Fターム[5F004EA03]の内容

半導体のドライエッチング (64,834) | パターン形成手法 (4,711) | マスク構成 (1,627) | レジスト以外のエッチングマスク (1,380)

Fターム[5F004EA03]の下位に属するFターム

Fターム[5F004EA03]に分類される特許

101 - 120 / 430

パターン形成方法、パターン形成体

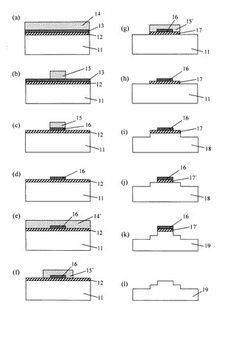

【課題】複数の段差を備えた微細な3次元構造パターンの形成に好適なパターン形成方法及びパターン形成体を提供する。

【解決手段】基板上に第1層目のハードマスク層を形成し、基板上の第1層目のハードマスク層を備えた面に、順に、第2層目から第N層目までのハードマスク層を形成し、第N層目のハードマスク層のパターニング処理し、順に、第(N−1)層目から第1層目までのハードマスク層のパターニング処理し、パターニングされた第1層目から第N層目までのハードマスク層をエッチングマスクとして基板に第1段目の異方性エッチングしてパターニング処理することを特徴とするパターン形成方法。

(もっと読む)

電子デバイスを形成する方法

【課題】高密度レジストパターンの形成を可能にする。

【解決手段】この方法は、(a)パターン形成される1以上の層を含む半導体基体を提供し;(b)パターン形成される1以上の層上に、第1の感光性組成物の第1の層を適用し;(c)第1のフォトマスクを通した活性化放射線に第1の層を露光し;(d)露光された第1の層を現像してレジストパターンを形成し;(e)ハードベークプロセスにおいてレジストパターンを熱処理し;(f)ハードベークされたレジストパターンを、当該レジストパターンの表面をアルカリ性にするのに有効な物質で処理し;(g)樹脂成分と光酸発生剤とを含む第2の感光性組成物の第2の層を、処理されたレジストパターンおよびパターン形成される1以上の層の上に適用し;(h)第2の層を活性化放射線に露光し;並びに、(i)露光された第2の層を現像し、現像後に第2の層の一部分を残す;ことを含む。

(もっと読む)

集積回路装置の製造方法

【課題】

エッチングフェンスを発生させずに集積回路装置を製造すること。

【解決手段】 第1のマスクと、前記第1のマスクより異方性エッチングに対する耐性が高く且つ所定の形状を有する第2のマスクとを積層したエッチングマスクを、被エッチング層の上に形成する第1の工程と、前記エッチングマスク及び前記被エッチング層に前記異方性エッチングを施して、前記被エッチング層を、前記第2のマスクに対応した形状にエッチングする第2の工程とを有し、前記第2の工程において、前記異方性エッチングにより前記第2のマスクを、垂直方向及び水平方向にエッチングしながら、前記被エッチング層をエッチングすること。

(もっと読む)

半導体装置の製造方法

【課題】成膜性及びエッチング耐性に優れる膜を形成し、微細加工技術に適する半導体装置の製造方法を提供する。

【解決手段】ウエハ18上にSiN膜2を形成する工程と、前記SiN膜2上にハードマスク膜を形成する工程と、前記ハードマスク膜をエッチングマスクとして前記SiN膜2をエッチングする工程と、を有し、前記ハードマスク膜は、窒化アルミニウム膜(AlN膜7)または窒化アルミニウムシリコン膜のうち少なくともいずれかを含むことを特徴とする。

(もっと読む)

エッチング処理装置

【課題】 フォトマスクパターンを形成する場合と比較し、処理工程が少なく且つ設備コストも低廉なエッチング処理装置を提案する。

【解決手段】被処理物Wに着脱自在であり、当該被処理物Wに装着された状態にて当該被処理物Wの被処理面Waの所定領域を被覆し、当該所定領域における前記処理液又は処理ガスの接触を遮断する被覆手段14を備える。

(もっと読む)

酸エッチング耐性、保護コーティング

本発明は、新規な組成物と、これらの組成物を、半導体およびMEMSデバイスの製造中に保護層として用いる方法とを提供する。この組成物は、溶媒系中に分散または溶解したシクロオレフィン共重合体を含有し、酸エッチングおよびその他の処理および取扱い中に、基板を保護する層を形成するために用いることができる。保護層は、感光性であっても非感光性であってもよく、保護層の下に、プライマー層を用いても用いなくてもよい。好ましいプライマー層は溶媒系中に塩基性ポリマーを含む。 (もっと読む)

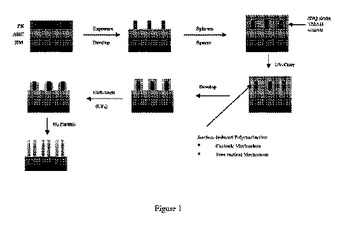

ダブルパターニング方法及び材料

シルセスキオキサン樹脂をパターン形成フォトレジストの上に塗布し、硬化して、パターン表面上に硬化シルセスキオキサン樹脂を生成する。次に未硬化シルセスキオキサン樹脂を除去し、パターン表面上に硬化シルセスキオキサン樹脂を残す。水平表面上の硬化シルセスキオキサン樹脂を除去し、下にあるフォトレジストを露光する。このフォトレジストを除去し、硬化シルセスキオキサンのパターンを残す。任意で、新規パターンを下層へ転写することができる。  (もっと読む)

(もっと読む)

基板処理方法及び記憶媒体

【課題】OR搬送処理を行った場合にも、全てのウエハの処理後の物性値を測定することなく、各ウエハに対して最適処理を施すことができる基板処理方法を提供する。

【解決手段】チャンバと、測定器とを備えた基板処理装置を用いてOR搬送処理によって複数のウエハWに対してシュリンク処理を連続して施す基板処理方法であって、処理前のウエハWのCD値を測定する処理前測定ステップと、得られたCD値に基づいて作成された処理条件に従ってFF制御によってウエハWにシュリンク処理を施す処理ステップと、処理後のウエハWのCD値を測定する処理後測定ステップと、処理後のCD値と目標値との差に基づいてFF制御における処理条件作成用のオフセット値を更新するオフセット値更新ステップとを有し、チャンバにおける経過処理時間が予め決められた所定値に到達するまで処理後測定ステップ及びオフセット値更新ステップを省略する。

(もっと読む)

半導体装置

【課題】キャパシタを構成する下部電極の自立安定性が十分に高められる半導体装置を提供する。

【解決手段】キャパシタ下地層2上に、キャパシタを構成する筒状の下部電極10と、下部電極10の外壁部に、外壁部から延在して形成されたフィン17とサポート膜6を有する。フィン17は下部電極10の長手方向一部にだけ形成されている。さらに、フィン17を含む下部電極10の上端はサポート膜6に接続されており、サポート膜6からの下部電極10の剥がれが防止される。フィン17を含む下部電極10上に、容量膜、上部電極、容量プレートの埋込みサポート膜、および容量プレートを成膜する。フィン17とサポート膜6とを接続させることにより、サポート膜6と下部電極10の接続面積を増大させることができる。

(もっと読む)

ナノ/微小球リソグラフィによって製造されるナノ/マイクロワイヤ太陽電池

【課題】 ナノ/微小球リソグラフィによって製造されるナノ/マイクロワイヤ太陽電池を提供する。

【解決手段】 ナノワイヤ/マイクロワイヤ・ベースの太陽電池を製造する技術が提供される。一実施形態において、太陽電池を製造する方法が提供される。本方法は、以下のステップを含む。ドープ基板を準備する。基板の上に球の単層を堆積させる。球は、ナノ球、微小球、又はそれらの組み合わせを含む。球をトリミングして単層内の個々の球の間に空間を設ける。トリミングされた球をマスクとして用いて、基板内にワイヤをパターン形成する。ワイヤは、ナノワイヤ、マイクロワイヤ、又はそれらの組み合わせを含む。ドープ・エミッタ層をパターン形成されたワイヤ上に形成する。上部コンタクト電極をエミッタ層の上に堆積させる。底部コンタクト電極を基板のワイヤとは反対の側に堆積させる。

(もっと読む)

基板処理方法

【課題】半導体デバイスの小型化要求を満たす寸法の開口部をマスク層又は中間層に形成することができる制御性に優れた基板処理方法を提供する。

【解決手段】アモルファスカーボン膜51、SiON膜52,BARC膜53及びフォトレジスト膜54が順に積層されたウエハWを処理する基板処理方法であって、CHF3ガスと、CF3Iガスと、H2ガス及びN2ガスの混合ガスから生成されたプラズマによって、フォトレジスト膜54の開口部55のCD値を縮小しつつ開口部底部のSiON膜をエッチングするシュリンクエッチングステップと、開口部55の側壁面へのデポの堆積を促進させて各CD値のばらつきを吸収するばらつき吸収ステップと、開口部の内面に薄膜を形成して各開口部の開口幅を縮小させる開口幅縮小ステップとを1ステップで行う。

(もっと読む)

半導体装置の製造方法

【課題】側壁転写加工技術を用いる場合に、転写用のマスクが非対称な形状となることに起因した不具合を極力防止する

【解決手段】半導体基板1上に、ゲート電極を形成するための膜を積層形成する。第1膜としてシリコン窒化膜8a、第2膜としてシリコン酸化膜9aを積層形成する。シリコン酸化膜9aを加工して芯材パターン9を形成する。ウェット処理によりシリコン窒化膜8aを選択的エッチングして、所定深さまで除去すると共に、芯材パターン9の直下に括れ部8bを形成する。非晶質シリコン膜11aを形成し、エッチバックによりスペーサパターン11を形成する。芯材パターン9をエッチングにより除去すると独立したスペーサパターン11を得ることができ、これをマスクとしてシリコン窒化膜8aをRIEエッチング加工しマスクパターン8を形成する。イオンが斜入しても芯材パターン9の直下部分が偏ったエッチング状態とならない。

(もっと読む)

被エッチング材のプラズマエッチング方法

【課題】高アスペクト比の深孔加工において、被エッチング材の開口におけるボーイングを抑制しつつ、高アスペクト比部での開口不足を解消する。

【解決手段】プラズマエッチング装置により被エッチング材上にパターニングされて形成されたマスクを用いて前記被エッチング材をエッチング処理する被エッチング材のプラズマエッチング方法において、フルオロカーボンガスCxFy(x=1、2、3、4、5、6、y=4、5、6、8)を用いて前記マスクのマスクパターンの表面に近い開口側壁に堆積物を付着させながら被エッチング材をエッチングする高堆積性の第1のステップと、フルオロカーボンガスを用いて前記マスクのマスクパターンの表面に近い開口側壁に付着させた堆積物を削りながら被エッチング材をエッチングする低堆積性の第2のステップと、を順次行う。

(もっと読む)

プラズマ処理方法

【課題】有機膜および無機膜を備えた積層膜の各膜に対して均一に一貫処理を施す。

【解決手段】処理ガスを供給するガス供給管を備えた真空容器1と、該真空容器内に配置された基板電極3と、前記真空容器内で前記基板電極に対向して配置されたアンテナ電極7と、前記基板電極とアンテナ電極間の距離を処理雰囲気中で変更可能な電極間距離調整手段を備え、前記アンテナ電極に高周波エネルギを供給して供給された処理ガスに高周波エネルギを供給してプラズマを生成し、前記基板電極にイオン引き込み用高周波電圧を供給して、生成された前記プラズマ中のイオンを加速して前記基板電極上に載置した試料にプラズマ処理を施すプラズマ処理方法において、前記試料は有機膜と無機膜を積層した構造を備える絶縁膜構造を具備し、前記有機膜をエッチングするときは、前記無機膜をエッチングするときよりも前記電極間距離を大きく設定する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】ビアと配線の間に位置ずれが生じても、エアギャップとビアが繋がることを抑制できるようにする。

【解決手段】配線162は第1絶縁層120に埋め込まれており、上面が第1絶縁層120の上面より高い。エアギャップ128は、配線162と第1絶縁層120の間に位置している。第2絶縁層200は、少なくとも第1絶縁層120上及びエアギャップ128上に形成されている。本図に示す例では、第2絶縁層200は配線162を被覆していない。エッチングストッパー膜210は、少なくとも第2絶縁層200上に形成されている。本図に示す例では、エッチングストッパー膜210は、第2絶縁層200上及び配線162上に形成されている。第3絶縁層220はエッチングストッパー膜210上に形成されている。ビア262は第3絶縁層220に埋め込まれており、配線162に接続している。

(もっと読む)

薄膜トランジスタの製造方法及び表示装置の製造方法

【課題】レジスト組成物を用いたマスクパターンを用いることなくTFT及びそれを用いた表示装置を製造することを目的とする。

【解決手段】ロールツーロール方式により加工処理を行う表示装置の製造方法であって、組成物の吐出口が一軸方向に複数個配列した第1の液滴吐出手段により、可撓性を有する基板上に開口部を有する絶縁性樹脂膜を形成し、組成物の吐出口が一軸方向に複数個配列した第2の液滴吐出手段により、開口部にゲート電極を形成し、プラズマの噴出口が一軸方向に複数個配列したノズル体を備えた被膜形成手段により、ゲート電極および絶縁性樹脂膜上にゲート絶縁膜を形成する。

(もっと読む)

基板の加工方法および半導体チップの製造方法ならびに樹脂接着層付き半導体チップの製造方法

【課題】プラズマ処理を用いたエッチングのためのマスクを低コストで形成することができる基板の加工方法および半導体チップの製造方法を提供する。

【解決手段】半導体ウェハ1をプラズマ処理を用いたエッチングによって個片の半導体チップ1eに分割するプラズマダイシング用のマスク形成において、半導体ウェハ1の裏面1bにおいてスクライブライン1cおよび外縁に沿って所定幅で設定された輪郭部に撥液性の液体を印刷して撥液膜3,3eより成る撥液パターンを形成し、裏面1bに液状の樹脂を供給して撥液膜3の存在しない領域にこの撥液膜3の厚みよりも厚い膜厚の樹脂膜4を形成し、さらにこの樹脂膜4を硬化させてエッチングにおいて除去される領域以外を覆うマスク4*を形成する方法を採用する。これによりフォトリソグラフィ法などの高コストの方法を用いることなく、エッチングのためのマスクを低コストで形成することができる。

(もっと読む)

半導体装置の製造方法

【課題】プラズマ雰囲気の周囲に存在する銅による影響を抑制する半導体装置の製造方法を提供する。

【解決手段】半導体基板1の上方に絶縁膜18〜21を形成する工程と、絶縁膜18〜21上にレジスト膜24を形成する工程と、レジスト膜24の上方にマスク膜25を形成する工程と、マスク膜25の上方にレジストパターン27を形成する工程と、レジストパターン27をマスクにしてマスク膜25をエッチングする工程と、酸素ガスとハイドロフロロカーボンガスの混合ガスを導入し、30mTorr以上の圧力の雰囲気内で、マスク膜25から露出する領域のレジスト膜24をエッチングする工程とを有する。

(もっと読む)

ビア構造とそれを形成するビアエッチングプロセス

【課題】ビア構造とそれを形成するビアエッチングプロセスを提供する。

【解決手段】ビアエッチングプロセスは、丸角とテーパ型側壁プロファイルを有するスルーサブストレートビアを形成する。その方法は、半導体基板を提供するステップと、半導体基板上に、ハードマスク層とパターン化フォトレジスト層を形成するステップと、ハードマスク中に開口を形成して、半導体基板の一部を露出するステップと、パターン化されたフォトレジスト層とハードマスク層をマスキング要素として、半導体基板の少なくとも一部を通過するビアを形成するステップと、トリミングプロセスを実行して、ビアの頂角を丸くするステップと、フォトレジスト層を除去するステップと、からなる。

(もっと読む)

金属触媒を用いたポリシリコンマスクの製造方法及び該マスクを用いた半導体素子の製造方法

【課題】金属触媒を用いたポリシリコンマスクの製造方法及びこれを用いた半導体素子の製造方法を提供すること。

【解決手段】本発明に係る金属触媒を用いたポリシリコンマスクの製造方法は、基板10を提供するステップと、基板10上に所定のパターンを有する非晶質シリコン層30を形成するステップと、非晶質シリコン層30上に金属触媒層40を形成するステップと、非晶質シリコン層30を熱処理してポリシリコンマスク31を形成するステップとを含むことを特徴とする。  (もっと読む)

(もっと読む)

101 - 120 / 430

[ Back to top ]