Fターム[5F004EA37]の内容

半導体のドライエッチング (64,834) | パターン形成手法 (4,711) | エッチング形状の制御 (314)

Fターム[5F004EA37]に分類される特許

41 - 60 / 314

エッチング方法、エッチングシステムおよびエッチング装置

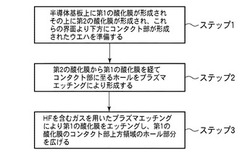

【課題】シリコン酸化膜にコンタクト部に到達する高アスペクト比のホールを形成する際に、ホール内のコンタクト材料とコンタクト部との間で十分なコンタクトがとれるようなホールを形成すること。

【解決手段】基板上にBおよびPの少なくとも一方を含むシリコン酸化物からなる第1の酸化膜と、その上に形成された、BおよびPを含まないシリコン酸化物からなる第2の酸化膜とを有し、さらに第1の酸化膜および第2の酸化膜の界面より下方に形成されたコンタクト部を有する被処理体を準備し(ステップ1)、第2の酸化膜と前記第1の酸化膜をエッチングしてコンタクト部に到達するホールを形成し(ステップ2)、HFガスおよび不活性ガスを用いたドライプロセスにより第1の酸化膜をエッチングし、第1の酸化膜のコンタクト部上方領域のホール部分を広げる(ステップ3)。

(もっと読む)

プラズマ処理装置及び光学モニタ装置

【課題】平板スロットアンテナの電磁波放射特性の均一性に影響を与えずに波長領域の広いモニタ光を用いて処理容器内の被処理基板の表面に対する光学的なモニタリングを高精度に行う。

【解決手段】このマイクロ波プラズマエッチング装置における光学モニタ装置100は、サセプタ12上に載置される半導体ウエハWのエッジよりも半径方向内側にあって、かつ同軸管66よりも半径方向外側の位置で、冷却ジャケット板72の上に配置されるモニタヘッド102と、このモニタヘッド102から鉛直下方にカバープレート72、誘電体板56、スロット板54および誘電体窓52を縦断して設けられるモニタリング用の光導波路104と、光ファイバ106を介してモニタヘッド102と光学的に結合されるモニタ本体108とを有している。

(もっと読む)

半導体装置とその作製方法

【課題】特性が良好なトランジスタを提供する。

【解決手段】例えば、ボトムゲート・ボトムコンタクト構造のトランジスタを作製するに際して、ソースとドレインを構成する導電層を3層の積層構造とし、2段階のエッチングを行う。すなわち、第1のエッチング工程には、少なくとも第2の膜及び第3の膜に対するエッチングレートが高いエッチング方法を採用し、第1のエッチング工程は少なくとも第1の膜を露出するまで行う。第2のエッチング工程には、第1の膜に対するエッチングレートが第1のエッチング工程よりも高く、「第1の膜の下に接して設けられている層」に対するエッチングレートが第1のエッチング工程よりも低いエッチング方法を採用する。第2のエッチング工程後にレジストマスクをレジスト剥離液により剥離するに際し、第2の膜の側壁が少し削られる。

(もっと読む)

半導体装置の製造方法

【課題】エッチングレートを上昇でき、生産性を向上できる半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、半導体基板上に交互に積層されたシリコン層とシリコン酸化膜とを備える多層膜に対して、一括してエッチングを行う工程を含み、前記エッチングの際のエッチングガスは、少なくとも2種類以上の第7族元素と、第3族元素,第4族元素,第5族元素,または第6族元素とを含有し、前記エッチング工程の際の前記半導体基板に入射するイオンのエネルギーは、100eV以上であり、前記第7族元素に対する、前記第3族乃至前記7族元素の添加比率は、0.5以上3.0以下である。

(もっと読む)

プラズマ処理装置

【課題】エッチングレートあるいは所望の加工形状をウエハ面内で均一に得ることのできるプラズマ処理装置を提供する。

【解決手段】真空処理容器内に処理ガスを供給するガス供給装置113と、前記真空処理容器内に試料を載置して保持する載置電極115と、前記載置電極に高周波バイアス電圧を供給する高周波バイアス電源117と、前記真空処理容器内を排気する排気装置と、前記真空処理容器内に磁界を形成する電磁コイル107,108,109と、前記真空処理容器に高周波エネルギーを供給して、前記磁界との相互作用によりプラズマを生成するプラズマ生成装置101とを備え、前記高周波バイアス電源は2MHz以上の高周波であり、前記載置電極上の前記真空処理容器のプラズマ生成領域に対向する面に形成されたアース領域の高さ以下の領域の磁束密度は20mT以下である。

(もっと読む)

半導体素子のパターン形成方法

【課題】互いに異なる幅のパターンを同一層で形成するにあたり、パターン間の間隔の均一度を改善することができる半導体素子のパターン形成方法を提供する。

【解決手段】セル領域及びセレクトトランジスタ領域を含む下部膜上に補助膜を形成する段階と、前記セレクトトランジスタ領域の前記補助膜上部に第1保護膜を形成する段階と、前記セレクトトランジスタ領域の前記第1保護膜上部には、前記第1保護膜の幅より狭い第1フォトレジストパターンが、前記セル領域の前記補助膜上部には前記第1フォトレジストパターンの幅より狭い第2フォトレジストパターンが形成され、前記第1及び第2フォトレジストパターン間の間隔を前記第2フォトレジストパターン間の間隔と同一に形成する段階と、を含む。

(もっと読む)

エッチング方法

【課題】エッチングの異方性と、エッチングレートとを高めることができるエッチング方法を提供する。

【解決手段】

エッチング方法では、接地された真空槽11内に処理対象物である基板Sを搬入する以前に、真空槽11に供給される成膜ガスを下部電極13への高周波電力の供給によってプラズマ化して、該真空槽11の内壁11bに絶縁膜Iを形成する絶縁膜形成工程を実施する。その後、真空槽11内に供給されるエッチングガスを真空槽11内に配設された下部電極13への高周波電力の供給によってプラズマ化して真空槽11内に搬入された基板Sを該プラズマによってエッチングするエッチング工程を実施する。

(もっと読む)

半導体装置の製造方法

【目的】マスクの厚さを所定の値にし、後退量とエッチング量の比を所定の値にしてトレンチの開口部の端部を丸めることで、ゲート酸化膜形成温度を950℃未満の低い処理温度にした場合でもゲート酸化膜の良好な耐圧特性と長期信頼性が得られる半導体装置の製造方法を提供すること。

【解決手段】マスクであるシリコン酸化膜2の端部10をトレンチ8の開口部9の端部Aから後退させる量Xと、等方性ドライエッチングによるエッチング量Yとの比(X/Y)を2以上5以下に設定することで、Qbdの値を高くすることができて、良好なトレンチ8の開口部9の端部Aと段差12の端部Bの形状を丸めることができる。その結果、その後形成するゲート酸化膜14の熱処理温度を、950℃未満、あるいは、900℃以下で行った場合でも、ゲート酸化14の良好な耐圧特性と長期信頼性を得ることが可能となる。

(もっと読む)

半導体装置及びその製造方法

【課題】D−RAMのキャパシタを形成するシリンダのドライエッチ加工において、従来技術の製造方法ではアスペクト比が高いシリンダやコンタクトの形状がボーイング形状となり隣接するホール間ショートの問題やホール内に形成する電極成膜のカバレッジ異常などの問題が発生する。

【解決手段】本発明ではシリコン酸化膜4aにコンタクトホールを形成する際にボーイングが発生する部分にLow−k膜の炭化シリコン酸化膜5を挿入して積層構造とし、ドライエッチでシリコン酸化膜4aのエッチング速度に対し、炭化シリコン酸化膜5のエッチング速度が1/5〜1/10と遅い条件にすることでボーイング形状の抑制を可能にした。

(もっと読む)

半導体装置

【課題】シリコン基板裏面をソース電極として使用するLDMOSFETにおいて、出力効率向上のため、基板抵抗を下げようとして高濃度ボロンドープ基板を用いると、ソースドレイン間のリーク不良が、多発することが、本願発明者等によって明らかにされた。更に、この不良解析の結果、ソース不純物ドープ領域からP型エピタキシ層を貫通してP型基板に至るP型ポリシリコンプラグに起因する不所望な応力が、このリーク不良の原因であることが明らかにされた。

【解決手段】本願発明は、LDMOSFETを含む半導体装置であって、LDMOSFETのソース不純物ドープ領域の近傍の上面から下方に向けてエピタキシ層内をシリコン基板の近傍まで延び、前記エピタキシ層内にその下端があるシリコンを主要な成分とする導電プラグを有する。

(もっと読む)

エッチング方法及び装置

【課題】マスク選択比を大きくでき、異方性に優れ、深くエッチングすることのできるエッチング方法及び装置を提供する。

【解決手段】エッチング装置は、真空チャンバ1内に設けた基板電極6に対向して電位的に浮遊状態に維持された浮遊電極を設け、この浮遊電極の基板電極に対向した側に、エッチング保護膜を形成する材料13を設け、浮遊電極に高周波電力を間欠的に印加させる制御手段14を設けて構成される。エッチング方法は、基板電極に対向して設けた浮遊電極の基板電極に対向した側に設けた、エッチング保護膜を形成する材料をターゲット材として用い、主ガスとして希ガスのみを用い、浮遊電極に高周波電力を印加して基板上にスパッタ膜を形成し、その後、浮遊電極への高周波電力の印加を止め、真空チャンバにエッチングガスを導入して基板をエッチングし、基板上におけるスパッタ膜の形成とエッチングとを予定のシーケンスで繰り返すように構成される。

(もっと読む)

薄膜のパターニング方法及び表示パネルの製造方法

【課題】コンタクトホールをより微細に形成することができる薄膜のパターニング方法及び表示パネルの製造方法を提供する。

【解決手段】所定の段差部を有した絶縁層25を形成する工程と、スパッタ法により前記段差部を覆うようにして前記絶縁層25上に犠牲層28を成膜する工程と、前記段差部に対応する領域における前記犠牲層28のうちの少なくとも一部の除去と、前記除去により前記犠牲層28から露出された領域における前記絶縁層25の除去とを、ドライエッチングにより連続して行う工程と、前記ドライエッチングで残存した前記犠牲層28の少なくとも一部をウェットエッチングにより除去する工程と、を有する。

(もっと読む)

デュアルドープゲートの用途におけるプロフィル制御とN/Pローディングを改善する方法

【課題】プラズマエッチングチャンバ内でデュアルドープゲート構造をエッチングするための方法を提供する。

【解決手段】エッチングされるポリシリコンフィルムを保護するパターンを設ける工程、次いで、プラズマが点火され、保護されていないポリシリコンフィルムのほぼすべてがエッチングされる。次いで、シリコン含有ガスを導入しつつポリシリコンフィルムの残りをエッチングする。また、エッチング処理中にシリコン含有ガスを導入するよう構成されたエッチングチャンバ。

(もっと読む)

周期的な酸化およびエッチングのための装置と方法

ミストエッチング装置及びミストエッチング方法

【課題】 エッチング処理が困難な材料に対しても適用可能であり、サイドエッチングを抑制し、且つエッチング処理面が平滑である良好なパターン形状を得ることができるミストエッチング装置及びミストエッチング方法を提供すること。

【解決手段】 エッチング液をミスト化するミスト生成部と、エッチング対象物をエッチングするエッチング部とを備えており、前記ミスト生成部は、エッチング液が収容され且つミスト化されるミスト生成容器と、前記エッチング液をミスト化するミスト生成機構と、生成された前記ミストを前記ミスト生成容器外へ排出するミスト排出口とからなり、前記エッチング部には、前記ミストが導入されるミスト導入口と前記エッチング対象物とが備えられ、該エッチング部で前記ミストが蒸気化されることを特徴とするミストエッチング装置とする。

(もっと読む)

微細加工方法

【課題】より安価に超微細な加工が可能な微細加工方法を提供する。

【解決手段】

基板の微細加工方法は、薄膜形成過程と、V字溝形成過程と、薄膜エッチング過程と、基板エッチング過程と、薄膜除去過程と、からなる。薄膜形成過程は、基板1よりも軟性を有し、基板1に対して選択エッチングが可能であり、且つ可塑性を有する薄膜2を基板1上に形成する。V字溝形成過程は、薄膜2よりも硬性を有する少なくとも断面がV字形状のV字工具4を薄膜に押圧させ、基板1まで達さない少なくとも断面がV字形状のV字溝3を薄膜2に形成する。薄膜エッチング過程は、V字溝3の先端が開孔して基板1が露出するように薄膜2をエッチングする。基板エッチング過程は、薄膜2をマスクとして基板1をエッチングする。薄膜除去過程は、基板1上から薄膜2を除去する。

(もっと読む)

半導体の異方性エッチングプロセス

II−VI及びIII−V半導体などの半導体材料を異方的にエッチングする方法が提供される。本方法は、エッチングマスクを通した非反応性ガスによる半導体材料のプラズマスパッタエッチングと、その後に続く、ポリマーフォーマーを使用したプラズマ重合による側壁の不動態化の繰り返しサイクルを含む。この手順を用いて、下方変換発光ダイオードデバイスの微細な画素を作製することができる。 (もっと読む)

貫通孔形成方法

【課題】プラズマエッチングにより基板に貫通孔を形成する方法を提供すること。

【解決手段】基板上にマスクパターンを形成し、バイアス電力500〜1000Wの条件で、プラズマエッチングによりホール又はトレンチを形成する際に、ホール又はトレンチの底部周囲にマイクロトレンチを形成し、基板に貫通孔を形成する。

(もっと読む)

半導体素子の製造方法及び半導体素子

【課題】p型半導体領域、n型半導体領域を有する半導体基板から成る半導体素子のpn接合部における耐圧性の向上を可能にする。

【解決手段】本発明の半導体素子の製造方法では、p型半導体領域、n型半導体領域を有する半導体基板から半導体素子を形成する。本発明の製造方法では、プラズマ処理装置1を用いて前記半導体基板の表面をプラズマエッチングすることによって前記半導体素子を取り囲む溝を形成する。そして、プラズマ条件を適宜に設定することにより、溝の内側壁のうちp型半導体領域とn型半導体領域の境界部分に横穴状の溝を形成する。この結果、形成される半導体素子は、側壁のうちp型半導体領域とn型半導体領域の境界部分に横穴構造を有することになり、pn接合部における耐圧性が向上する。

(もっと読む)

太陽電池の製造方法

【課題】高い光閉じ込め効果を有する太陽電池を、簡単にかつ安価に製造する。

【解決手段】太陽電池は、基板上(1)に背面電極層(2)を形成するステップと、背面電極層(2)上に光電変換層(3)を形成するステップと、光電変換層(3)の上面に複数の開口(5)を有するパターン膜を形成するステップと、このパターン膜を介して異方性エッチングを行い、開口(5)下の光電変換層(3)に縦長の第1の孔部(5a)を形成するステップと、第1の孔部(5a)の形成後に、パターン膜を介して等方性エッチングを行って、第1の孔部(5a)下方に、最大幅が第1の孔部(5a)の開口幅よりも大きい湾曲した側面を有する第2の孔部(5b)を形成するステップと、パターン膜を除去して光電変換層(3)上に透明導電被膜(4)を形成するとともに第1、第2の孔部中に透明導電被膜を埋め込むステップとによって製造される。

(もっと読む)

41 - 60 / 314

[ Back to top ]