Fターム[5F032DA34]の内容

Fターム[5F032DA34]に分類される特許

1 - 20 / 217

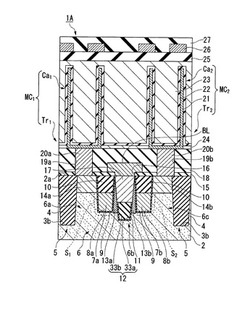

半導体装置及びその製造方法、並びにデータ処理システム

【課題】トランジスタのオン電流を十分に確保することが可能な信頼性の高い半導体装置を提供する。

【解決手段】活性領域6を分断する2つの埋め込みゲート用の溝部8a,8bにゲート絶縁膜9を介して埋め込まれたゲート電極7a,7bと、2つの埋め込みゲート用の溝部8a,8bによって分断された3つの活性領域6a,6b,6cのうち、中央部に位置する活性領域6bを分断するビットコンタクト用の溝部11の両側面に、埋め込みゲート用の溝部8a,8bの底面と同程度の深さで不純物を拡散させることによって形成された第1の不純物拡散層13a,13bと、中央部を挟んだ両側に位置する活性領域6a,6cに、ゲート電極7a,7bの上面と同程度の深さで不純物を拡散させることによって形成された第2の不純物拡散層14a,14bとを備える。

(もっと読む)

半導体装置の製造方法

【課題】FinFETの特性が均一な半導体装置の製造方法を提供する。

【解決手段】実施形態に係る半導体装置の製造方法は、半導体基板の上層部分に凹部を形成する工程と、前記凹部内に犠牲材を配置する工程と、前記半導体基板及び前記犠牲材を選択的に除去することにより、一方向に延び、周期的に配列された複数本のフィンを形成する工程と、前記フィン間の空間の下部に素子分離絶縁膜を形成する工程と、前記犠牲材を除去する工程と、前記フィンの露出面上にゲート絶縁膜を形成する工程と、前記素子分離絶縁膜上に、前記フィンを跨ぐように、前記一方向に対して交差した方向に延びるゲート電極を形成する工程と、を備える。

(もっと読む)

半導体装置の製造方法

【課題】SOI基板を使用せずバルク基板を用いてフィン型FETを製造すると、従来技術では素子領域と半導体基板との間の絶縁耐圧が低くなっていた。

【解決手段】本発明の半導体装置の製造方法では、素子分離膜の形成時にマスクとして用いる耐酸化用膜を、半導体基板表面に設ける溝部の底部から所定の距離まで離間した部分を除いて立設部の表面に形成することで、立設部の下部の素子分離膜がほぼ一定の膜厚にすることができた。このため、立設部と半導体基板との間の絶縁耐圧が向上し、リークもなく、信頼性が向上した。

(もっと読む)

半導体装置、及び半導体装置の製造方法

【課題】ランプアニールによるレイアウトに起因した温度バラつきを低減する。

【解決手段】この半導体装置10は、基板100と、基板100に埋め込まれた素子分離領域200と、基板100のうち、素子分離領域200の無い領域に形成された不純物層(エクステンション領域322、ソース領域324、エクステンション領域342、及びドレイン領域344)と、を備える。この素子分離領域200は、たとえば、波長300nm以上890nm以下においてSiO2よりも光吸収係数が大きい材料から形成されている光吸収層220を含む。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の信頼性を向上させ、半導体装置の製造歩留まりを向上させる。

【解決手段】半導体基板1の主面に酸化膜として絶縁膜2を形成し、絶縁膜2上に窒化シリコン膜を形成してから、素子分離用の溝4aをプラズマドライエッチングにより形成し、溝4aを埋めるように酸化シリコンからなる絶縁膜6をHDP−CVD法で形成し、CMP処理により溝4aの外部の絶縁膜6を除去し、溝4a内に絶縁膜6を残す。それから、窒化シリコン膜を除去する。その後、絶縁膜2をウェットエッチングで除去して半導体基板1を露出させるが、この際、半導体基板1の主面に140ルクス以上の光を当てながら絶縁膜2をウェットエッチングする。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】STIの形成によるウェル拡散層の不純物濃度の変化を抑制し、かつ、ウェル拡散層のドーズロスを抑制した半導体記憶装置およびその製造方法を提供する。

【解決手段】半導体記憶装置は、半導体基板を備える。メモリセル領域には、複数のメモリセルが半導体基板上に形成されている。周辺回路領域には、複数のメモリ素子を制御する複数の半導体素子が形成されている。素子分離領域は、複数のメモリセル間を分離し、あるいは、複数の半導体素子間を分離する。周辺回路領域において半導体素子が形成されているアクティブエリアの不純物濃度は、半導体基板の表面に対して水平方向に素子分離領域の側面からアクティブエリアの内部へ向かって低下している。

(もっと読む)

半導体装置

【課題】耐圧の向上が図られる半導体装置を提供する。

【解決手段】n-型半導体領域には、ドレイン領域となるn-型の拡散領域が形成されている。n-型の拡散領域の周囲を取囲むようにp型の拡散領域が形成されている。p型の拡散領域には、ソース領域となるn+型の拡散領域が形成されている。n-型の拡散領域の直下には、p-型の埋め込み層13が形成されている。n-型の半導体領域の領域には、高電位が印加されるn+型の拡散領域が形成され、そのn+型の拡散領域の表面上には電極が形成されている。電極とドレイン電極とは、配線20によって電気的に接続されている。配線20の直下に位置する部分に、p-埋め込み層13に達するトレンチ3aが形成されて、ポリシリコン膜81が形成されている。

(もっと読む)

半導体装置およびその製造方法

【課題】ワードライン間の素子分離を行い、メモリセルの微細化が可能な半導体装置およびその製造方法を提供する。

【解決手段】半導体基板10内に形成されたビットライン14と、ビットライン14上にビットライン14の長手方向に連続して設けられた絶縁膜ライン18と、ビットライン14間の半導体基板10上に設けられたゲート電極16と、ゲート電極16上に接して設けられ、ビットライン14の幅方向に延在したワードライン20と、ビットライン14間でありワードライン20間の半導体基板に形成されたトレンチ部22と、を具備する。

(もっと読む)

半導体装置およびその製造方法

【課題】第1のトランジスタと第2のトランジスタが、ぞれぞれのドレイン領域とソース領域を共有して同一の半導体基板上に形成される構成の半導体装置の製造において、それぞれのトランジスタのソース領域およびドレイン領域の直下に埋め込み絶縁膜を効率的に形成できる製造方法を提供する。

【解決手段】半導体基板上にそれぞれのトランジスタのソース領域およびドレイン領域に対応してトレンチを形成し、前記トレンチをSiGe混晶層と半導体層を順次形成することにより充填し、さらに第1のトランジスタのソース領域および第2のトランジスタのドレイン領域直下のSiGe混晶層を、素子分離溝を介して選択エッチングにより除去し、第1のトランジスタのドレイン領域および第2のトランジスタのソース領域として共有される拡散領域直下のSiGe混晶層を、前記拡散領域に形成した孔を介して選択エッチングし、除去する。

(もっと読む)

半導体装置及びその製造方法

【課題】製造プロセスが複雑になるといったことを防ぎつつ、n型及びp型MOSトランジスタについて両方の性能を向上させた半導体装置を提供する。

【解決手段】半導体基板1の面内に、n型MOSトランジスタと、p型MOSトランジスタとを備える半導体装置であって、n型MOS型トランジスタが形成される第1の拡散層2aの間を絶縁分離する第1の絶縁層3aと、p型MOS型トランジスタが形成される第2の拡散層2cの間を絶縁分離する第2の絶縁層3bとを備え、第1の絶縁層3aは、半導体基板1の表層に形成された第1の溝部4aに、シリコン窒化膜5と、このシリコン窒化膜5の上にシリコン酸化膜6とを埋め込むことによって形成され、第2の絶縁層3bは、半導体基板1の表層に第1の溝部4aよりも幅広となるように形成された第2の溝部4bに、シリコン酸化膜6を埋め込むことによって形成されている。

(もっと読む)

半導体装置及びその作製方法

【課題】酸化物半導体を用いるトランジスタにおいて、電気的特性の良好なトランジスタ及びその作製方法を提供することを課題の一とする。

【解決手段】基板上に酸化物半導体膜及び絶縁膜を有し、酸化物半導体膜の端部は絶縁膜と接しており、酸化物半導体膜は、チャネル形成領域と、チャネル形成領域を挟んで形成されたドーパントを含む領域とを含み、酸化物半導体膜上に接して形成されたゲート絶縁膜と、ゲート絶縁膜上に形成され、サイドウォール絶縁膜を有するゲート電極と、サイドウォール絶縁膜、酸化物半導体膜、および絶縁膜に接して形成されたソース電極およびドレイン電極とを有する半導体装置である。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】隣接セル間干渉を抑制した不揮発性半導体記憶装置及びその製造方法を提供する。

【解決手段】実施形態によれば、第1メモリストリングと、ソースコンタクトと、第2メモリストリングと、シールド導電層と、を備えた不揮発性半導体記憶装置を提供する。第1メモリストリングは、第1軸に沿って並ぶ第1メモリセル及び第2メモリセルを含む。ソースコンタクトは、第1メモリストリングのソース側の端に設けられる。第2メモリストリングは、第1軸に対して直交する第2軸に沿って第1メモリセルと並ぶ第3メモリセルを含み、第1軸に沿って延在する。シールド導電層は、第1メモリストリングと第2メモリストリングとの間において第1軸に沿って延在し、ソースコンタクトと電気的に接続される。

(もっと読む)

二酸化ケイ素膜の製造方法

【課題】低収縮かつ低応力である絶縁膜を製造することができる方法の提供。

【解決手段】基板表面にポリシラザン組成物を塗布して塗膜を形成させ、引き続き前記塗膜を過酸化水素雰囲気下、50〜200℃で加熱することを含んでなることを特徴とする、二酸化ケイ素膜の製造方法。この二酸化ケイ素膜の製造方法によって各種絶縁膜などのアイソレーション構造を形成させることができる。

(もっと読む)

半導体装置の製造方法

【課題】塗布法を用いて形成される酸化膜を溝の内部に充填した溝型の素子分離部を有する半導体装置において、溝の内部におけるボイドの発生を抑制して、埋め込み不良を低減することのできる技術を提供する。

【解決手段】0.2μm以下の溝幅を有する溝4Sの内部に埋まるポリシラザン膜の上面がパッド絶縁膜3の上面よりも高く、かつ1.0μm以上の溝幅を有する溝4Lの内部に埋まるポリシラザン膜の上面がパッド絶縁膜3の上面よりも低くなるように、半導体基板1の主面上にポリシラザン膜を形成し、続いて、300℃以上の熱処理を行うことにより、ポリシラザン膜を酸化シリコン(SiO2)からなる第1埋め込み膜8へ転化すると同時に、溝4Sの上部に局所的に生じたボイドを消滅させる。

(もっと読む)

半導体装置

【課題】SOI−MISFETにおいて、多結晶シリコンの残存による電気的な短絡、ゲート電極の寄生容量の増大を防止する。逆狭チャネル効果の抑制。

【解決手段】シリコン膜13を有するSOI基板上にゲート絶縁膜14、第1の多結晶シリコン膜15、ストッパー窒化膜(16)を順次堆積する。シリコン膜13、第1の多結晶シリコン膜15の側面に逆テーパー面(テーパー角θが鈍角)が形成されるようにエッチングして素子分離溝を形成する。STI埋め込み絶縁膜17を堆積し、CMPにより平坦化した後、等速性のRIEによりストッパー窒化膜(16)と絶縁膜17をエッチングして平坦な表面を得、その上に第2の多結晶シリコン膜18を堆積し(e)、積層多結晶シリコン膜をエッチングして積層ゲート電極(15、18)を形成する(f)。以下、ソース・ドレイン領域21、シリサイド膜22、層間絶縁膜23及びメタル配線24等を形成する(g)。

(もっと読む)

半導体装置の製造方法

【課題】メモリセル領域とメモリセル領域の外周に周辺回路領域を有する半導体装置の製造において、セルフアラインダブルパターニングを用いてメモリセル領域の半導体基板に溝を形成する際、メモリセル領域端部において正常に溝が形成されないという問題がある。

【解決手段】メモリセル領域の第1のマスクパターンを幅W1、ピッチW3(但し、W3>2×W1)のラインパターンに形成し、その上に犠牲膜をW1の幅のギャップが残るように形成した後、塗布法で第2のマスクパターンとなる膜を形成し、犠牲膜と第2のマスクパターンとなる膜をエッチバックして第1のマスクパターン表面を露出させる。その後、第1及び第2のマスクパターン間の犠牲膜を選択的に除去し、溝パターンを形成する。周辺回路領域では、メモリセル領域との境界部を残して第1のマスクパターンを形成せず、境界部に形成される第1のマスクパターンの幅W2をW1の1〜4倍とする。

(もっと読む)

半導体装置の製造方法

【課題】MOSトランジスタの形成工程を利用して、トレンチアイソレーションを形成できるようにした半導体装置の製造方法を提供する。

【解決手段】シリコン基板1にDTI層20とMOSトランジスタとを有する半導体装置の製造方法であって、シリコン基板1に深いトレンチを形成し、トレンチが形成されたシリコン基板1に熱酸化を施して、PMOSトランジスタ50のゲート酸化膜13を形成すると同時に、トレンチの内側面にSiO2膜14を形成する。次に、トレンチを埋め込むようにシリコン基板1上にポリシリコン膜15を堆積し、このポリシリコン膜15をパターニングする。これにより、PMOSトランジスタ50のゲート電極17を形成すると同時に、トレンチ内にSiO2膜14とポリシリコン膜18とを含むDTI層20を形成する。

(もっと読む)

シャロートレンチアイソレーション膜のためのアミノシラン

【課題】記憶及び論理回路を含む半導体基材、例えば、1つ又は複数の集積回路構造をその上に有するシリコンウェハにおいて用いられるシャロートレンチアイソレーションのための高アスペクト比の特徴のギャップを充填するための酸化条件下で二酸化ケイ素含有膜をスピンオン堆積させる方法を提供する。

【解決手段】高アスペクト比の特徴を有する半導体基材を用意する工程、該半導体基材を低分子量のアミノシランを含む液体配合物と接触させる工程、該半導体基材上に該液体配合物を塗布することにより膜を形成する工程、及び該膜を酸化条件下において高温で加熱する工程を含む方法が提供される。この方法のための組成物もまた記載される。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、トランジスタを容易にOn(オン)させることが可能で、かつ良好なデータ保持特性を実現することの可能な半導体装置及びその製造方法を提供することを課題とする。

【解決手段】半導体基板12に形成され、第1の方向に延在する第1の素子分離用51、及び第1の素子分離用溝51を埋め込む第1の素子分離用絶縁膜53よりなり、複数の素子形成領域Rを有した活性領域16を区画する第1の素子分離領域14と、半導体基板12に、第1の方向と交差する第2の方向(Y方向)に延在するように形成され、第1の素子分離領域14の一部を分断する第2の素子分離用溝54、及び第2の素子分離用溝54を埋め込む第2の素子分離用絶縁膜56よりなり、複数の素子形成領域Rを区画する第2の素子分離領域17と、を有する。

(もっと読む)

半導体装置及びその製造方法

【課題】トレンチ分離されたSOI基板にIGBTとその制御回路等が形成される半導体装置において、IGBTの高耐圧化及びターンオフ特性の改善等が必要になる。

【解決手段】ダミー半導体基板16にN型エピタキシャル層8を形成し、N型エピタキシャル層8にトレンチ30を形成し、トレンチ30側壁及びN型エピタキシャル層8表面にN型バッファ層7、次にP型埋め込みコレクタ層6を形成し、トレンチ30底面及びP+型埋め込みコレクタ層6上を埋め込み絶縁膜5で被覆する。埋め込み絶縁膜5上をポリシリコン膜3で被覆し、該ポリシリコン膜3と絶縁膜2を介してP型半導体基板1を貼り合わせた後、ダミー半導体基板16を除去し、略同一平面状に露出するトレンチ30底面の埋め込み絶縁膜5、P+型埋め込みコレクタ層6、N型バッファ層7、N型ドリフト層8a等を具備するSOI基板を形成する。該SOI基板にIGBT等を形成する。

(もっと読む)

1 - 20 / 217

[ Back to top ]