Fターム[5F033HH09]の内容

半導体集積回路装置の内部配線 (234,551) | 単一配線層の材料,層間接続の上層配線層の材料 (33,767) | 金属及びその合金(シリサイドを除く) (23,853) | Al (4,491) | Al合金 (1,292)

Fターム[5F033HH09]の下位に属するFターム

Si、Cu以外を含むもの (235)

Fターム[5F033HH09]に分類される特許

61 - 80 / 1,057

半導体装置

【課題】銅ヒューズに起因する故障または特性悪化を抑制または防止できる半導体装置を提供する。

【解決手段】半導体装置は、半導体基板1と、銅ヒューズ4と、半導体基板1と銅ヒューズ4との間に配置された銅膜からなるシール膜7,8と、銅ヒューズ4よりも上の層に形成された銅以外の金属材料膜からなり、銅ヒューズ4の両端にそれぞれに接続された最上層配線501,502と、シール膜7,8に結合され、銅ヒューズ4の周囲を取り囲む筒状に形成された銅シールリング6とを含む。

(もっと読む)

半導体装置およびその製造方法

【課題】アルミ膜を用いて生産コストの低減を図りながら、歩留りおよび信頼性を両立できる半導体装置およびその製造方法を提供する。

【解決手段】半導体基板1上に形成された酸化膜3上に指向性スパッタによってチタン膜41が形成される。このチタン膜41上に通常のスパッタによって窒化チタン膜42が形成される。さらに、窒化チタン膜42上に、通常のスパッタによってアルミ膜43が形成される。チタン膜41は、(002)配向し、アルミ膜43は(111)配向する。

(もっと読む)

半導体装置

【課題】半導体装置の特性を向上させる。

【解決手段】LDMOSと、LDMOSのソース領域と電気的に接続されるソースプラグP1Sと、ソースプラグP1S上に配置されるソース配線M1Sと、LDMOSのドレイン領域と電気的に接続されるドレインプラグP1Dと、ドレインプラグP1D上に配置されるドレイン配線M1Dと、を有する半導体装置のソースプラグP1Sの構成を工夫する。ドレインプラグP1Dは、Y方向に延在するライン状に配置され、ソースプラグP1Sは、Y方向に所定の間隔を置いて配置された複数の分割ソースプラグP1Sを有するように半導体装置を構成する。このように、ソースプラグP1Sを分割することにより、ソースプラグP1SとドレインプラグP1D等との対向面積が低減し、寄生容量の低減を図ることができる。

(もっと読む)

半導体装置

【課題】表示パネルに設けられるパッド部として適した構造を提供することを目的の一と

する。酸化物半導体の他、絶縁膜及び導電膜を積層して作製される各種用途の表示装置に

おいて、薄膜の剥がれに起因する不良を防止することを目的の一とする。

【解決手段】走査線と信号線が交差し、マトリクス状に配列する画素電極層と、該画素電

極層に対応して設けられた画素部を有し、該画素部に酸素の含有量が異なる少なくとも二

種類の酸化物半導体層とを組み合わせて構成される逆スタガ型薄膜トランジスタが設けら

れた表示装置である。この表示装置において画素部の外側領域には、走査線、信号線を構

成する同じ材質の導電層によって、画素電極層と対向する共通電極層と電気的に接続する

パッド部が設けられている。

(もっと読む)

半導体装置とその製造方法

【課題】配線加工時のエッチングレートの極端な上昇を抑え、プロセスを安定化させる。

【解決手段】炭化珪素基板1上に形成された炭化珪素層20の上に、ソース電極8、ゲート電極9、層間絶縁膜10、層間絶縁膜10上に形成されたソース電極上部配線11およびゲート電極上部配線12とが形成され、ソース電極上部配線11とゲート電極上部配線12の下には、これらの上部配線を構成する金属が炭化珪素層20に拡散することを抑制するためのバリアメタル16が形成されている。層間絶縁膜10には、炭化珪素層20上に形成されたソース電極8およびゲート電極9に到達するようにコンタクトホール13、15が形成されており、バリアメタル16はコンタクトホール内の電極と上部配線との界面、層間絶縁膜10の側壁と上部配線との界面、および側壁の上端部近傍と上部配線との界面にのみ形成されている。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】電極パッド部の安定した電気的接触を確保しつつ電極パッド部の面積を小さくすることができる半導体装置および半導体装置の製造方法を提供する。

【解決手段】半導体装置は、半導体基板と、半導体基板の主表面上であって平面視において素子形成領域内およびダイシングライン領域内の少なくともいずれかに形成された半導体チップ用電極パッド部,TEG用電極パッド部PTとを備えている。半導体チップ用電極パッド部,TEG用電極パッド部PTは、外部と電気的に接続するための表面OSFを有し、かつ半導体チップ用電極パッド部,TEG用電極パッド部PTの辺SIDに対して斜めに傾斜した方向に延びた溝部THPを表面OSFに有している。

(もっと読む)

半導体装置の製造方法

【課題】ドライエッチングによりアルミニウム材料を金属配線とする加工では、加工中に生成されるホトレジストの反応性生成物が固着することから、取り扱いに手間やコストが掛かる高価な専用の剥離液を用いる必要があった。また、この剥離液は、金属配線にダメージを与えるため、金属配線の品質を低下させていた。

【解決手段】塩素ガス又は塩素を含む反応ガスを用いるドライエッチング工程である金属配線形成工程と、ホトレジストを剥離するホトレジスト剥離工程とを有し、このホトレジスト剥離工程は、酸素と水素を含むフッ化炭素との混合ガスを用いフルアッシングする金属配線露出工程と、純水により洗浄する洗浄工程と、酸素を用いるプラズマでアッシングと、の3つの工程からなる。これにより、専用の剥離液による処理が不要になるため、低コストで品質の高い金属配線を形成できる。

(もっと読む)

半導体装置およびその製造方法

【課題】パッドと当該パッドの下地との密着性の向上および信頼性の向上を図ることが可能な半導体装置およびその製造方法を提供する。

【解決手段】半導体装置は、半導体基板1の一表面側に熱酸化膜1bとシリコン窒化膜32と層間絶縁膜50とパッシベーション膜60との積層構造を有する半導体装置であって、熱酸化膜1b上にパッド80を形成してある。半導体装置の製造方法では、半導体基板1の上記一表面側に熱酸化膜1bと熱酸化膜1bの表面の一部を覆うシリコン窒化膜32とを有する基本構造を形成してから、半導体基板1の上記一表面側に層間絶縁膜50を形成する。基本構造の形成にあたっては、シリコン窒化膜32のうち熱酸化膜1bにおけるパッド80の形成予定領域に形成した部分を除去する。層間絶縁膜の形成後であってパッド80の形成前に層間絶縁膜50のうち熱酸化膜1bにおけるパッド80の形成予定領域上に形成されている部分を除去する。

(もっと読む)

半導体基板への有機膜パターンの直接描画プロセスにおける前処理方法

【課題】直接描画法によりレジストの膜パターンやパッシベーション用などの有機膜パターンを形成する際に発生し易い描画性や密着性の問題を防ぐことのできる半導体基板への有機膜パターンの直接描画プロセスにおける前処理方法を提供すること。

【解決手段】相互に異なる材料で構成された複数のパターン膜2、3、4で覆われた半導体基板1表面上に、前記複数のパターン膜2、3、4上に跨って積層される有機膜パターン5を直接描画法により形成する際に、前処理として前記半導体基板1表面を、プラズマ生成ガスとして酸素と窒素を用いてアッシングし、続いて水素と窒素をプラズマ生成ガスとして用いてクリーニング処理を行う。

(もっと読む)

半導体装置

【課題】安定した特性のヒューズ素子を有する半導体装置を提供する。

【解決手段】半導体装置100は、基板10と、基板10の上方に形成され、空洞部20を画成する被覆構造体30と、空洞部20に収容されたヒューズ素子40a,40b,40cと、を含み、被覆構造体30は、導電層を有し、ヒューズ素子40a,40b,40cの材質は、導電層の材質と同じである。

(もっと読む)

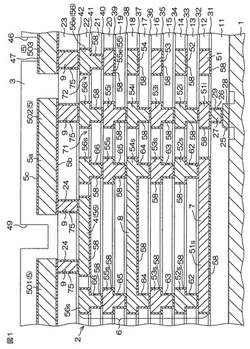

能動領域ボンディングの両立性のある高電流構造体

【課題】ボンディング・パッド下方に各回路を有する集積回路。

【解決手段】一実施例において、集積回路は基板と、最上部導電層と、1つ以上の中間導電層と、絶縁材料から成る各層と、各デバイスとを具備する。最上部導電層は少なくとも1個のボンディング・パッド及び比較的硬質の材料から成る副層を有する。1つ以上の中間導電層は最上部導電層及び基板の間に形成する。絶縁材料から成る各層は各導電層を分離する。更に、絶縁材料から成る各層のうちの1つの層は比較的硬質で、最上部導電層及びこの最上部導電層に最も近接した中間導電層の間に位置する。各デバイスは集積回路に形成する。また、最上部導電層に最も近接した少なくとも中間導電層は、ボンディング・パッド下方の各選択デバイスの機能的相互接続部に対して適合する。

(もっと読む)

半導体装置

【課題】基板の大型化に対応し得る金属配線を作製する。

【解決手段】絶縁表面上に少なくとも一層の導電膜12,13を形成し、前記導電膜12,13上にレジストパターンを形成し、前記レジストパターンを有する導電膜にエッチングを行い、バイアス電力密度、ICP電力密度、下部電極の温度、圧力、エッチングガスの総流量、エッチングガスにおける酸素または塩素の割合に応じてテーパー角αが制御された金属配線を形成する。このようにして形成された金属配線は、幅や長さのばらつきが低減されており、基板10の大型化にも十分対応し得る。

(もっと読む)

半導体装置およびその製造方法

【課題】DRAMセルとロジックを混載したLSIデバイスにおけるアスペクト比の大きいコンタクト構造において、素子分離絶縁膜および不純物拡散層のオーバエッチングを抑制して、接合リークを抑制することを課題とする。

【解決手段】周辺MOSトランジスタを覆う第1エッチングストッパ層121と、DRAMメモリセルのキャパシタ部上層に第2エッチングストッパ層122が形成され、周辺MOSトランジスタの不純物拡散層113は、第1、第2エッチングストッパ層121、122を貫通する電極層131により、上記キャパシタ部上層に形成された金属配線層と接続され、不純物拡散層113の少なくとも一つは素子分離絶縁膜102の境界上に電極層131を接続し、素子分離絶縁膜102上に形成された電極層131の底部の不純物拡散層113表面からの深さ寸法は、不純物拡散層113の接合深さ寸法もより短く形成されたものである。

(もっと読む)

半導体装置およびその製造方法

【課題】工程数を削減して生産性を向上できる構造の半導体装置およびその製造方法を提供する。

【解決手段】半導体装置の製造方法は、半導体層1にトレンチ20を形成する工程と、トレンチ2の内壁およびトレンチ2外の表面を覆うように半導体層1上に絶縁膜3を形成する工程と、トレンチ2を埋め尽くし、トレンチ2外の絶縁膜3上に堆積されるように導電性のポリシリコン膜4を形成する工程と、トレンチ2内、およびトレンチ2外の絶縁膜3上の所定領域にポリシリコン膜4が残るように、当該ポリシリコン膜4を選択的に除去するポリシリコンエッチング工程とを含む。

(もっと読む)

多層薄膜パターン及び表示装置の製造方法

【課題】間便に所望の形状のパターンを得ることのできる多層薄膜パターン及び表示装置の製造方法を提供すること。

【解決手段】基板上に層間絶縁膜1を形成する工程と、層間絶縁膜1上に導電性を有する第1の薄膜2を形成する工程と、第1の薄膜2上に第2の薄膜3を形成する工程と、第2の薄膜3上に、複数階調露光によって膜厚差を有するレジストパターン5を形成する工程と、膜厚差を有するレジストパターン5を介して、第2の薄膜3及び第1の薄膜2をエッチングして、レジストパターンの存在しない領域の層間絶縁膜1を露出させる工程と、膜厚差を有するレジストパターン5をアッシングして、レジストパターンの薄膜部5bを除去する工程と、薄膜部5bが除去されたレジストパターン5cを介して、第2の薄膜3をエッチングする工程と、を順次実施する。

(もっと読む)

半導体装置の製造方法

【課題】製造工程数を削減し、電気抵抗値のバラツキを低減して歩留まりを向上させる。

【解決手段】まず、半導体基板1の平面1aに、開口部を有するマスク層を形成し、次いで、半導体基板1に、マスク層の開口部から電極パッド層4に達するビアホール6を形成した後、マスク層を除去する。次に、金属層形成工程において、半導体基板1に形成したビアホール6の底部6aとなる電極パッド層4上に、電極パッド層4よりも絶縁材料の密着性が低い金属層8を形成する。次に、絶縁層形成工程において、化学気相成長法にて金属層8を除く部分、即ちビアホール6の側壁部6bに絶縁材料からなる絶縁層9を形成する。そして、導電膜形成工程において、半導体基板1の平面1a及びビアホール6の内部に導電層12を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、アルミ配線パターンに含まれるアルミニウムと銅配線に含まれる銅とが反応して高抵抗の合金が生成されることを防止した上で、導電膜である窒化チタン膜に起因する半導体基板の反りを低減することの可能な半導体装置及びその製造方法を提供することを課題とする。

【解決手段】第2の層間絶縁膜18に形成されたコンタクト孔27により露出された銅配線16の上面16aを覆うように、窒化チタン膜を含む第1の導電膜21を設けると共に、アルミ配線パターン23と第1の導電膜21及び第2の層間絶縁膜18との間に、窒化チタン膜を含まない第2の導電膜22を設ける。

(もっと読む)

導電膜用エッチング液組成物

【課題】基板上に形成されたモリブデン系導電性薄膜、または、モリブデン系導電性薄膜とアルミニウム系導電性薄膜とが積層された積層導電性薄膜を、効率よく、側面が良好な順テーパー形状となるようなエッチングを行うことが可能なエッチング液、および、該エッチング液を用いたエッチング方法を提供することを目的とする。

【解決手段】(a)リン酸30〜80重量%と、(b)硝酸0.1〜20重量%と、(c)有機酸塩0.1〜20重量%と、(d)水とを含有するエッチング液を用いてエッチングを行う。

また、上記エッチング液を用いて、アルミニウム系導電性薄膜と、モリブデン系導電性薄膜とを備えてなる2層構造の積層導電性薄膜、または、アルミニウム系導電性薄膜と、アルミニウム系導電性薄膜を挟み込むようにその両主面側に配設された第1のモリブデン系導電性薄膜および第2のモリブデン系導電性薄膜を備えてなる3層構造の積層導電性薄膜をエッチングする。

(もっと読む)

半導体装置の製造方法

【課題】水素又はカルボン酸を用いたリフロー時の導電部と絶縁層の密着力低下を抑制する。

【解決手段】半導体基板の上に設けられた第1導電部上に絶縁層を形成し(ステップS1)、その絶縁層を被覆するようにバリア層を形成した後(ステップS2)、そのバリア層の上に第2導電部を形成する(ステップS3)。そして、第1導電部上の絶縁層がバリア層で被覆されている状態で、第2導電部を水素又はカルボン酸を含む雰囲気中で溶融し(ステップS4)、その後、その第2導電部をマスクにして、絶縁層の上からバリア層を除去する(ステップS5)。

(もっと読む)

半導体装置の作製方法及び表示装置の作製方法

【課題】材料の利用効率を向上させ、かつ、作製工程を簡略化して、信頼性の高い半導体

装置を作製する方法を提供する。

【解決手段】基板上に導電層を形成し、該導電層上に光透過層を形成し、該光透過層上か

らフェムト秒レーザを照射して、該導電層及び該光透過層を選択的に除去する工程を有す

る。なお、該導電層の端部は、該光透過層の端部より内側に配置されるように該導電層及

び該光透過層を除去されていてもよい。また、フェムト秒レーザを照射する前に、該光透

過層表面に撥液処理を行ってもよい。

(もっと読む)

61 - 80 / 1,057

[ Back to top ]