Fターム[5F033HH20]の内容

半導体集積回路装置の内部配線 (234,551) | 単一配線層の材料,層間接続の上層配線層の材料 (33,767) | 金属及びその合金(シリサイドを除く) (23,853) | 高融点金属 (8,733) | Mo (732)

Fターム[5F033HH20]に分類される特許

161 - 180 / 732

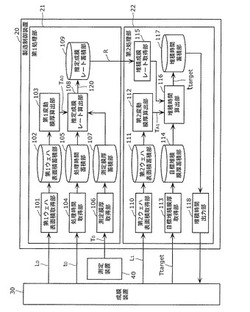

製造制御装置及び製造制御方法

【課題】膜厚変動を抑制することにより、トランジスタ特性のばらつきを低減できる製造制御装置及び製造制御方法を提供する。

【解決手段】第1半導体ウェハ上に絶縁膜を堆積する成膜装置30を制御する制御パラメータ(堆積時間ttarget)を算出する製造制御装置20であって、第2半導体ウェハの第2ウェハ表面積L1が大きいほど、成膜装置30に絶縁膜を厚く堆積させる制御パラメータ(堆積時間ttarget)を算出する。また、製造制御装置20は、第2ウェハ表面積L1が大きいほど堆積時間ttargetが長くなるように堆積時間ttargetを算出する堆積時間算出部116を備えてもよい。

(もっと読む)

金属薄膜の製造方法および半導体装置の製造方法

【課題】金属薄膜パターンの端部におけるバリ発生を確実に防止できる金属薄膜の製造方法および半導体装置の製造方法を提供する。

【解決手段】本発明は、所定パターンの金属薄膜パターン8を形成するための方法であって、下地の上に、前記パターンのエッジに対応する位置近傍に壁面を有する段差パターン3を形成する工程と、段差パターン3を含む下地全体にレジスト4を塗布する工程と、塗布したレジスト4に対して、前記パターンの反転パターンとなるようにパターニングを施す工程と、レジスト4および段差パターン3を含む下地全体に金属薄膜5を形成する工程と、溶剤を塗布して、レジスト4および該レジスト4上に位置する金属薄膜5を除去する工程とを含む。

(もっと読む)

薄膜トランジスタの製造方法及び表示装置の製造方法

【課題】レジスト組成物を用いたマスクパターンを用いることなくTFT及びそれを用いた表示装置を製造することを目的とする。

【解決手段】ロールツーロール方式により加工処理を行う表示装置の製造方法であって、組成物の吐出口が一軸方向に複数個配列した第1の液滴吐出手段により、可撓性を有する基板上に開口部を有する絶縁性樹脂膜を形成し、組成物の吐出口が一軸方向に複数個配列した第2の液滴吐出手段により、開口部にゲート電極を形成し、プラズマの噴出口が一軸方向に複数個配列したノズル体を備えた被膜形成手段により、ゲート電極および絶縁性樹脂膜上にゲート絶縁膜を形成する。

(もっと読む)

電子素子及びその製造方法、並びに表示装置

【課題】低温プロセスで製造でき、リーク電流が抑制された電子素子を提供する。

【解決手段】基板10上に、端部断面のテーパー角度が60°以下である下部電極22と、前記下部電極22上に配置され、水素原子の含有率が3原子%以下であり、波長650nmにおける屈折率nが1.475以下であるSiO2膜24と、前記SiO2膜24上に配置され、前記下部電極22と重なり部を有する上部電極26と、を有する電子素子である。

(もっと読む)

液晶パネル

【課題】複数個のアレイ基板を同時に形成するためのアレイ基板用マザー基板にスピンコ

ーターを用いてレジスト塗布する際、表示領域内に放射状の塗布ムラが生じないような配

線パターンとされたアレイ基板を備えた液晶パネルを提供すること。

【解決手段】本発明の液晶パネルは、液晶層を挟持して対向配置された一対の基板を有し

、前記一対の基板の一方の表示領域には複数のサブ画素がマトリクス状に形成されている

と共に、表示領域の周縁部には表示領域からゲート配線39G及びソース配線39Sが端

子領域まで延在されている液晶パネルにおいて、前記互いに隣接するゲート配線39G及

びソース配線39S等の引き回し配線の直近の屈曲点P1同士を順次結んでなるラインが

、端子領域が形成されている辺と実質的に平行な直線ラインL1とされている。

(もっと読む)

レーザーを用いたパターン形成方法

【課題】パターン形成のタクトタイムの短縮を可能とし、またパターン層と誘電体層の一括焼成を可能にし、パターン形成のトータル的低コスト化が可能なパターニング方法を提供することを目的とする。

【解決手段】無機粉末と、ガラスフリットと、溶剤からなる混合物を基板上に塗布する塗布工程と、塗布された前記混合物を乾燥する乾燥工程と、レーザー照射により前記乾燥工程を経た塗膜にパターンを描画するレーザー照射工程と、前記パターンを現像する現像工程とを含むパターン形成方法。

(もっと読む)

Al−Ni系合金配線材料及びそれを用いた素子構造

【課題】ITOなどの透明電極層と直接接合が可能なAl系合金配線材料であって、現像液への耐食性に優れ、コンタクトホール形成時における耐食性にも優れ、大面積のガラス基板において素子を形成した場合においても、そのガラス基板面内に形成された素子の接合抵抗値をより均一にすることができるAl−Ni系合金配線材料を提供する。

【解決手段】アルミニウムにニッケルを含有したAl−Ni系合金配線材料において、セリウムとボロンとを含有し、各濃度は、ニッケル含有量をニッケルの原子百分率Xat%とし、セリウム含有量をセリウムの原子百分率Yat%とし、ボロン含有量をボロンの原子百分率Zat%とした場合、式0.5≦X≦5.0、0.01≦Y≦1.0、0.01≦Z≦1.0の各式を満足する領域の範囲内にある。

(もっと読む)

半導体装置

【課題】開口率の高い半導体装置又はその作製方法を提供することを目的の一とする。また、消費電力の低い半導体装置又はその作製方法を提供することを目的の一とする。

【解決手段】絶縁表面を有する基板上に設けられた半導体層と、半導体層を覆うゲート絶縁膜と、ゲート絶縁膜上に設けられた第1の導電層と第2の導電層とで積層されたゲート電極を含むゲート配線と、半導体層と前記ゲート電極を含む前記ゲート配線を覆う絶縁膜と、絶縁膜上に設けられ、半導体層と電気的に接続され、第3の導電層と第4の導電層とで積層されたソース電極を含むソース配線と、を有し、ゲート電極は、第1の導電層で形成され、ゲート配線は、第1の導電層と第2の導電層で形成され、ソース電極は、第3の導電層で形成され、ソース配線は、第3の導電層と第4の導電層で形成されている。

(もっと読む)

半導体装置

【課題】配線抵抗の低い半導体装置を提供すること、透過率の高い半導体装置を提供すること、または開口率の高い半導体装置を提供することを課題とする。

【解決手段】ゲート電極、半導体層、ソース電極又はドレイン電極を透光性を有する材料を用いて形成し、ゲート配線又はソース配線等の配線を透光性を有する材料より抵抗率が低い材料で設ける。また、ソース配線及び/又はゲート配線を、透光性を有する材料と当該透光性を有する材料より抵抗率が低い材料を積層させて設ける。これにより、配線抵抗が低く、透過率の高い半導体装置を提供することができる。

(もっと読む)

半導体装置とその製造方法、電気光学装置とその製造方法、回路基板とその製造方法、及び電子機器

【課題】フォトリソグラフィー法及びエッチング法を用いることなく導電層間を接続することができる半導体装置の製造方法を提供する。

【解決手段】本発明の半導体装置の製造方法は、基板上に第1導電層と層間絶縁膜と第2導電層とを順に積層形成する導電層工程と、前記第2導電層の表面から物理的加工を施すことで、前記第2導電層と前記層間絶縁膜とを貫通して前記第1導電層に達する凹部を形成するコンタクトホール形成工程と、を有することを特徴とする。

(もっと読む)

半導体装置

【課題】コンタクトホールの加工時において配線のダメージを受けにくく、信頼性の低下を抑制できる構造の接続部を有する半導体装置を提供すること。

【解決手段】接続部1は、第1導電層2と第2導電層4とが、その交差個所に設けられたコンタクトホール5を介して接続されたものである。矩形状のコンタクトホール5は第2導電層4の幅方向の略中央に配置されている。そして、コンタクトホール5のパターンを囲むように矩形状の半導体層3が設けられている。半導体層3は、コンタクトホール5の底部において第1導電層2上に形成されている。この半導体層3は、第1導電層2とのエッチング選択比が高く、第1導電層2に対するエッチング効率が充分に高いものである。

(もっと読む)

液晶表示パネル及びその製造方法

【課題】スイッチング素子としてのトップゲート式TFTと、前記TFTを遮光するため

の遮光膜とが設けられた液晶表示パネルにおいて、遮光膜の材料としてMoを採用し、遮

光膜の被覆絶縁層にドライエッチング処理を施してMoの表面を露出させる場合にも、オ

ーバーエッチングによる遮光膜の消失を防げるようにした液晶表示パネルを提供すること

。

【解決手段】本発明の液晶表示パネル1は、遮光膜11がMoからなり、かつ、遮光膜1

1と上層金属配線との電気的接続が、バッファ絶縁膜12とゲート絶縁膜14を貫通する

第1コンタクトホール27を経て遮光膜11と電気的に接続されていると共に層間絶縁膜

16に被覆された第1導電部材25と、層間絶縁膜16を貫通する第2コンタクトホール

28を経て層間絶縁膜16の表面の金属配線と電気的に接続された第2導電部材26と、

を経て行われている。

(もっと読む)

半導体装置

【課題】半導体膜の厚みを適当な範囲に制御することによって、大きいドレイン電流を有するとともに、所望の電気的特性を備える半導体装置を提供する。

【解決手段】半導体装置は、主表面1aを有するガラス基板1と、主表面1a上に設けられ、チャネル領域11と、チャネル領域11の両側に位置するソース領域9およびドレイン領域13とが形成されたポリシリコン膜7と、ポリシリコン膜7に接触するように設けられたゲート絶縁膜17と、ゲート絶縁膜17を介してチャネル領域11に向い合う位置に設けられたゲート電極21とを備える。ポリシリコン膜7は、50nmを超え150nm以下の厚みを有する。ソース領域9およびドレイン領域13は、ポリシリコン膜7の頂面7aからポリシリコン膜7の底面7cにまで達して形成されている。

(もっと読む)

半導体装置の製造方法

【課題】Au系微細金属配線を線幅制御性良く形成することを可能とする半導体装置の製造方法を提供すること。

【解決手段】基板1上の絶縁膜2の上にAuを主材料とする金属配線層3を形成し、金属配線層3上にマスク用W層4を形成し、マスク用W層4上にレジスト層を形成してこのレジスト層をパターニングし、パターニングされたレジスト層5をマスクとしてマスク用W層4を反応性イオンエッチング法によりパターニングし、パターニングされたマスク用W層4をマスクとして金属配線層3を、アルゴンと酸素の混合ガスを用いる反応性イオンエッチング法により選択的に除去した後、マスク用W層4を反応性イオンエッチング法により除去することによってAu系金属配線を形成する金属配線形成工程を備えることを特徴とする半導体装置の製造方法を構成する。

(もっと読む)

薄膜トランジスタ表示板の製造方法およびこれに使用されるネガティブフォトレジスト組成物

【課題】パターンの不良が減少した薄膜トランジスタ表示板の製造方法およびこれに使用されるネガティブフォトレジスト組成物を提供する。

【解決手段】基板上に導電性物質からなる導電膜を形成する段階と、導電膜上にネガティブフォトレジスト組成物からなるエッチングパターンを形成する段階と、エッチングパターンをエッチングマスクとして利用して導電膜をエッチングし、導電膜パターンを形成する段階とを含み、ネガティブフォトレジスト組成物は、アルカリ現像液に溶解性を有するヒドロキシル基を含有するノボラック樹脂10〜50重量部、第1光酸発生剤(特定構造のスルホニルオキシイミド化合物)0.5〜10重量部、第2光酸発生剤(第1光酸発生剤とは構造の異なる特定構造のスルホニルオキシイミド化合物)0.5〜10重量部、架橋結合剤1〜20重量部および溶媒10〜90重量部を含む。

(もっと読む)

半導体装置の作製方法

【課題】 レジスト材料の利用効率を向上させて、作製コストの削減を目的としたレジス

トパターンの作製方法、レジストパターンの除去方法、半導体装置の作製方法を提供する

ことを課題とする。

【解決手段】 本発明は、減圧下で、被加工物上に、感光剤を含む組成物を吐出してレジ

ストパターンを形成するステップを有することを特徴とする。また、前記レジストパター

ンをマスクとして前記被加工物をエッチングするステップ、若しくは、前記レジストパタ

ーンに、フォトマスクを介して前記感光剤の感光波長域の光を照射するステップ、前記レ

ジストパターンをマスクとして前記被加工物をエッチングするステップ、前記被加工物上

の前記レジストパターンを除去するステップを有することを特徴とする。

(もっと読む)

半導体集積回路装置および半導体集積回路装置の製造方法

【課題】一般的なウエハ・レベル・パッケージ・プロセスでは、メッキ・プロセス中におけるスクライブ領域のアルミニウム系パッド電極の腐食を防止するために、製品領域における有機系保護膜と同層のパッド保護用樹脂膜でパッド電極をカバーしている。しかし、これでは再配線形成後にスクライブ領域のパッド電極に対するプローブ検査が実行できない。

【解決手段】本願発明は、ウエハ・レベル・パッケージ方式の半導体集積回路装置の製造方法において、チップ領域およびスクライブ領域の有機系保護膜を相互に連結した一体の膜パターンとし、ペレタイズ工程においては、スクライブ領域中央部の有機系保護膜を含む表層部分を先ず、レーザ・グルービングで除去することで幅広の溝を形成し、その後、この溝内の中央部をダイシング処理することで、ここのチップ領域に分離するものである。

(もっと読む)

半導体装置およびその作製方法

【課題】酸化物半導体層を用い、電気特性の優れた薄膜トランジスタを備えた半導体装置を提供することを課題の一つとする。

【解決手段】チャネル形成領域にSiOxを含む酸化物半導体層を用い、電気抵抗値の低い金属材料からなるソース電極層及びドレイン電極層とのコンタクト抵抗を低減するため、ソース電極層及びドレイン電極層と上記SiOxを含む酸化物半導体層との間にソース領域またはドレイン領域を設ける。ソース領域またはドレイン領域は、SiOxを含まない酸化物半導体層または酸窒化物膜を用いる。

(もっと読む)

半導体装置の製造方法及び半導体装置

【目的】配線抵抗の上昇を抑制したまま、EM特性を改善させる半導体装置或いはその製造方法を提供することを目的とする。

【構成】本発明の一態様の半導体装置の製造方法は、基体上に絶縁膜を形成する工程(S104)と、絶縁膜に開口部を形成する工程(S106)と、開口部内に、ケイ化物の形成エネルギーがCuケイ化物の形成エネルギーよりも小さい金属含有膜を形成する工程(S108)と、前記金属含有膜が形成された開口部内に銅(Cu)膜を埋め込む工程(S112)と、Cu膜上に、300℃未満の温度でCuとSiとを含有する化合物膜を選択的に形成する工程(S120)と、を備えたことを特徴とする。

(もっと読む)

半導体装置及びその製造方法

【課題】 ビアホールの微細化及び高アスペクト比化が進むと、銅からなるシード層でビアホールの内面を連続的に覆うことが困難になる。

【解決手段】 半導体基板(10)の上に絶縁膜(20)が形成されている。絶縁膜に凹部(21)が形成されている。凹部の内面を第1の導電膜(22)が覆う。島状組織(25)が、第1の導電膜の表面に離散的に分布する。島状組織は、銅に対して、第1の導電膜の濡れ性よりも高い濡れ性を有する。凹部が、銅または銅合金からなる導電部材(31)で充填されている。

(もっと読む)

161 - 180 / 732

[ Back to top ]