Fターム[5F033HH25]の内容

半導体集積回路装置の内部配線 (234,551) | 単一配線層の材料,層間接続の上層配線層の材料 (33,767) | シリサイド (1,618)

Fターム[5F033HH25]の下位に属するFターム

高融点金属のシリサイド (1,006)

Fターム[5F033HH25]に分類される特許

141 - 160 / 612

半導体装置及びその製造方法

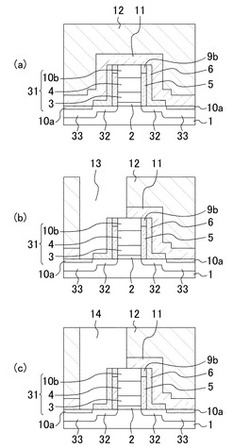

【課題】シェアードコンタクト形成時に、ゲート電極が溶解されて形状異常となるのを防止する。

【解決手段】半導体装置は、基板1上にゲート絶縁膜2を介して形成されたゲート電極31と、基板1のゲート電極31の両側方に形成された不純物領域32及び33とを有するトランジスタと、トランジスタ上を覆うように基板1上に形成された層間絶縁膜11及び12と、不純物領域32及び33及びゲート電極31に電気的に接続するシェアードコンタクト14とを備える。ゲート電極31の側面下部を覆うように第1のサイドウォール5、第1のサイドウォール5におけるゲート電極31とは反対側に第2のサイドウォール6、第1のサイドウォール5上に、ゲート電極31の側面上部と第2のサイドウォール6とに挟まれるように第3のサイドウォール9bが形成されている。第2及び第3のサイドウォール6及び9bは、第1のサイドウォール5とは異なる材料からなる。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置内の局所配線を簡単な工程で形成するための半導体装置の製造方法を提供する。

【解決手段】シリコン基板101上に1又は複数の半導体素子が作り込まれてなる半導体装置に局所配線構造を形成する際に、半導体素子の2つの導電領域を絶縁している絶縁領域に、この2つの導電領域を接続するようにシリコン膜104又は第1金属膜109を形成し(第1工程)、形成されたシリコン膜又は第1金属膜上に無電解めっき法により選択的に第2金属膜110を形成する(第2工程)。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置内の埋め込みコンタクトホールを簡略な工程で形成するための半導体装置の製造方法を提供する。

【解決手段】シリコン基板101上に1又は複数の半導体素子が作り込まれてなる半導体装置に埋め込みコンタクトを形成するにあたり、半導体素子層の全面に層間絶縁膜109を形成する(第1工程)。次いで、半導体装置内のシリコン106、107、ポリシリコン104A、104B、又は金属シリサイド108A,108Bからなる2つの領域が露出するように層間絶縁膜にコンタクトホール109aを形成する(第2工程)。そして、コンタクトホールから露出しているシリコン106、107、ポリシリコン104A、104B、又は金属シリサイド108A,108Bの表面に無電解めっき法により選択的に金属膜111を形成する(第3工程)。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体装置の性能を向上させる。

【解決手段】半導体基板1に形成したnチャネル型MISFETQnのソース・ドレイン用のn+型半導体領域7bおよびゲート電極GE1上と、pチャネル型MISFETQpのソース・ドレイン用のp+型半導体領域8bおよびゲート電極GE2上とに、ニッケル白金シリサイドからなる金属シリサイド層13bをサリサイドプロセスで形成する。その後、半導体基板1全面上に引張応力膜TSL1を形成してから、pチャネル型MISFETQp上の引張応力膜TSL1をドライエッチングで除去し、半導体基板1全面上に圧縮応力膜CSL1を形成してからnチャネル型MISFETQn上の圧縮応力膜CSL1をドライエッチングで除去する。金属シリサイド層13bにおけるPt濃度は、表面が最も高く、表面から深い位置になるほど低くなっている。

(もっと読む)

半導体装置の製造方法

【課題】配線層に銅配線を使用する半導体装置において、半導体基板の裏面に付着した銅原子が半導体基板の裏面から内部へと拡散することを抑制し、半導体基板の主面に形成されているMISFETなどの半導体素子の特性劣化を抑制できる技術を提供する。

【解決手段】半導体基板1Sの主面に形成される銅拡散防止膜を銅拡散防止膜DCF1aとし、半導体基板1Sの裏面に形成される銅拡散防止膜を銅拡散防止膜DCF1bとする。本実施の形態1の特徴は、半導体基板1Sの裏面に銅拡散防止膜DCF1bを形成する点にある。このように、銅配線の形成工程の前に、半導体基板1Sの裏面に銅拡散防止膜DCF1bを形成することにより、半導体基板1Sの裏面から銅原子(銅化合物を含む)が拡散することを防止できる。

(もっと読む)

半導体集積回路装置の製造方法

【課題】ニッケル系メタル・シリサイドとコンタクト用メタル間でのコンタクト抵抗の低抵抗化がホールの微細化に伴って、困難になるという問題がることが、本願発明者の検討により明らかとなった。

【解決手段】本願の一つの発明は、ニッケル系メタル・シリサイドによりソース・ドレイン領域等のシリサイデーションを施したMISFETを有する半導体集積回路装置の製造方法において、プリ・メタル絶縁膜に設けられたコンタクト・ホールにバリア・メタルを形成する前に、シリサイド膜の上面に対して、窒素水素間結合を有するガスを主要なガス成分の一つとして含む非プラズマ還元性気相雰囲気中で、熱処理を実行するものである。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート電極との短絡を抑えたセルフアラインコンタクトを有する、製造コストの低い半導体装置およびその製造方法を提供する。

【解決手段】本発明の一態様に係る半導体装置100は、それぞれ半導体基板2上に形成され、それぞれゲート電極4a、4bを有し、互いの間のソース・ドレイン領域8aを共有する隣接したトランジスタ1a、1bと、ゲート電極4a上に形成された絶縁膜11aと、ゲート電極4b上に形成された絶縁膜11aよりも厚さの厚い領域を有する絶縁膜11bと、ソース・ドレイン領域8aに接続され、その中心位置がゲート電極4a、4bの間の中心位置よりもゲート電極4b側に位置するSAC14と、を有する。

(もっと読む)

イメージセンサー装置および半導体イメージセンサー装置の製造方法

【課題】半導体イメージセンサー装置を提供する。

【解決手段】半導体イメージセンサー装置は、第一および第二半導体基板を含む。画素アレイと制御回路とが、第一基板の第一表面中に形成される。相互接続層が、第一基板の第一表面の上に形成され、制御回路を画素アレイに電気的に接続する。頂部導電層が、相互接続層を介して制御回路または画素アレイの少なくとも一つと電気的接続を有するように、相互接続層の上に形成される。第二基板の表面は、頂部導電層に接合される。導電性スルーシリコンビア(TSV)は第二基板を貫通し、頂部導電層と電気的接続を有する。第二基板の反対の表面上に端子が形成され、TSVに電気的に接続される。

(もっと読む)

配線材料、TFT回路基板、及びターゲット材

【課題】ガラス基板への密着性が高いと共に、Siを含んだ層へのCuの拡散を抑制し、配線とSiを含んだ層とのコンタクト抵抗を低くすることができる配線を提供することができ、また、当該配線材料を用いた回路基板と、当該配線材料用のターゲット材とを提供する。

【解決手段】本発明に係る回路基板用の配線材料は、Cuよりも優先的にSiとの間でシリサイドを形成するシリサイド形成材と、Siの酸化物生成自由エネルギーよりも酸化物生成自由エネルギーが低い少なくとも1種類の添加物とが添加され、残部がCu及び不可避的不純物からなる。

(もっと読む)

半導体装置およびその製造方法

【課題】低コストかつ高製造歩留まりで、BiCMOS型半導体集積回路装置を実現することができる半導体装置およびその製造方法を提供する。

【解決手段】シャロートレンチ3、ディープトレンチ6に囲まれた半導体層2の基板領域17に、p型の単結晶半導体からなるエピタキシャル・ベース層24が島状に形成される。当該島状領域を含む半導体層2上の全面に窒化シリコン膜42、酸化シリコン膜43が形成される。島状領域上の異なる位置の窒化シリコン膜42、酸化シリコン膜43には、少なくとも2つの開口部が形成され、開口部が形成された窒化シリコン膜42、酸化シリコン膜43上に半導体膜44が形成される。当該半導体膜44が選択的に除去され、一方の開口部において島状領域に接続するベース電極と、他方の開口部において島状領域に接続するエミッタ電極とが同時に形成される。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】含境界部分における金属シリサイド層の厚さに関係なく、金属シリサイド層の抵抗値を自由に調整することができる半導体装置を提供する。

【解決手段】半導体基板12に形成されたNチャネル型トランジスタ形成領域14と、Pチャネル型トランジスタ形成領域16と、Nチャネル型トランジスタ形成領域14とPチャネル型トランジスタ形成領域16とに跨って延在し、Nチャネル型トランジスタ形成領域14とPチャネル型トランジスタ形成領域16との境界線Lを含む領域に形成された含境界部分および境界線を含まない領域に形成された無境界部分を有すると共に、導電性シリコン層28と、導電性シリコン層28表面に形成され、含境界部分における厚さおよび無境界部分における厚さが異なる金属シリサイド層30(30A,30B)と、を備えるゲート電極と、を備えた半導体装置。

(もっと読む)

半導体装置およびその製造方法

【課題】プラグとシリサイド領域との間の電気抵抗を小さくすることができる半導体装置およびその製造方法を提供する。

【解決手段】シリサイド領域SCs、SCgを各々が有する少なくとも1つの半導体素子NT、PTが半導体基板SB上に形成される。シリサイド領域上に層間絶縁膜が形成される。シリサイド領域SCs、SCgからなる底面を有する内面が設けられたスルーホールTHが層間絶縁膜ILD1に形成される。内面を被覆するTi(チタン)膜が化学気相成長法によって形成される。内面を被覆するバリアメタル膜を形成するためにTi膜TFの少なくとも表面部が窒化される。バリアメタル膜を介してスルーホールTHを埋めるプラグが形成される。

(もっと読む)

半導体装置の製造方法及び半導体装置

【目的】配線抵抗の上昇を抑制したまま、EM特性を改善させる半導体装置或いはその製造方法を提供することを目的とする。

【構成】本発明の一態様の半導体装置の製造方法は、基体上に絶縁膜を形成する工程(S104)と、絶縁膜に開口部を形成する工程(S106)と、開口部内に、ケイ化物の形成エネルギーがCuケイ化物の形成エネルギーよりも小さい金属含有膜を形成する工程(S108)と、前記金属含有膜が形成された開口部内に銅(Cu)膜を埋め込む工程(S112)と、Cu膜上に、300℃未満の温度でCuとSiとを含有する化合物膜を選択的に形成する工程(S120)と、を備えたことを特徴とする。

(もっと読む)

半導体装置

【課題】コンタクト抵抗を低減し、動作信頼性を向上出来る半導体装置を提供すること。

【解決手段】半導体基板10上に形成された、第1導電型の第1MOSトランジスタ5と、前記半導体基板10上に形成された、第2導電型の複数の第2MOSトランジスタ6と、円形の平面形状を有する第1コンタクトプラグCP10−1と、楕円形の平面形状を有する第2コンタクトプラグCP10−2とを具備し、前記第2コンタクトプラグCP10−2は、前記第2MOSトランジスタ6のいずれか6−1の、ソースまたはドレイン上に形成され、前記第1コンタクトプラグCP10−1は、残りの前記第2MOSトランジスタ6−2、及び前記第1MOSトランジスタ5の、ソースまたはドレイン上に形成される。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】ゲート絶縁膜の厚さが異なるトランジスタを有する半導体装置の製造歩留まりを向上させる。

【解決手段】シリコン基板1上に高耐圧絶縁膜IH1を形成した後、高耐圧絶縁膜IH1の表面を削って膜厚を薄くし、高耐圧絶縁膜IH1と隣接するようにして中耐圧絶縁膜IM1を形成する。高耐圧絶縁膜IH1は、熱酸化法によって、シリコン基板1の主面より内側から外側に至るようにして形成し、中耐圧絶縁膜IM1は高耐圧絶縁膜IH1より薄くなるようにして形成する。高耐圧絶縁膜IH1は高耐圧MISトランジスタのゲート絶縁膜として、中耐圧絶縁膜IM1は中耐圧MISトランジスタのゲート絶縁膜として形成する。

(もっと読む)

半導体装置の製造方法

【課題】ダミーアクティブを有するフィールド領域を貫通する貫通電極を含み、且つサリサイド技術が適用された半導体装置において、貫通孔の側壁におけるノッチの発生を防止することができる半導体装置の製造方法を提供する。

【解決手段】複数の能動素子を含む第1領域と能動素子を有しない第2領域とを有するシリコン基板と、能動素子のいずれかに電気的に接続された少なくとも1つの電極パッドと、シリコン基板の裏面から第2領域を経由して電極パッドに電気的に接続された少なくとも1つの貫通電極と、を含む半導体装置の製造方法であり、シリコン基板に第1領域において能動素子間を絶縁分離する素子分離層110を形成するとともに、第2領域において絶縁体層内にシリコン基板の基材が露出したダミー部200を形成する。少なくとも貫通電極と交差する位置においてダミー部にシリサイド層が形成されないように能動素子にシリサイド層190を形成する。

(もっと読む)

不揮発性半導体記憶装置、及びその製造方法

【課題】コストを抑えた不揮発性半導体記憶装置、及びその製造方法を提供する。

【解決手段】不揮発性半導体記憶装置は、ビット線BL0i〜BL2i、ビット線BL0i〜BL2iと交差するワード線WL0i、WL1i、及びビット線BL0i〜BL2i及びワード線WL0i、WL1iの交差部で両配線間に接続されたメモリセルMC0〜MC3を有する単位セルアレイMAT00を備える。さらに、不揮発性半導体記憶装置は、第1位置に設けられたビット線BL0iの側部に接し、第1位置よりも上方の第2位置に設けられたビット線BL1iまで積層方向に延びるコンタクトプラグCL1〜CL3と、第1位置と第2位置の間の第3位置に設けられたワード線WL0iの側部に接し、第2位置よりも上方の第4位置に設けられたワード線WL1iまで積層方向に延びるコンタクトプラグCL5、CL6とを備える。

(もっと読む)

半導体装置およびその製造方法

【課題】本発明は、裏面コンタクト電極と拡散層とのコンタクト抵抗が低減して、半導体装置の動作速度の向上を図ることを可能にする。

【解決手段】基板10の表面側に形成された拡散層25P、26P、25N、26Nと、前記拡散層25P、26P、25N、26Nの表面に形成されていて前記拡散層25P、26P、25N、26Nよりも抵抗が低い低抵抗部27P、28P、27N、28Nと、前記基板10の裏面側より前記基板10を貫通して前記拡散層25P、26P、25N、26Nを通して前記低抵抗部27P、28P、27N、28Nに接続された裏面コンタクト電極63P、64P、63N、64Nを有する。

(もっと読む)

半導体装置の製造方法

【課題】第1領域におけるライナー膜の膜厚と、第2領域におけるライナー膜の膜厚とが互いに異なる半導体装置において、コンタクトホールの形成時に、活性領域及び素子分離領域に削れが形成されることを防止する。

【解決手段】ゲート構造体Gbが密に配置された第1領域におけるライナー膜22b及び層間絶縁膜23に、互いに隣接するゲート構造体同士の間の領域を開口して、底部に第1の膜厚を有するライナー膜が残存する第1のコンタクトホール28rを形成する。次に、ゲート構造体が疎に配置された第2領域におけるライナー膜及び層間絶縁膜に、互いに隣接するゲート構造体同士の間の領域を開口して、底部に第2の膜厚を有するライナー膜が残存する第2のコンタクトホール34rを形成する。次に、第1のコンタクトホールの底部に残存するライナー膜、及び第2のコンタクトホールの底部に残存するライナー膜を除去する。第1の膜厚と第2の膜厚とは、同等である。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート電極とコンタクト配線のショート不良を防止できる半導体装置の製造方法を提供する。

【解決手段】半導体基板32上にゲートハードマスク、ゲート電極34及びゲート絶縁膜33を形成する。ゲートハードマスクの線幅をゲート電極よりも狭くした後、S/Dエクステンション36を形成する。全面にシリコン酸化膜を堆積形成し、エッチバックしてゲート電極の側壁から上面の一部上に渡って連続的に残存させた絶縁部材37を形成する。ゲートハードマスクを除去した後、ゲート電極と絶縁部材をマスクにしてコンタクトジャンクション38を形成する。金属シリサイド膜を形成後、シリコン窒化膜40と層間絶縁膜41を順次堆積形成する。層間絶縁膜にコンタクトホールを形成し、続いてシリコン酸化膜との選択比が高い異方性エッチングによってシリコン窒化膜を除去することでコンタクトホールを開孔し、コンタクト配線43を形成する。

(もっと読む)

141 - 160 / 612

[ Back to top ]