Fターム[5F033JJ11]の内容

半導体集積回路装置の内部配線 (234,551) | 層間接続のコンタクト層の材料 (22,060) | 金属及びその合金(シリサイドを除く) (14,566) | Cu (3,263)

Fターム[5F033JJ11]の下位に属するFターム

Cu合金 (406)

Fターム[5F033JJ11]に分類される特許

161 - 180 / 2,857

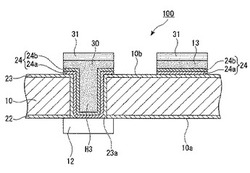

半導体装置、半導体装置の製造方法、回路基板および電子機器

【課題】電極パッドと貫通電極との接続面積を確保しつつ、下地膜が確実に形成される半導体装置、半導体装置の製造方法、回路基板および電子機器を提供する。

【解決手段】半導体基板10の能動面10a側に設けられた第一絶縁膜22と、第一絶縁膜22上に設けられた電極パッド12と、電極パッド12の形成位置に対応し、半導体基板10および第一絶縁膜22に形成された貫通孔H3と、貫通孔H3の少なくとも側面に設けられた第二絶縁膜23と、第二絶縁膜23と電極パッド12とを覆うように設けられた下地膜24と、下地膜24の内側で、貫通孔H3に埋め込まれた導電材料からなる貫通電極30と、を具備した半導体装置100において、貫通孔H3の側面と電極パッド12の裏面との角部23aに、第二絶縁膜23がフィレット状に形成されている。

(もっと読む)

半導体装置の製造方法

【課題】 低k膜と金属マスクとの間の界面に歪みを引き起こすことなく、高い精度の望ましいパターンを得ること。

【解決手段】 半導体装置を製造する方法では、金属マスクと絶縁マスクをと備える多層ハードマスクを用いて形成される配線層を含む半導体装置が形成される。第1パターンにアラインされた第2開口パターンを形成するために、第1ステップで多層ハードマスクが使用された後、金属マスクが除去され、絶縁マスクが、第2のステップで絶縁層中に第1のパターン構造を形成するために使用される。

(もっと読む)

めっき装置及び半導体装置の製造方法

【課題】ウェハの周縁部で膜を正常に成長させることができるめっき装置を提供する。

【解決手段】めっき槽2内部に取り付けられた第1電極6と、めっき槽2の側壁5cにおいて、環状のフランジ7cを介してめっき槽2の内から外に向けて直径の小さい順に隣接する環状の第1、第2の開口部7a,7bと、第2の開口部7b内でフランジ7cの上に取り付けられるシールパッキン8と、シールパッキン8の上に、第2の開口部7bの内壁から離れて取り付けられる環状の第2の電極9と、第2の電極9に対向する位置に周縁を有するウェハ保持領域11xを有する第2の開口部7bよりも大きなウェハステージ11と、ウェハステージ11のウェハ保持領域11xの周囲の領域に形成され、シールパッキン8に一端が向けられる加圧用ホール11iと、ウェハステージ11を移動してめっき槽2の側壁5cに押し当てて前記第2の開口部7bを閉塞させる駆動部13とを有する。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体基板の一表面上に絶縁膜を介して形成された導電層と、半導体基板の他面上に形成されたバンプ部と、導電層とバンプ部とを接続する半導体基板を貫通する貫通電極部とを有する半導体装置を提供する。

【解決手段】半導体基板の他面側から導電層に接続する貫通孔を形成し、貫通孔及び他面上にメタル膜(バリアメタル及びシードメタル)6を形成し、その上にフォトレジスト10を形成し、貫通孔より大きなパターンに加工してメッキマスク層を形成し、電解メッキ法により銅からなる第1メッキ膜7を形成して、貫通電極部と第1バンプ部を形成し、第1バンプ部上に第2バンプ部となる第2メッキ膜8を形成する。

(もっと読む)

複数の開口部を備える基板上への層の蒸着方法

【課題】多孔性低誘電率絶縁膜のトレンチおよびビア内にカバレージ良くライニング層を形成する半導体装置の製造方法を提供する。

【解決手段】第1パルス期間に供給される第1反応物と、第2パルス期間に供給される第2反応物とを利用する原子層堆積(ALD)プロセスにより成膜する。まずシーリング層を低コンフォマリティーを有する条件で成膜し、ポアをブロックする。この後、接着層を高いコンフォマリティーを有する条件で成膜する。

(もっと読む)

半導体装置およびその製造方法、並びに表示装置

【課題】3層以上の配線を接続する際に、最も効率的にかつ最小面積で接続を行えるコンタクト構造を実現可能な半導体装置およびその製造方法、並びに表示装置を提供する。

【解決手段】基板201上に3層以上のn層の導電層202〜204が積層して形成され、n層の導電層がコンタクトパターンを介して接続され、コンタクトパターンが形成される一つの主コンタクト領域には、(n−1)個の導電層202,203を接続する(n−1)個の接続領域211,212を有し、(n−1)個の導電層のうち基板201に対する積層方向(基板201の主面に対する法線方向)において第1層より上層の導電層は、その終端部がコンタクトパターンCPTNの縁の一部に臨むように形成され、(n−1)個の導電層は、第n層の導電層により電気的に接続されている。第n層の導電層は、コンタクトパターンCPTNであるコンタクト孔を埋めつくよう形成されている。

(もっと読む)

無電解薄膜析出法により平坦化銅相互接続層を形成する方法および装置

【課題】基板に定形された形態部の内部に、表面が平坦化された導電性材料を形成する方法を提供する。

【解決手段】平坦化表面を形成する方法であって、狭小形態部と幅広形態部が形成された基板上に、第1のプロセスでは電気めっき法により狭小形態部および幅広形態部の少なくとも一部を充填し、第1の層を形成し、第2のプロセスでは無電解めっき法により幅広形態部のに対応する第1の層中の孔および第1の層上に第2の層を充填形成し、表面が平坦な上層部110を形成する。

(もっと読む)

キャパシタおよび半導体装置

【課題】キャパシタの電極として機能する配線の延伸方向への電流供給を容易とすること。

【解決手段】第1金属層12と、前記第1金属層の膜厚方向に離間して設けられ、第1方向および前記第1方向に交差する第2方向に配列された複数の孔36を備えた第2金属層14と、前記第2金属層の膜厚方向で前記第1金属層とは反対側に離間して設けられ、前記第1方向および前記第2方向とは異なる方向に延伸し、第1配線と第2配線とが交互に設けられた複数の第1配線16aおよび複数の第2配線16bと、前記複数の第1配線と前記複数の第2配線との間に設けられた誘電体膜26と、前記複数の第1配線を、それぞれ前記複数の孔を通過し前記第1金属層に電気的に接続する複数の第1ビア配線32と、前記複数の第2配線を、それぞれ前記第2金属層に電気的に接続する複数の第2ビア配線34と、を具備するキャパシタ。

(もっと読む)

半導体装置、半導体装置の製造方法、固体撮像装置及び電子機器

【課題】 ビア形成時のエッチングによる基板や配線への影響を抑制しつつ積層された半導体ウェハの回路どうしを接続する。

【解決手段】 半導体装置の製造方法は、第1基板と第1基板の一面と接するように形成された第1絶縁層を有する第1の半導体ウェハと、第2基板と第2基板の一面と接するように形成された第2絶縁層を有する第2の半導体ウェハを接合する工程と、第1基板の他面に第3絶縁層を形成する工程と、第3絶縁層、第1基板、及び第1絶縁層を貫通し第2絶縁層に形成された第2の配線上に第2絶縁層が残るようにエッチングを行い第1接続孔を形成する工程と、第1接続孔に絶縁膜を形成する工程と、第2の配線上の第2絶縁層及び絶縁膜のエッチングを行い第2接続孔を形成し第2の配線を露出させる工程と、第1及び第2接続孔の内部に形成され第2の配線と接続する第1のビアを形成する工程とを備え、第1基板の他面に形成された第1接続孔の径は第3絶縁層に形成された前記第1接続孔の径より大きい。

(もっと読む)

電子部品、電子部品の製造方法、基板

【課題】チッピング検出用配線が他の部材で覆われている状態であっても、ダイシングによって電子部品を形成した後に、チッピング検出用配線の導通状態を検出するための電圧を印加できる基板を提供する。

【解決手段】電子部品40は、互いに平行を成す一方の主面41aと他方の主面41bが矩形状の基体41を有する。基体41の一方の主面41aには、第一チッピング検出用配線42が配されている。また、基体41の他方の主面41bには、第二チッピング検出用配線44が配されている。第一チッピング検出用配線42は貫通配線43aを介して第二チッピング検出用配線44に電気的に接続される。

(もっと読む)

容量素子および半導体装置

【課題】容量素子のQ値(Quality Factor)特性を向上する。

【解決手段】容量素子は、互いに対向する一対の電極EL10、EL20と、一対の電極の一方の電極に設けられ、一方の電極の両端部から間隔を置いて配置された第1端子部とTE10、一対の電極の他方の電極に設けられ、他方の電極の両端部から間隔を置いて配置された第2端子部とTE20を有している。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】信頼性に優れた半導体装置を提供する。

【解決手段】半導体装置の製造方法は、主面に複数の埋込導電部(埋込導電部106)が設けられたシリコンウエハ102と、シリコンウエハ102の主面に配置された、埋込導電部106に電気的に接続する複数の第1の半導体素子(半導体チップ108)と、を備える構造体を用意する工程と、半導体封止用樹脂組成物を用いて、シリコンウエハ102の主面上の複数の半導体チップ108を封止する封止材層110を形成する工程と、シリコンウエハ102の裏面を研削して、裏面に埋込導電部106を露出させて、貫通プラグ105とする工程と、を含む。

(もっと読む)

半導体装置の製造方法

【課題】本実施形態は、コンタクトプラグの抵抗の低減を行うことができる半導体装置の製造方法を提供する。

【解決手段】本実施形態の半導体装置の製造方法は、基板にコンタクトホール又はコンタクトトレンチを形成し、コンタクトホール又はコンタクトトレンチの底に、アモルファスシリコン層又は多結晶シリコン層を形成し、アモルファスシリコン層又は多結晶シリコン層を覆うように不純物を含むニッケル膜を形成し、加熱することによりニッケル膜とアモルファスシリコン層又は多結晶シリコン層とを反応させて、ニッケルシリサイド膜を形成し、コンタクトホール又はコンタクトトレンチを埋め込むようにコンタクト金属膜を形成する。

(もっと読む)

下地導電層付き基板の製造方法および貫通電極基板の製造方法

【課題】製造時間とコストの大幅な削減が可能な下地導電層付き基板および貫通電極基板の製造方法を提供する。

【解決手段】厚さ方向に複数の貫通孔2を有するガラス基板3の貫通孔2内に下地導電層4を有する基板の製造方法であって、前記ガラス基板3の貫通孔2内に、金属粒子と分散媒とを含有する流動性の導電性組成物(金属インク)の層を形成する工程と、この導電性組成物の層を加熱して、貫通孔2の内壁面に金属粒子の金属を主体とする下地導電層4を形成する工程とを備える方法である。貫通電極基板5の製造方法は、こうして形成された下地導電層4上に電解めっき等により導電性金属の層を形成して、貫通孔2内に充填された貫通電極6を形成する工程を有する。

(もっと読む)

半導体装置及びその製造方法

【課題】配線抵抗を低減することのできる半導体装置を提供する。

【解決手段】一の実施の形態に係る半導体装置は、半導体基板と、半導体基板上にそれぞれ設けられた第1の領域及び第2の領域とを備える。第1の領域は、半導体基板上の第1配線層に形成され、所定の第1の幅を有する第1の金属配線と、第1配線層の上層の第2配線層に形成され第1の幅を有する第2の金属配線と、第1の金属配線と第2の金属配線とを接続し、第1の幅以下の第2の幅を有する第1のコンタクトとを有する。第2の領域は、第1配線層から第2配線層へと亘る膜厚を有し、所定の第3の幅を有する第3の金属配線を有する。

(もっと読む)

半導体装置

【課題】複数のスパイラルを直列に接続してインダクタを形成する場合において、スパイラルを大面積化することなく、スパイラルの巻線を長くする。

【解決手段】インダクタ10は、第1スパイラル100及び第2スパイラル200を有している。第1スパイラル100は、インダクタ10の巻軸と平行な第1の方向から見た場合、中心から外側に向かって巻かれている。第2スパイラル200は、第1の方向から見た場合、外側から中心に向かって、第1スパイラル100と同一の向きに巻かれている。第1スパイラル100及び第2スパイラル200は、外側の端部同士、または中心側の端部同士が、外側接続部材300又は中心側接続部材400を介して接続されている。第2スパイラル200は、第1スパイラル100を、巻軸を回転中心として右回りに90°回転させてから、巻軸に直交する平面に含まれる水平線を基準に鏡映させ、かつ縦横比を変更した形状である。

(もっと読む)

配線膜、薄膜トランジスタ、ターゲット、配線膜の形成方法

【課題】信頼性の高い薄膜トランジスタを提供する。

【解決手段】薄膜トランジスタ20のゲート電極15、ソース、ドレイン電極33、34のうち、いずれか一つ以上の電極はバリア膜25を有し、バリア膜25が成膜対象物21又は半導体層30に密着している。NiとMoを100原子%としたときに、バリア膜25は、Moを7原子%以上70原子%以下含有し、ガラスからなる成膜対象物21や半導体層30に対する密着性が高い。また、バリア膜25表面にCuを主成分とする金属低抵抗層26が形成された場合に、Cuが半導体層30に拡散しない。

(もっと読む)

半導体チップ

【課題】金属原子の拡散に起因する素子特性の劣化を抑制する。

【解決手段】半導体チップは、半導体基板10と、半導体基板10を貫通する貫通電極20と、半導体基板10を貫通する金属柱40と、アライメントマーク47と、絶縁性を有する筒状の絶縁膜50とを有する。アライメントマーク40は、半導体基板10の外部に露出した金属柱40の端部によって形成されている。筒状の絶縁膜50は、半導体基板10に形成されており、金属柱40を取り囲んでいる。

(もっと読む)

半導体装置

【課題】伝送線路を接続するビア層の周囲のグラウンドを強化することができると共に、ビア部の特性インピーダンスを調整することが可能な半導体装置を提供する。

【解決手段】絶縁層14を介して積層された第1の半導体基体11及び第2の半導体基体21と、第1の半導体基体11に形成され、信号線12とグラウンド13とを含む第1の伝送線路と、第2の半導体基体21に形成され、信号線22とグラウンド23とを含む第2の伝送線路と、第1の伝送線路の信号線12及び第2の伝送線路の信号線22に接続された信号線用のビア層と、第1の伝送線路のグラウンド13及び第2の伝送線路のグラウンドに接続された、グラウンド用の第1のビア層と、第2の伝送線路のグラウンド23に接続され、かつ、信号線用のビア層に対向して形成された帯状のビア層を含む、グラウンド用の第2のビア層16を有する半導体装置を構成する。

(もっと読む)

半導体装置

【課題】とりわけ表面マークの下部に配線タングステンパッドがある場合でも、表面マークのコントラスト低下を抑制する。

【解決手段】メモリチップ31は、配線タングステン階層WTL、第1、第2、第3アルミニウム配線階層1AlL,2AlL,3AlLを備える多層配線構造を備える。各配線層の間には、第1、第2、第3層間絶縁膜315,316,317がそれぞれ形成され、第3アルミニウム配線階層3AlLとポリイミド膜PIとの間には、第4層間絶縁膜318が形成されている。第1のダミーパターンDP1は、第1アルミニウム配線階層1AlLに形成され、第2層間絶縁膜316に覆われている。第2のダミーパターンDP2は、第2アルミニウム配線階層2AlLに形成され、第3層間絶縁膜317に覆われている。第2ダミーパターンDP2は、第1ダミーパターンDP1よりも幅が長い。

(もっと読む)

161 - 180 / 2,857

[ Back to top ]