Fターム[5F033JJ11]の内容

半導体集積回路装置の内部配線 (234,551) | 層間接続のコンタクト層の材料 (22,060) | 金属及びその合金(シリサイドを除く) (14,566) | Cu (3,263)

Fターム[5F033JJ11]の下位に属するFターム

Cu合金 (406)

Fターム[5F033JJ11]に分類される特許

201 - 220 / 2,857

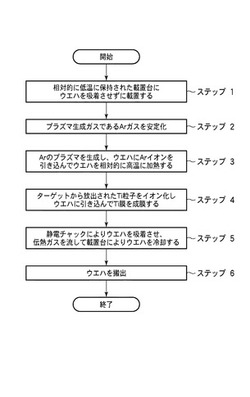

成膜方法およびCu配線の形成方法

【課題】被処理基板を加熱してトレンチやホールの間口部のオーバーハングを抑制しつつ金属膜を成膜するとともに、成膜後に速やかに被処理基板の温度を低下させることができる成膜方法を提供すること。

【解決手段】載置台を低温に保持して、載置台上に被処理基板を吸着させずに載置する工程と、プラズマ生成ガスのプラズマを生成し、載置台に高周波バイアスを印加した状態で、被処理基板にプラズマ生成ガスのイオンを引きこんで被処理基板を予備加熱する工程と、ターゲットに電圧を印加して金属粒子を放出させ、プラズマ生成ガスのイオンとともにイオン化した金属イオンを被処理基板に引きこんで金属膜を形成する工程と、被処理基板を低温に保持された載置台に吸着させ、載置台と被処理基板との間に伝熱ガスを供給して被処理基板を冷却する工程とを有する。

(もっと読む)

半導体装置及び半導体装置の製造方法。

【課題】半導体基体同士が張り合わされた構成を有する半導体装において、接合精度の向上を可能とする。

【解決手段】第1半導体基体31と、第2半導体基体45とを備え、第1半導体基体31の第1主面31A側と、第2半導体基体45の第1主面45A側が接合されている。そして、第1半導体基体31の第1主面31A側、第2半導体基体45の第1主面45A側、第1半導体基体31の第2主面31B側、及び、第2半導体基体45の第2主面45B側から選ばれる少なくとも1つ以上に形成されている反り補正層13,14を備える半導体装置79を構成する。

(もっと読む)

半導体装置の製造方法

【課題】 金属部材の表面に、再現性よくバリア膜を形成する技術が望まれている。

【解決手段】 基板の上に、下部バリア膜を形成する。下部バリア膜の上にシード膜を形成する。シード膜の一部の領域上に、導電部材を形成する。導電部材をエッチングマスクとして、シード膜をエッチングし、導電部材の形成されていない領域において、下部バリア膜を露出させる。下部バリア膜の表面には堆積しない条件で、導電部材の表面に選択的に上部バリア膜を成長させる。上部バリア膜をエッチングマスクとして、下部バリア膜をエッチングする。

(もっと読む)

回路基板の製造方法

【課題】絶縁膜に形成されるヴィアホールの直径を縮小化することが可能で、高密度化に寄与することのできる回路基板の製造方法を提供する。

【解決手段】本発明の回路基板の製造方法は、基板10上に第1導電体を形成する第1導電体形成工程と、第1導電体を被覆する様にゲート絶縁膜21を成膜する第1絶縁膜成膜工程と、第1導電体上のゲート絶縁膜21に貫通孔32を開口して、当該貫通孔32を介して第1導電体の表面および基板の表面を部分的に露出させる貫通孔形成工程と、貫通孔32内に露出する第1導電体の表面を撥液化させる撥液化工程と、貫通孔32内に露出する第1導電体以外の領域に第2絶縁膜を形成する第2絶縁膜形成工程と、を含むことを特徴とする。

(もっと読む)

半導体基板、その製造方法、および電子装置

【課題】カーボンナノチューブを用いた特性が良好な半導体基板、その製造方法、および電子装置を提供することにある。

【解決手段】

本発明の一態様による半導体基板は、一主面に下部電極を有する基板と、前記基板上の前記下部電極以外の部分に設けられた層間絶縁膜と、前記下部電極の上に設けられた触媒層と、前記触媒層上に設けられ、前記下部電極の一主面に垂直な方向に延伸する複数のカーボンナノチューブと、前記カーボンナノチューブ上に設けられ、前記下部電極と対向する上部電極と、前記触媒層および前記カーボンナノチューブの前記触媒層側の端部を覆う第1の埋め込み膜と、前記カーボンナノチューブの他端部の間に満たされ、前記第1の埋め込み膜よりも高密度のである第2の埋め込み膜と、を有する。

(もっと読む)

半導体チップ及びその製造方法、並びに半導体装置

【課題】ダイシング工程で発生し得る裏面側のチッピングが、貫通電極が存在するアクティブエリアにまで侵入することを防止する。

【解決手段】メモリチップ1Aは、スクライブセンターSC側から、スクライブエリアSA、ガードリングエリアGA、及びアクティブエリアAAという領域に区分けされる。スクライブエリアSAの層間絶縁膜内には、メモリチップ1Aの表面側のチッピングを防止するための第1、第2クラックストップ3a,3bが設けられている。ガードリングエリアGAの表面側には、ガードリング4が設けられている。一方、ガードリングエリアGAの半導体基板10側(メモリチップ1Aの裏面側)には、裏面側のチッピングを防止するための溝5Aが設けられている。この裏面チッピング防止溝5Aによって、チッピングがサポート貫通電極2a及び信号等用貫通電極が形成されている領域に侵入することを防ぐことができる。

(もっと読む)

半導体装置の製造方法

【課題】信頼性の高い半導体装置を提供する。

【解決手段】基板上に設けられた層間絶縁膜40に開口部48を形成する工程と、開口部48の側面上および底面上、ならびに層間絶縁膜40上に第1金属材料からなる第1膜10を形成する工程と、第1膜10上であって、開口部48内および層間絶縁膜40上に、第1金属材料よりも電気陰性度が小さい第2金属材料からなる第2膜20を形成する工程と、第2膜20上に、第2金属材料よりも電気陰性度が小さい第3金属材料からなる第3膜30を形成する工程と、熱処理する工程と、開口部48外に位置する第1膜10および第2膜20、ならびに第3膜30を研磨によって除去する工程と、を備える。

(もっと読む)

自己整合シリサイドの形成方法、半導体デバイスの製造方法、および半導体構造物

【課題】製造工程の増大を抑制し、コンタクト抵抗および界面抵抗の増大を防止する。

【解決手段】実施形態において、シリコン層は、ゲートラストスキームを用いた機能的ゲート電極の製造後に、形成される。初期的な半導体構造物は、半導体基板上に形成された少なくとも一つの不純物領域、不純物領域の上に形成された犠牲膜、犠牲膜の上に形成された絶縁層、絶縁層の上に形成された絶縁層を備える。ビアは、初期の半導体構造物の絶縁層へ、および、コンタクト開口部が絶縁層に形成されるように絶縁層の厚さを通り抜けて、パターン化される。次に、絶縁層の下にある犠牲膜は、絶縁層の下に空隙を残して除去される。次に、金属シリサイド前駆体は、空隙スペースに配置され、金属シリサイド前駆体は、アニールプロセスを通じてシリサイド層に変換される。

(もっと読む)

半導体装置およびその製造方法

【課題】結晶欠陥が可及的に少なく、従来よりも抵抗率の低い高質のグラフェンを備えた半導体装置を提供する。

【解決手段】半導体装置は、半導体基板と、前記半導体基板の上方に設けられた配線とを具備する。前記助触媒層のうち前記触媒層と接触している部分は、面心立方構造もしくは六方最密構造を有し、かつ、前記面心立方構造の(111)面もしくは前記六方最密構造の(002)面が前記半導体基板の表面と平行になるように配向しているか、または、前記助触媒層のうち前記触媒層と接触している部分は、アモルファス構造もしくは微結晶構造を有する。前記触媒層は、面心立方構造もしくは六方最密構造を有し、かつ、前記面心立方構造の(111)面もしくは前記六方最密構造の(002)面が前記半導体基板の表面と平行になるように配向する。

(もっと読む)

薄膜の成膜方法

【課題】基板上への薄膜の成膜速度を上げ、かつトレンチやビアホールの底面に効率よく薄膜を成膜できる薄膜の形成方法を提供すること。

【解決手段】本発明の成膜方法は、開口幅又は開口径が3μm以下で、かつ、アスペクト比が1以上の段差であるトレンチ又はビアホールを有する基板上に薄膜を成膜する成膜方法であり、真空排気可能な処理室に、基板を支持する第1の電極と、前記基板に対向するように配置されターゲットを支持する第2の電極と、前記第2の電極の外側に配置されて当該第2の電極の内側にカスプ磁界を形成する複数のマグネットと、を備え、

前記処理室にNeを含む処理ガスを導入し、前記第1の電極と前記第2の電極の少なくとも一方にプラズマ形成用の高周波電力を供給すると共に、前記第2の電極上にカスプ磁場を生成してプラズマを発生させ、ターゲット物質をトレンチ又はビアホールを有する基板上に成膜する。

(もっと読む)

半導体装置

【課題】容量素子を備え、電気的特性の安定化が可能な半導体装置を提供する。

【解決手段】半導体基体1上の配線層に形成されている配線と絶縁層とからなる容量素子10を備える。そして、容量素子10の形成領域内の半導体基体11上に形成されている導体パターンと、導体パターンの電位を固定するための電位固定端子28とを備える半導体装置を構成する。

(もっと読む)

半導体装置の製造方法、及び半導体装置

【課題】微細配線においてボイドの発生を確実に防ぐ。

【解決手段】層間絶縁膜102、103に形成された開口部12の底面及び側壁、並びに、開口部12以外の層間絶縁膜103上にあるフィールド部に、第一の金属を含むシード膜を形成し、シード膜上にレジストを形成して、開口部12をレジストで埋め込んだ後、開口部12の底面上に形成されたシード膜にレジストを残しつつレジストの一部を除去して、開口部12の側壁202A、Bの上部からフィールド部203にわたって形成されたシード膜を露出させ、開口部12の側壁の上部、及び、フィールド部203に位置するシード膜上に、第一の金属よりも抵抗率が高い第二の金属を含むカバー膜を形成した後、レジストを除去してシード膜を露出させ、露出させたシード膜に、第一の金属を含むめっき膜を形成するものである。

(もっと読む)

素子付き基板、赤外線センサー、および貫通電極形成方法

【課題】マイグレーションの問題を生じることなく、微細でアスペクトの高く絶縁特性に優れた絶縁膜を備えた貫通電極を有する素子付き基板、赤外線センサーおよび貫通電極形成方法を提供する。

【解決手段】予め、素子回路形成前のベース基板にビアホールを形成し、前記ベース基板の素子回路形成面と前記ビアホールの内面に熱酸化により絶縁膜を形成する熱酸化を行なう。前記熱酸化工程後に前記ビアホール形成部に導電部を有する素子回路を形成した後、前記素子回路形成工程後に前記ビアホールに導電体を埋め込み形成するようにしている。

(もっと読む)

基板処理方法および記憶媒体

【課題】 変性処理およびその後の溶解処理によるダメージにより低誘電率膜のk値が上昇した場合にも十分にk値を回復させることができる基板処理方法を提供すること。

【解決手段】 低誘電率膜をエッチング処理して所定パターンを形成し(ステップ3)、エッチング処理を終了した後に残存する物質を所定の液に対して可溶化するように変性し(ステップ8)、ステップ8の後、パターンが形成された低誘電率膜の表面にシリル化剤を供給し、ステップ8の際に低誘電率膜に入ったダメージを回復するためのシリル化処理をし、変性された物質を溶解除去し(ステップ9)、ステップ9の後、パターンが形成された低誘電率膜の表面にシリル化剤を供給し、ステップ9の際に低誘電率膜が受けたダメージを回復するためのシリル化処理をし(ステップ10)、ステップ10の後、基板をベークしてシリル化処理後の低誘電率膜の比誘電率を下げる(ステップ11)。

(もっと読む)

半導体装置及びその製造方法

【課題】コンタクトホール内にめっき層から成るコンタクト層を埋め込んで上下層の電気的接続を行うときの、コンタクト層の埋め込み性を良好にする構造の半導体装置を提供する。

【解決手段】配線層12,16と、少なくとも底部において、三角形の平面形状であるコンタクトホール14と、めっき層から成り、コンタクトホール14の内部を埋めて形成され、配線層12,16に接続されたコンタクト層15とを含む、半導体装置を構成する。

(もっと読む)

銅結線のシード層の処理方法および処理装置

【課題】ダマシンプロセスによる銅の充填において、銅シード層の完全性を失わないように行う。

【解決手段】誘電体層に半導体結線形状を形成するための方法は、誘電体層上に形成された形成されたバリア層上、および誘電体層のエッチング形状内に、銅シード層を蒸着する工程を含む。次いで、銅シード層は、酸化された層を銅シード層から除去するために処理を施される。次いで、その方法は、処理された銅シード層上に銅充填層を電気メッキする工程に進む。銅充填層は、誘電体層のエッチング形状を満たすよう構成されている。

(もっと読む)

光電変換装置、撮像システム及びその製造方法

【課題】 フローティングディフュージョン部の容量の増大を抑制することが可能な光電変換装置を提供する。

【解決手段】 光電変換素子と、フローティングディフュージョン部と、転送トランジスタと、増幅トランジスタとが配された半導体基板と、第1の配線層と、第2の配線層とを含む複数の配線層と、を有する光電変換装置において、転送トランジスタのゲート電極と、前記第2の配線層とがスタックコンタクト構造で接続されている。

(もっと読む)

半導体装置、電子デバイス及び電子デバイスの製造方法

【課題】対向するバンプ、パッド等を良好に接続し、接続部分の水平強度を高めるための半導体装置を提供する。

【解決手段】半導体基板2の上方に形成される第1絶縁膜15と、第1絶縁膜15内に形成される導電パターン19と、第1絶縁膜15上に形成される第2絶縁膜21と、第2絶縁膜21内に形成され、導電パターン19に接続されるビアプラグ24と、記ビアプラグ24の上に接続され、開口部25aを有する電極パッド25と、第2絶縁膜21内でビアプラグ24の周辺に形成される内部空間21aとを有し、電極パッド25上面及び開口部25a内には外部の突起状電極58が接続される。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】貫通孔の側面のスキャロップ形状及びアンダーカットを修復する。

【解決手段】半導体装置は、第1の基板と、第2の基板と、前記第1の基板と前記第2の基板との間に配置され、前記第1の基板と前記第2の基板とを接着する接着層と、を備え、前記第2の基板及び前記接着層には、前記第2の基板及び前記接着層を貫通する貫通孔が形成されており、前記貫通孔の側面には、凹部が形成されており、前記凹部には、少なくとも有機骨格を有する樹脂が埋め込まれており、前記貫通孔の中には、導電体が形成されている。

(もっと読む)

半導体集積回路装置およびその製造方法ならびにそれを用いた電子システム

【課題】再配線のランド部にバンプ電極が接続された半導体集積回路装置において、再配線と半田バンプとの接着強度を向上させる。

【解決手段】再配線20のランド部20Aは、再配線20を構成する5層の金属膜(バリアメタル膜13、シード膜14、Cu膜15、第1Ni膜16および第2Ni膜17)のうち、最上層の第2Ni膜17の面積が他の金属膜(バリアメタル膜13、シード膜14、Cu膜15、第1Ni膜16)の面積よりも大きくなるように構成され、この第2Ni膜17の表面に半田バンプ21が接続されている。そして、半田バンプ21の端部では、第2Ni膜17の直下にポリイミド樹脂膜22が形成されている。

(もっと読む)

201 - 220 / 2,857

[ Back to top ]