Fターム[5F033JJ14]の内容

半導体集積回路装置の内部配線 (234,551) | 層間接続のコンタクト層の材料 (22,060) | 金属及びその合金(シリサイドを除く) (14,566) | Ag、Ag合金 (479)

Fターム[5F033JJ14]に分類される特許

81 - 100 / 479

半導体集積回路装置の製造方法

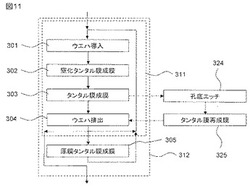

【課題】信頼性の高い半導体集積回路装置の製造プロセスを提供する。

【解決手段】銅ダマシン配線プロセスのバリアメタル膜のタンタル系積層膜に関し、スパッタリング成膜チャンバ内のシールド内面に、比較的薄い窒化タンタル膜およびタンタル膜が交互に成膜されるが、この連続成膜プロセスを断続的に繰り返すと、膜の内部応力により剥がれて、異物やパーティクルの原因となる。この異物やパーティクルの防止のため、繰り返し、成膜するに際して、所定の間隔を置いて、厚い膜厚を有する異物防止用タンタル膜をチャンバの実質的な内壁に成膜する工程を設ける。

(もっと読む)

半導体装置

【課題】 貫通穴の開口寸法が小さく小型化や微細化を容易にでき、貫通穴全体の金属層形成速度を向上する事が容易で、金属層形成工程に要する時間を短縮する事が容易な貫通穴形状を構成した半導体装置を提供することを目的とする。

【解決手段】 基板の表面と裏面とを接続する貫通穴内に金属層を設けた半導体装置において、貫通穴側壁に表面と裏面とを結ぶ向きに複数の突起を設けた事を特徴とする。

(もっと読む)

回路基板及び電子デバイス

【課題】導体の亀裂、基板のクラック、絶縁膜の破壊等を生じ難い高信頼度・高品質の回路基板及び電子デバイスを提供する。

【解決手段】基板1と、導体3とを含んでおり、導体3は、金属または合金でなり、基板1に設けられ、少なくとも基板1と対面する領域に、等軸晶31の領域を有する。この構造によれば、基板1と対面する領域で、導体3の等軸晶組織による等方性が得られるため、導体3の亀裂、絶縁膜の破壊及び基板1のクラックなどの発生が抑制される。

(もっと読む)

半導体装置の製造方法

【課題】フォトリソグラフィ法の露光解像限界未満のラインアンドスペースパターンとなる被加工膜のパターンの上層に、その被加工膜のパターンと接続するコンタクトを容易に形成することができる半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、半導体基板上に形成された第2の膜14を、複数の線状部とそれぞれの線状部の一端に形成された線状部よりも幅の広い端部を有するパターンへと加工し、このパターンをスリミングして第1のパターン16を形成し、第1のパターン16の端部141a上を横断する第1の開口180を有する第2のパターンを形成し、第1の開口180内に露出する第2の膜14をエッチングし、端部141aを線状部140aに近い第1の端部142aと、線状部140aと遠い第2の端部143aとに分割することを含む。

(もっと読む)

半導体ダイのコンタクト構造および方法

【課題】他の物体によって損傷、剥離、または亀裂を生じることなく、より粗野な処理、運送、および使用を可能にするよりよい緩衝を、半導体デバイスの金属化層に配置された低k誘電体層、ELK誘電体層、および/またはULK誘電体層の半導体ダイのコンタクトを形成するシステム、方法を提供する。

【解決手段】複数の誘電体層および導電層を含む基板101、複数の導電層の最上層115の1つと電気的に接続し、約15,000Åより大きい厚さを有する金属コンタクト105、および金属コンタクトと電気的に接続したコネクタを含む半導体デバイス。

(もっと読む)

金属の付着

システム及び方法が、電圧切り換え可能な誘電体材料に1つ以上の材料を付着させることを含む。特定の態様では、電圧切り換え可能な誘電体材料が、導電バックプレーン上に配置される。いくつかの実施形態では、電圧切り換え可能な誘電体材料が、付着に関する特性電圧が相違する複数の領域を含む。いくつかの実施形態は、マスキングを含み、取り除くことが可能なコンタクトマスクの使用を含むことができる。特定の実施形態は、電気グラフトを含む。いくつかの実施形態は、2つの層の間に配置される中間層を含む。 (もっと読む)

単結晶基板

【課題】直線状又は螺旋状の深い孔を有する単結晶基板を低コストで提供する。

【解決手段】単結晶基板1は、主成分がシリコンからなり、<100>方向に孔3が形成されており、その孔の底に銀粒子及び/又はパラジウム粒子が存在し、孔径/粒子径の比が1以上2以下であることを特徴とする。また、単結晶基板1は、主成分がシリコンからなる単結晶基板であって、孔径10〜200nm、螺旋径100〜600nmの螺旋状の孔が形成されており、その孔の底に銀、白金及びパラジウムのうちから選ばれる一種以上の金属の微粒子が存在することを特徴とする。

(もっと読む)

高温印刷部分と低温印刷部分の2つの部分を有する光起電力電池導体

半導体材料(1)上に少なくとも1つの導体を形成する方法は、(E1)−シルクスクリーン印刷によって第1の高温ペーストを堆積させるステップと、(E2)−前のステップの間に堆積された第1の高温ペーストに少なくとも部分的に重ねて、シルクスクリーン印刷によって、低温ペーストを堆積させるステップとを有する。 (もっと読む)

電極基板の製造方法、電極基板、及び薄膜トランジスタ

【課題】製造工程の複雑化と製造コストの高価格化を招くことなく、多層電極間の接続を容易に行うことが可能な電極基板の製造方法、電極基板、及び薄膜トランジスタを提供する。

【解決手段】下地層の上に、下層電極、層間絶縁膜、上層電極がこの順番で積層され、下層電極と上層電極とが層間絶縁膜に形成された開口部を介して電気的に接続された電極基板の製造方法であって、下地層の上に、電極材料を含有する溶液を塗布した後、乾燥させて下層電極を形成する工程と、下層電極が形成された下地層の上に、開口部を有する層間絶縁膜を形成する工程と、開口部に溶液の溶媒を滴下し、開口部に位置する下層電極を溶解した後、乾燥させることにより、電極材料を開口部の内壁に沿ってコーヒーステイン形状に形成する工程と、電極材料が開口部の内壁に沿ってコーヒーステイン形状に形成された層間絶縁膜の上に上層電極を形成する工程と、を有する。

(もっと読む)

半導体ダイにおける応力を軽減するためのルーティング層

【解決手段】

半導体ダイのためのルーティング層が開示される。ルーティング層は、半田バンプを取り付けるためのパッドと、集積回路を有するダイのバンプパッドにボンディングされるボンドパッドと、ボンドパッドをパッドと相互接続するトレースと、を含む。ルーティング層は誘電体材質の層上に形成される。ルーティング層は、パッドに取り付けられる半田バンプからの応力を吸収するように、幾つかのパッドを少なくとも部分的に包囲する伝導性トレースを含む。パッドを包囲するトレースの一部は、半田バンプに隣接する下層の誘電体材質の一部を応力から保護する。

(もっと読む)

半導体装置の製造方法、半導体装置

【課題】ダイシング時で半導体チップに発生するチッピング、割れ、或いは欠けを低減する。

【解決手段】半導体装置80は、半導体チップ50がガラス基板60にFace Downして載置され、接着層10で半導体チップ50とガラス基板60が接着される。半導体チップ50には、シリコン基板1、集積回路部2、受光部3、層間絶縁膜4、樹脂層5、表面電極6、貫通電極8、裏面電極9、裏面保護膜12、ボール端子13が設けられる。樹脂層5は、シリコン基板1上に層間絶縁膜4と接するように半導体チップ50の端部に設けられる。樹脂層5は、層間絶縁膜4をエッチングした開口領域に設けられる。半導体装置80は、接着層10により固着されたシリコンウェハ100とガラス基板60をブレードダイシングにより個片化されたものである。

(もっと読む)

回路基板の貫通電極の形成方法

【課題】基板上の微細な貫通孔へ貫通電極となる金属を充填する方法であって、基板への熱的影響を軽減することができ、且つ、効率的な製造を可能とする方法を提供する。

【解決手段】本発明は、貫通孔を有する基板の貫通孔に導電性金属を充填する貫通電極の形成方法であって、所定の純度及び粒径の金属粉と有機溶剤とからなる金属ペーストを用いるものである。このとき、金属ペーストに周波数60Hz〜100kHzの機械的振動を印加しながら基板に塗布し、金属ペーストの塗布と同時、又は、金属ペーストの塗布後に貫通孔を他端側から減圧して金属ペーストを貫通孔内に吸引し、その後金属ペーストを焼結して貫通電極とする。この金属ペーストの塗布は、機械的振動が印加されたブレードを基板と非接触な状態で移動させることが好ましい。

(もっと読む)

半導体装置及びその製造方法

【課題】高い実装信頼性が得られる半導体装置及びその製造方法を提供する。

【解決手段】半導体装置は、半導体構造部13、14と、半導体構造部の主面側に設けられた配線層16、17と、配線層における半導体構造部が設けられた面の反対側の面に設けられ、配線層と電気的に接続された電極パッド21、22と、電極パッド21、22に対して各々が互いに離間して接合された複数の金属ピラー31と、複数の金属ピラー31の先端部に共通に設けられた外部端子41とを備え、個々の金属ピラー31の径が外部端子41の径よりも小さい。

(もっと読む)

光学装置および光学装置の製造方法

【課題】より効率良く光学装置を製造できる光学装置の製造方法を提供すること。

【解決手段】 複数の光学素子1を備える光学素子シート6を、配線パターン3が形成された基板シート7に接合する工程と、上記接合する工程の後に、光学素子シート6を切断することにより、複数の光学素子1どうしを分離する工程と、上記接合する工程の後に、基板シート7を切断することにより、光学素子1と接合している配線基板を形成する工程と、を備える。

(もっと読む)

半導体素子およびその製造方法

【課題】ウェットエッチングにより形成される配線の線幅のばらつきが抑えられた半導体素子を提供する。

【解決手段】半導体素子の製造方法は、半導体層14上に電極11を形成する工程と、半導体層14上に、電極11に達する配線接続孔12aを有し、配線接続孔12aの周りに凹部12bが形成された層間絶縁膜12を形成する工程と、層間絶縁膜12上から配線材料18を堆積する工程であって、層間絶縁膜12の凹部12bに対応して配線材料18に凹部18aが形成される工程と、配線材料18上に、電極11に配線接続孔12aを介して接続される配線13を形成するためのレジスト膜19を、配線材料18に形成された凹部18aを覆うように形成する工程と、レジスト膜19をマスクとしてウェットエッチングを行い、配線材料18を選択的に除去して配線13を形成する工程と、を含む。

(もっと読む)

半導体基板上のスルーインターコネクトを製造する方法

半導体基板のスルーインターコネクトを製造する方法は、基板の第1側部上に基板を部分的に通るビアを形成するステップと、第1側部上及びビア内に電気絶縁層を形成するステップと、絶縁層上にビアを少なくとも部分的にライニングする導電層を形成するステップと、ビア内の導電層上に第1コンタクトを形成するステップと、ビア内の、少なくとも絶縁層まで基板の第2側部から基板を薄層化するステップとを含む。また、本方法は、第1コンタクトと電気接続状態にある第2コンタクトを基板の第2側部に形成するステップをも含み得る。本方法は、ウエハスケールのインターコネクト要素を形成するように半導体ウエハ上で実行可能である。さらに、インターコネクト要素を、発光ダイオード(LED)システムのような半導体システムを構築するのに使用可能である。 (もっと読む)

半導体装置およびその製造方法

【課題】半導体装置の再配線層において配線を狭ピッチ化して隣接する配線間距離が著しく近接しても、配線間でイオンマイグレーションを効果的に抑制する。

【解決手段】一方の主面11aに半導体デバイスおよび電極11cが設けられた半導体基板11と、一方の主面11aの上に形成された層間絶縁層12と、層間絶縁層12上において個々の配線パターンに沿って複数形成されたポリイミドからなる樹脂パターン部13と、樹脂パターン部13の上にそれぞれ形成された再配線層14と、再配線層14の上を封止する封止絶縁層15とを有し、樹脂パターン部13の側面13aが、配線パターンの長手方向に垂直な断面において凹凸状とされている。

(もっと読む)

半導体装置の作製方法

【課題】電界メッキ法やCMP法を使わないことで製造コストを落として配線を形成する半導体装置の作製方法を提供する。

【解決手段】絶縁膜を形成する工程と、絶縁膜上にマスクを形成する工程と、選択的にエッチングして絶縁膜に開口部を形成する工程と、マスク上および開口部に第1導電膜を形成する工程と、液滴吐出法により開口部の第1導電膜上に導電材料を含む液滴を滴下する工程と、レーザー光を選択的に照射して導電材料を加熱して第2導電層を形成する工程と、マスク上および第2導電層上に第3導電膜を形成する工程と、マスクを除去すると同時にマスク上に形成された第1導電膜および第3導電膜を除去し、第1導電層および第3導電層を形成する工程とを有する半導体装置の作製方法を提供する。

(もっと読む)

回路基板の製造方法および回路基板

【課題】配線構造が積層化された回路基板において、回路特性の劣化を防止できる製造方法を提供する。

【解決手段】基板1上に下層配線パターン3を形成し、下層配線パターン3を覆う状態で絶縁膜5を形成し、この絶縁膜5に下層配線パターン3を露出する開口部5aを形成する。絶縁膜5上に上層配線パターン7を形成し、その後下層配線パターン3と上層配線パターン7とを接続する接続材料パターン9を絶縁膜5の開口部5aの側壁に形成する。接続材料パターン9は、例えば有機半導体材料を用いて形成する。これにより、有機半導体材料からなる接続材料パターン9の劣化を防止した回路基板11-1が得られる。

(もっと読む)

配線を形成する方法及び半導体装置の作製方法

【課題】生産性がよく、信頼性を向上した配線の作製方法とそれを用いた半導体装置の作製方法を提供する。

【解決手段】液滴吐出法によりゲート電極を形成する半導体装置の作製方法であって、基板上に半導体を形成し、半導体上にゲート絶縁膜を形成し、ゲート絶縁膜上に絶縁膜を形成し、絶縁膜にコンタクトホールを形成し、コンタクトホールにバリア膜として機能する金属膜をスパッタリング法または蒸着法により形成し、液滴吐出法により、コンタクトホールに銅からなる導電層をコンタクトホールを充填するように形成し、金属膜と導電層からなるゲート電極を形成する半導体装置の作製方法。

(もっと読む)

81 - 100 / 479

[ Back to top ]