Fターム[5F033JJ14]の内容

半導体集積回路装置の内部配線 (234,551) | 層間接続のコンタクト層の材料 (22,060) | 金属及びその合金(シリサイドを除く) (14,566) | Ag、Ag合金 (479)

Fターム[5F033JJ14]に分類される特許

41 - 60 / 479

半導体装置の作製方法及び表示装置の作製方法

【課題】材料の利用効率を向上させ、かつ、作製工程を簡略化して、信頼性の高い半導体

装置を作製する方法を提供する。

【解決手段】基板上に導電層を形成し、該導電層上に光透過層を形成し、該光透過層上か

らフェムト秒レーザを照射して、該導電層及び該光透過層を選択的に除去する工程を有す

る。なお、該導電層の端部は、該光透過層の端部より内側に配置されるように該導電層及

び該光透過層を除去されていてもよい。また、フェムト秒レーザを照射する前に、該光透

過層表面に撥液処理を行ってもよい。

(もっと読む)

貫通配線基板の製造方法及び貫通配線基板

【課題】貫通孔の底面部付近において、導電層をカバレッジ良く形成し、接触不良がなく、電気的な安定性を向上させた貫通配線を、工程やコストを増加することなく形成する。

【解決手段】半導体基板の一方の面に第一絶縁層を介して導電部を形成する第一工程、ドライエッチング法により半導体基板の他方の面側から第一絶縁層が露呈するように貫通孔を形成する第二工程、貫通孔の内壁面および底面に第二絶縁層を形成する第三工程、第二絶縁層及び第一絶縁層のうち貫通孔の底面に位置する部分を除去し導電部を露呈する第四工程、第二絶縁層上に導電層を形成し該導電層を導電部と電気的に接続する第五工程、を有し、第四工程において、第二絶縁層に続いて導電部の一部をエッチングすると共に、エッチングにより除去された第一金属成分とエッチングガス成分とからなる第一副生成物を、貫通孔の底面部及びその近傍に位置する内壁面部に堆積させ、テーパー部を形成する。

(もっと読む)

ビアホールの製造方法およびビアホールを有する半導体素子の製造方法

【課題】内部への埋め込み材料を増量させて放熱性向上効果を得ることが可能なビアホール構造を、ビアホール形成のための半導体基板へのエッチングの回数を少なくしつつ製造することのできるビアホールの製造方法およびビアホールを有する半導体素子の製造方法を提供する。

【解決手段】メタルマスク8は、メタルマスク10の開口23により露出させられた部分8aを有する。メタルマスク10は、メタルマスク8よりも厚く形成する。メタルマスク10の厚さは、開口23内のエッチングが半導体デバイス形成層4にほぼ到達すると同時に、開口22のエッチングがソース電極1に到達する厚さに設定する。

(もっと読む)

半導体装置

【課題】超高周波帯におけるシリコン基板による損失を低減すると共に、貫通配線のインダクタンス成分の影響を小さくした半導体装置を実現できるようにする。

【解決手段】半導体装置は、回路素子105が形成された半導体基板100と、半導体基板100の主面の上に形成された第1の誘電体層121と、第1の誘電体層121の上に形成された第2の誘電体層131と、第1の誘電体層121を貫通し、回路素子105と接続された第1の貫通配線122と、第2の誘電体層131を貫通し、第1の貫通配線122と接続された第2の貫通配線132とを備えている。第2の貫通配線132は、第1の貫通配線132よりもインダクタンスが小さい。

(もっと読む)

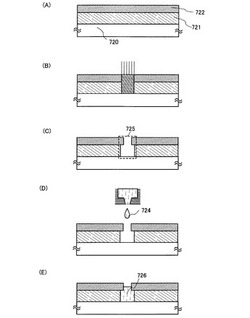

パターン形成方法及び回路基板の製造方法

【課題】印刷法にて、容易にヴィアホール等のパターンを形成する方法を提供する事。

【解決手段】基板上に設けられた第一高分子材料からなる第一薄膜をパターニングする際に、第一高分子材料を溶解する第一溶媒に第二高分子材料を溶解させた高分子溶液を準備し、これを第一薄膜に滴下する高分子溶液滴下工程と、第一溶媒が乾燥した後に第一薄膜を第二溶媒に触れさせる第二溶媒接触工程と、を含み、第二溶媒は第一高分子材料を溶解せず、第二高分子材料を溶解する溶媒とする。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】再配線のパターン形成後のレジストパターンの剥離性を確保しつつ、再配線のパターン形成前のレジストパターンとその下地との密着性を向上させる。

【解決手段】半導体チップ上に形成されたメタル膜5の表層には、レジスト膜6との密着性を上げる表面改質層16が形成され、表面改質層16を介してメタル膜5上に再配線7a〜7cが形成される。

(もっと読む)

半導体装置の作製方法

【課題】簡単な工程で絶縁膜、半導体膜、導電膜等の膜パターンを有する基板を作製する方法、さらには、低コストで、スループットや歩留まりの高い半導体装置の作製方法を提供することを目的とする。

【解決手段】基板上に形成された絶縁膜、半導体膜又は導電膜上に接して第1の膜を形成する工程と、第1の膜上に第1のマスク材料を含有する溶液を吐出して第1の膜上に第1のマスクを形成する工程と、第1のマスクを用いて第1の膜をパターニングして絶縁膜、半導体膜又は導電膜表面上に塗れ性の低い領域と塗れ性の高い領域を形成する工程と、第1のマスクを除去する工程と、塗れ性の低い領域に挟まれた塗れ性の高い領域に、第2のマスク材料を含有する溶液を吐出して第2のマスクを形成する工程と、第2のマスクを用いて、パターニングされた第1の膜をエッチングするとともに絶縁膜、半導体膜又は導電膜をエッチングする。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】低伝導度領域ができるだけ少なくなるグラフェン配線構造が可能な半導体装置を提供する。

【解決手段】半導体装置は、触媒金属膜220と、グラフェン膜230と、コンタクトプラグ240と、調整膜250と、を備える。触媒金属膜は、基板上に形成される。グラフェン膜は、触媒金属膜上に形成される。コンタクトプラグは、グラフェン膜と接続する。調整膜は、前記グラフェン膜表面のうち、前記コンタクトプラグと接続する領域以外の領域上に形成され、ディラック点位置をフェルミ準位に対してコンタクトプラグと接続する領域と同方向に調整する。

(もっと読む)

半導体素子、半導体装置及び半導体素子の作製方法

【課題】半導体領域に酸化物半導体を用いた、高耐圧で、大電流の制御が可能であり、かつ量産性に優れた半導体素子を提供することを課題の一とする。また、該半導体素子を用いた半導体装置を提供することを課題の一とする。また、該半導体素子の作製方法を提供することを課題の一とする。

【解決手段】半導体領域に酸化物半導体を用いたトランジスタと、トランジスタのゲート電極層、ソース電極層及びドレイン電極層の各々と電気的に接続した貫通電極を備えた半導体チップを積層し、トランジスタを電気的に並列接続することによって、実質的にW長の長い半導体素子を提供する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】再配線間のリークを抑制しつつ、再配線のピッチを微細化するとともに、再配線上のビア開口時のマージンを上げる。

【解決手段】緩衝層4上には再配線7bが形成され、再配線7b上には表面層8bが形成されている。表面層8bは、再配線7bから幅方向にはみ出すようにして再配線7bに沿うように配置され、再配線7bよりもエッチング耐性が高い。

(もっと読む)

半導体デバイス

【課題】応力による半導体回路の特性劣化を抑制した半導体デバイスを提供する。

【解決手段】縦導体は、半導体基板の厚み方向に設けられた微細孔を満たし、第1結晶組織301と第2結晶組織302とを含むナノコンポジット結晶構造を有する。ナノコンポジット結晶構造において、第1結晶組織301及び第2結晶組織302の少なくとも一方は、ナノサイズである。

(もっと読む)

半導体デバイス

【課題】ストレスによる半導体回路の特性変動・劣化を抑制した半導体デバイスを提供する。

【解決手段】縦導体3は、半導体回路に隣接して半導体層1の厚み方向に設けられ、少なくとも一つは、半導体層1と対面する領域に、等軸晶領域を有するか、または、凝固点と融解点との温度差が50℃以上である。

(もっと読む)

半導体装置及びその製造方法

【課題】配線間の実効的な容量の増加を抑制する。

【解決手段】半導体装置100は、6員環構造の環状シロキサンを原料とする絶縁膜11と、絶縁膜11に形成された配線溝12と、配線溝12に金属膜(配線メタル)15が埋め込まれて構成される配線10と、を有する。半導体装置100では、配線溝12の底面において、絶縁膜11の内部よりも単位体積あたりの炭素原子数、又は/及び、窒素原子数が多い改質層13が形成されている。

(もっと読む)

配線基板の製造方法

【課題】コンタクトホールを、生産性良く、低コストで、且つ信頼性良く製造する配線基板の製造方法を提供する。

【解決手段】基板1に第1電極3及び第2電極7が形成される。第1電極3及び第2電極7を連通するように形成された微細穴の側壁部及び底部に、導電膜9を形成してコンタクトホール2を形成する。この配線基板100の製造する際に、微細穴を形成する微細穴形成工程において、微細穴の側壁部の開口端側に相対的に浅い溝からなる第1溝領域4が形成され、微細穴の側壁部の底部側に相対的に深い溝からなる第2溝領域5が形成される。このように区分けした溝領域4,5のうち、第2溝領域5に導電性材料を含有する液体を付与して、導電膜9を形成する。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】研磨工程を含む新規な半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、半導体基板上方に、絶縁膜を形成する工程と、絶縁膜に、第1の深さを有するダミー溝と、第1の深さよりも深い第2の深さを有する配線溝と、配線溝の底面に配置されるビアホールとを形成する凹部形成工程と、ダミー溝内、配線溝内、ビアホール内、及び絶縁膜上方に、導電材を堆積させる工程と、絶縁膜上方の導電材を研磨除去する工程とを有する。

(もっと読む)

電子デバイス及びその製造方法

【課題】高性能及び高機能で、高周波特性に優れ、コストダウンに有効な絶縁構造を持つ電子デバイス及びその製造方法を提供する。

【解決手段】半導体基板1は、その厚み方向に伸びる縦孔30を有している。絶縁物充填層3は、縦孔30内にその内周面を覆うように充填してなる環状層である。縦導体2は、絶縁物充填層3によって囲まれた領域20内に充填された凝固金属体でなる。絶縁充填層3は、有機絶縁物又はガラスを主成分とする無機絶縁物と、ナノコンポジット構造のセラミックとを有する層である。ナノコンポジット構造のセラミックは、常温比抵抗が1014Ω・cmを超え、比誘電率が4〜9の範囲にある。

(もっと読む)

半導体装置及びその製造方法

【課題】実装基板に信頼性よく実装できる多層構造の再配線を備えた半導体装置を提供する。

【解決手段】バンプ電極18を備えた半導体基板10aと、半導体基板10aの上に形成され、バンプ電極18の横方向に配置された第1絶縁層20と、第1絶縁層20の上に形成され、バンプ電極18に接続された第1配線層30と、第1配線層30の上に形成された第2絶縁層22と、第2絶縁層22に形成され、第1配線層30に到達するビアホールVHと、第2絶縁層22の上に形成され、ビアホールVHに形成されたビア導体40を介して第1配線層30に接続される第2配線層32と、第2配線層32に接続された外部接続端子34とを含み、第2絶縁層22の弾性率は第1絶縁層20の弾性率より低く設定されている。

(もっと読む)

パターン付基板の作製方法、及び半導体装置の作製方法

【課題】隣接する膜パターンの間隔を制御することが可能なパターン付基板の作製方法を

提供する。また、膜パターンの幅の制御が可能で、特に、幅が細く且つ厚みのあるパター

ン付基板の作製方法を提供する。また、アンテナのインダクタンスのバラツキが少なく、

起電力の高い導電膜を有する基板の作製方法を提供することを課題とする。また、歩留ま

り高く半導体装置を作製する方法を提供することを課題とする。

【解決手段】基板、絶縁膜又は導電膜上に珪素及び酸素が結合し且つ前記珪素に不活性な

基が結合する膜を形成した後、珪素及び酸素が結合し且つ前記珪素に不活性な基が結合す

る膜表面に印刷法を用いて組成物を印刷し、組成物を焼成して膜パターンを形成すること

を特徴とする。

(もっと読む)

貫通電極を持つ半導体装置

【課題】貫通電極を持つ半導体装置を提供する。

【解決手段】パッドと、パッドの下部に配される貫通電極と、を備える半導体装置。貫通電極は、円筒形の第1金属プラグと、第1金属プラグの外周を取り囲む第1半導体レイヤと、第1半導体レイヤの外周を取り囲む第2金属プラグと、第1金属プラグの外周を取り囲む第2半導体レイヤと、第1金属プラグの外周に、第1半導体レイヤ及び第2金属プラグの内周及び外周に、そして第2半導体レイヤの内周に形成される少なくとも一つの絶縁膜と、を備え、第1半導体レイヤ内に第1絶縁膜との界面から広がる空乏層が形成されるように、第1半導体レイヤに第1バイアス電圧を印加するが、第1バイアス電圧は、第2半導体レイヤに印加される第2バイアス電圧とは異なる。

(もっと読む)

半導体装置およびその製造方法

【課題】積層される半導体基板同士が、貫通孔の内部に埋め込まれる導電体により、電気的に良好に接続される半導体装置を提供する。

【解決手段】第1半導体基板SCPは、主表面を有する基板SUBと、基板SUB内および基板SUB上に形成された半導体素子TRと、半導体素子TRに電気的に接続された配線MTLと、基板SUBの主表面であり、互いに対向する第1主面と第2主面とを貫通し、配線MTLに達する貫通孔の内部に形成された導電層TSVとを有する。第1半導体基板SCPと第2半導体基板SCPとが積層され、導電層TSVは第2半導体基板SCPの配線MTLと電気的に接続される。導電層TSVの第2主面では、貫通孔の端部の周囲には凹部DUMが形成され、凹部DUMの底壁面は基板SUBの内部に存在する。導電層TSVを構成する導電材料CUが凹部DUMの内部に充填される。

(もっと読む)

41 - 60 / 479

[ Back to top ]