Fターム[5F033JJ14]の内容

半導体集積回路装置の内部配線 (234,551) | 層間接続のコンタクト層の材料 (22,060) | 金属及びその合金(シリサイドを除く) (14,566) | Ag、Ag合金 (479)

Fターム[5F033JJ14]に分類される特許

101 - 120 / 479

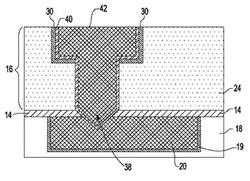

ビアがガウジングされた相互接続構造体及びその製造方法

【課題】 ビア開口部の底部にガウジング構造部を含む相互接続構造体、及びその形成方法を提供する。

【解決手段】 本発明の方法は、ビア開口部の上に配置されるライン開口部内の堆積されたトレンチ拡散バリアの被覆率に影響を与えず、及び/又は、ビア開口部及びライン開口部を含む相互接続誘電体材料内にスパッタリングを行なうことによりビア開口部の底部にガウジング構造部を生成することに起因する損傷を生じさせない。こうした相互接続構造体は、最初に相互接続誘電体内にライン開口部を形成し、その後、ビア開口部、次いでガウジング構造部を形成することによって、ビア開口部の底部内にガウジング構造部を提供することにより達成される。

(もっと読む)

半導体装置、電子部品、半導体装置の製造方法

【課題】貫通電極の電気特性を効率よく検査する。

【解決手段】本発明の半導体装置2の製造方法は、シリコン基板20に半導体素子を含んだ電気回路を形成する工程と、シリコン基板20を貫通して設けられ、電気回路と電気的に接続される第1貫通電極22を形成する工程と、シリコン基板20を貫通して設けられ、シリコン基板20の表面20aで第1貫通電極22と短絡する第2貫通電極23を形成する工程と、シリコン基板20の裏面20bにおいて、第1貫通電極22と第2貫通電極23との間の電気特性を検査する工程と、を有する。

(もっと読む)

半導体装置

【課題】下層導電層の表面を十分保護することができ、信頼性が高く、配線容量が小さなデュアルダマシン配線を有する半導体装置の製造方法を提供する。

【解決手段】導電性領域11を有する下地と10、下地の表面を覆う絶縁性エッチストッパ膜12と、絶縁性エッチストッパ膜上に形成された層間絶縁膜と、層間絶縁膜表面から第1の深さで形成された配線用溝と、配線用溝底面から導電性領域に達する接続用孔と、配線用溝および接続用孔を埋め込んで形成されたデュアルダマシン配線である。層間絶縁膜が配線用溝の側面および底面を包む第1種の絶縁層15と、第1種の絶縁層よりも下に配置され、第1種の絶縁層とエッチング特性の異なる第2種の絶縁層56とを含む。接続用孔は、断面で見た時に第1種の絶縁層内で傾斜し、上方に向かって次第に開口が増大する部分を有する。

(もっと読む)

貫通電極基板及びその製造方法、並びに貫通電極基板を用いた半導体装置

【課題】基板の表裏を導通する導通部における電気特性を向上した貫通電極基板及びそれを用いた半導体装置を提供すること。

【解決手段】本発明の貫通電極基板100は、表裏を貫通する貫通孔104を有する基板102と、貫通孔104内に充填される金属材料を含む導通部106と、を備え、導通部106の一端は、導通部106の他端より面積重み付けした平均結晶粒径が大きい金属材料を少なくとも含む。また、導通部106は、結晶粒径が13μm以上の金属材料を含む。

(もっと読む)

インプリント方法、配線パターンの形成方法、および積層電子部品

【課題】パターン欠陥の発生を抑制、防止して、パターンを歩留まりよく形成できるインプリント方法、それを用いた配線パターンの形成方法、該方法により形成された配線パターンを備えた積層電子部品を提供する。

【解決手段】被転写材領域R1の重心を通る直線上において、(a)被転写材領域内に位置する部分を線分被転写材部L1とし、(b)モールドパターン領域R2内に位置する部分を線分モールドパターン部L2とし、(c)プレス領域R3内に位置する部分を線分プレス部L3とした場合において、(イ)線分被転写材部の長さが線分プレス部の長さ以上で、(ロ)線分被転写材部と線分プレス部の重なる部分が線分被転写材部の92%以上を占め、かつ、(ハ)線分被転写材部の長さが線分モールドパターン部の長さ以上で、(ニ)線分被転写材部と線分モールドパターン部の重なる部分が線分被転写材部の97%以上を占めるという条件を満たしてインプリントを行う。

(もっと読む)

電界効果型トランジスタの製造方法、電界効果型トランジスタ、表示装置、及び電磁波検出器

【課題】絶縁層へのコンタクトホール形成時における、導電層の浸食や破損の抑制された電界効果型トランジスタの製造方法、電界効果型トランジスタ、表示装置、及び電磁波検出器を提供する。

【解決手段】導電層形成工程によって形成されたソース電極20A、ドレイン電極20B、及び画素電極20Cを含む導電層20上に、該導電層20及び酸化物半導体層18を覆うように、無機材料を主成分とする無機絶縁層23を形成する。そして、この無機絶縁層23上にフォトレジスト膜30を形成してパターン状に露光した後に、現像工程において、現像液を用いて現像することでレジストパターン30B’を形成する。現像工程では、この現像液をエッチング液として用いて、無機絶縁層23の内のレジストパターン30B’から露出した領域を除去することによって導電層20の一部を露出させて、無機絶縁層22にコンタクトホール27を形成する。

(もっと読む)

アクティブマトリクス基板およびその製造方法

【課題】従来よりも高い効率で製造することが可能な、コンタクトホールの段差部における画素電極の断線を防止したアクティブマトリクス基板およびその製造方法を提供する。

【解決手段】ゲート電極10と、ゲート電極を覆うように形成されたゲート絶縁層50と、ゲート絶縁層の上に形成された半導体層40と、半導体層と接触するように形成されたソース電極11およびドレイン電極12と、ソース電極およびドレイン電極の上に形成された第1層間絶縁層54と、第1層間絶縁層の上に形成された画素電極20と、第1層間絶縁層に形成された第1コンタクトホール51と、第1コンタクトホール内に形成された第1金属層55であって、厚さが第1コンタクトホールの深さより小さく、且つ、第1コンタクトホール内においてドレイン電極と電気的に接続された第1金属層55とを備え、画素電極は第1コンタクトホール51内で第1金属層に接触している。

(もっと読む)

金属充填装置

【課題】凹面化、空隙、ボイドなどを生じることなく、対象物の微細空間を金属充填材によって満たし、低コスト化と処理効率の向上とを実現しうる金属充填装置を提供すること。

【解決手段】金属充填装置は、微細空間の開口面の一つが開放された状態で、その開口面の反対側から対象物2を支持する第1の支持体10と、前記開口面側から第1の支持体10と接合して、対象物2を処理室A内に封入する第2の支持体11と、処理室Aに溶融金属Mを供給する溶融金属供給部12と、処理室A内の圧力を制御する圧力制御部13とを備えており、微細空間内に溶融金属Mが充填された後、その溶融金属が冷却により硬化するまで、処理室Aに圧力を与える加圧手段を有する。

(もっと読む)

半導体装置の製造方法、半導体装置、アクティブマトリクス装置、電気光学装置および電子機器

【課題】生産性に優れた半導体装置の製造方法、半導体装置、アクティブマトリクス装置、電気光学装置および電子機器を提供すること。

【解決手段】本発明の半導体装置の製造方法は、基板7の一方の面側に、トランジスタ4のゲート絶縁体層44を形成する第1の工程と、ゲート絶縁体層44上に、厚さ方向に貫通する貫通部91を備える絶縁体層9を形成する第2の工程と、貫通部91内の底部付近のゲート絶縁体層44上、および、貫通部91の周囲の絶縁体層9上に、気相成膜法により同時にかつ互いに接触しないようにそれぞれ電極を形成し、ゲート絶縁体層44上に形成された電極を用いて、ゲート電極45を形成するとともに、絶縁体層9上に形成された電極を用いて、画素電極6を形成する第3の工程とを有する。また、平面視で、貫通部91の開口部の縁が、当該貫通部91の底部の縁より内側に位置する。

(もっと読む)

配線パターンの形成方法

【課題】インプリントモールドの凹部への感光性配線ペースト層の充填不良や、ウェットエッチング(現像)工程での配線パターンの倒壊や剥がれの発生を抑制,防止して、効率よく精度の高い配線パターンを形成する。

【解決手段】感光性配線ペースト層2を形成する工程と、凹凸パターン17を有するインプリントモールド3を感光性配線ペースト層2に押し付けて光照射する工程と、感光性配線ペースト層2の未感光部をウェットエッチングにより除去して、インプリントモールドの凹凸パターンに対応する配線パターンを形成する工程とを備えた配線パターンの形成方法において、感光性配線ペースト層2の厚みtpを下記の式(1)の範囲で規定する。

6μm+(V/S)<tp<20μm+(V/S)……(1)

ただし、

tp:感光性配線ペースト層の厚み、

S:ペースト転写領域の面積、

V:前記凹凸パターンの、前記感光性配線ペースト層と接する領域における凹部の体積

(もっと読む)

薄膜トランジスタ装置およびその製造方法

【課題】

使用現場で使用者や顧客の要望に応じて、回路システムを形成することのできる薄膜トランジスタ装置およびその製造方法を提供する。

【解決手段】

薄膜トランジスタ装置において、TFTにより構成した複数の集積回路ブロック1,2と、これらの集積回路ブロックを相互に接続するための網目状に交差したマトリックス配線3、4、5、6を設ける。相互の集積回路ブロック間の接続は、使用現場で使用者や顧客の要望に応じて導電性材料を印刷等により、マトリックス配線の各々の配線交差部に選択的に設けることにより行い、所望の回路システムを構成する。

(もっと読む)

酸化マンガン膜の形成方法、半導体装置の製造方法および半導体装置

【課題】 Cuとの密着性を良好とすることが可能な酸化マンガン膜の形成方法を提供すること。

【解決手段】 酸化物102上にマンガンを含むガスを供給し、酸化物102上に酸化マンガン膜103を形成する酸化マンガン膜103の形成方法であって、酸化マンガン膜103を形成する際の成膜温度を、100℃以上400℃未満とする。

(もっと読む)

リフトオフ方法及び薄膜トランジスタの製造方法

【課題】歩留まりの低下を防止して、製造工程の簡素化を図ることが可能になるとともに、製造コストの低減を図ることができる表示装置及びその製造方法を提供することを目的とする。

【解決手段】半導体ナノワイヤ3とリフトオフレジスト12と金属膜13とが形成された基板1を、気体のマイクロバブルが混合された液体により構成された剥離液に浸漬させることにより、リフトオフレジスト12とともにリフトオフレジスト12上の金属膜13を剥離して、基板2上に金属膜13からなる所定のパターンを形成する。

(もっと読む)

半導体基板と半導体基板の製造方法および半導体パッケージ

【課題】高信頼性の貫通電極を有する半導体基板と半導体基板の製造方法を提供することを目的とする。

【解決手段】第1絶縁層(2)を介して第1配線層(3)が形成され、貫通孔(4)の内周に第2配線層(5)を形成し、貫通孔(4)は、第1の開口部(4a)と、第1の開口部(4a)よりも開口面積が小さい第2の開口部(4b)で形成され、第2の開口部(4b)に第3配線層(103a)を形成するとともに、第3配線層(103a)を第1の開口部(4a)よりも先に形成することを特徴とする。

(もっと読む)

ビア構造とそれを形成するビアエッチングプロセス

【課題】ビア構造とそれを形成するビアエッチングプロセスを提供する。

【解決手段】ビアエッチングプロセスは、丸角とテーパ型側壁プロファイルを有するスルーサブストレートビアを形成する。その方法は、半導体基板を提供するステップと、半導体基板上に、ハードマスク層とパターン化フォトレジスト層を形成するステップと、ハードマスク中に開口を形成して、半導体基板の一部を露出するステップと、パターン化されたフォトレジスト層とハードマスク層をマスキング要素として、半導体基板の少なくとも一部を通過するビアを形成するステップと、トリミングプロセスを実行して、ビアの頂角を丸くするステップと、フォトレジスト層を除去するステップと、からなる。

(もっと読む)

半導体装置とその製造方法、電気光学装置とその製造方法、回路基板とその製造方法、及び電子機器

【課題】フォトリソグラフィー法及びエッチング法を用いることなく導電層間を接続することができる半導体装置の製造方法を提供する。

【解決手段】本発明の半導体装置の製造方法は、基板上に第1導電層と層間絶縁膜と第2導電層とを順に積層形成する導電層工程と、前記第2導電層の表面から物理的加工を施すことで、前記第2導電層と前記層間絶縁膜とを貫通して前記第1導電層に達する凹部を形成するコンタクトホール形成工程と、を有することを特徴とする。

(もっと読む)

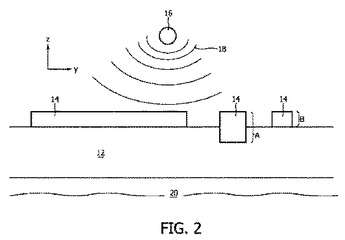

集積回路を製造する装置及び方法

本発明は、厚膜金属層14を有する集積回路10を製造する装置に関する。金属ペースト14の層は、熱伝導基板12上に適用手段24によって適用される。金属ペースト14は、予め決められたサイズの金属粒子を含む。RF生成器16は、金属ペースト14にRFエネルギー18を選択的に誘導結合させる。金属粒子を加熱するために、金属ペースト14の金属粒子の予め決められたサイズは、RFエネルギー18の結合周波数に対応する。このようにして、金属ペースト14の金属粒子は、従来のプロセスのパワーの何分の一かのパワーで、金属ペースト14を予備焼結する必要なく、加熱される。  (もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】半導体装置内の埋め込みコンタクトホールを簡略な工程で形成するための半導体装置の製造方法を提供する。

【解決手段】シリコン基板101上に1又は複数の半導体素子が作り込まれてなる半導体装置に埋め込みコンタクトを形成するにあたり、半導体素子層の全面に層間絶縁膜109を形成する(第1工程)。次いで、半導体装置内のシリコン106、107、ポリシリコン104A、104B、又は金属シリサイド108A,108Bからなる2つの領域が露出するように層間絶縁膜にコンタクトホール109aを形成する(第2工程)。そして、コンタクトホールから露出しているシリコン106、107、ポリシリコン104A、104B、又は金属シリサイド108A,108Bの表面に無電解めっき法により選択的に金属膜111を形成する(第3工程)。

(もっと読む)

配線構造、及びそれを備えた液晶表示装置、並びに配線製造方法

【課題】配線を高精細化しても断線が生じ難い、信頼性の高い配線回路を実現する。

【解決手段】配線構造1は、ゲート電極17・17b・17cが配された基板9上に配される半導体層10と、ゲート電極17・17b・17c及び半導体層10が配された基板9上に配された第2層間絶縁膜13と、第2層間絶縁膜13上に配される配線18とを備え、第2層間絶縁膜13に形成されたコンタクトホール15内で、半導体層10と、配線18とが電気的に接続され、第2層間絶縁膜13は感光性樹脂材料からなり、さらに、コンタクトホール15内には導電性微粒子16が充填されており、導電性微粒子16によって、半導体層10と、配線18とが電気的に接続されている。

(もっと読む)

半導体装置

【課題】コンタクトホールの加工時において配線のダメージを受けにくく、信頼性の低下を抑制できる構造の接続部を有する半導体装置を提供すること。

【解決手段】接続部1は、第1導電層2と第2導電層4とが、その交差個所に設けられたコンタクトホール5を介して接続されたものである。矩形状のコンタクトホール5は第2導電層4の幅方向の略中央に配置されている。そして、コンタクトホール5のパターンを囲むように矩形状の半導体層3が設けられている。半導体層3は、コンタクトホール5の底部において第1導電層2上に形成されている。この半導体層3は、第1導電層2とのエッチング選択比が高く、第1導電層2に対するエッチング効率が充分に高いものである。

(もっと読む)

101 - 120 / 479

[ Back to top ]