Fターム[5F033JJ19]の内容

半導体集積回路装置の内部配線 (234,551) | 層間接続のコンタクト層の材料 (22,060) | 金属及びその合金(シリサイドを除く) (14,566) | 高融点金属 (7,010) | W (2,609)

Fターム[5F033JJ19]に分類される特許

41 - 60 / 2,609

半導体装置

【課題】微細化が可能な半導体装置を提供する。

【解決手段】実施形態に係る半導体装置は、上面に、一方向に延び上方に突出した複数本のアクティブエリアが形成された半導体基板と、前記アクティブエリア間のトレンチの下部に埋め込まれた素子分離絶縁体と、第1の絶縁材料からなり、前記素子分離絶縁体の直上域に配置され、下部が前記トレンチ内に配置され、上部が前記アクティブエリアの上端よりも上方に突出した絶縁ブロックと、前記第1の絶縁材料とは異なる第2の絶縁材料からなり、前記半導体基板及び前記絶縁ブロックの上方に設けられた層間絶縁膜と、前記層間絶縁膜内に形成され、下端が前記アクティブエリアの上面に接続されたコンタクトと、を備える。前記コンタクトにおける前記絶縁ブロックの直上域に位置する部分の下面は、前記コンタクトにおける前記アクティブエリアの直上域に位置する部分の下面よりも上方に位置している。

(もっと読む)

ウェハ裏面のキャパシタを有する半導体デバイスを形成する方法

【課題】 ウェハ裏面のキャパシタを有する半導体デバイスの形成方法を提供する。

【解決手段】 本発明の方法は、その前面の活性シリコン層とその裏面のバルク・シリコン層との間に挿入された埋込み絶縁層を有する、SOI基板を準備するステップと、SOI基板の前面から埋込み絶縁層を貫通して延びる埋込みコンタクト・プラグを含む集積回路を、SOI基板の前記前面に形成するステップと、裏面エッチング・プロセスを実施してバルク・シリコン層内にトレンチを形成し、埋込みコンタクト・プラグの端部を埋込み絶縁層の裏表面に露出させるステップと、第1キャパシタ・プレートと、第2キャパシタ・プレートと、該第1及び第2キャパシタ・プレートの間に挿入されたキャパシタ誘電体層とを含むキャパシタをトレンチ内に形成するステップとを含み、第1キャパシタ・プレートは、埋込みコンタクト・プラグの露出した端部に接触するように形成される。

(もっと読む)

半導体装置及びその製造方法

【課題】プラグが微細化しても埋め込み不良が生じることなく、低コストで形成することができ、さらに種々の半導体装置に適用可能であるプラグ及びその形成技術を提供する。

【解決手段】本発明の実施形態にかかる半導体装置の製造方法は、半導体基板上に酸化シリコン膜を形成し、酸化シリコン膜にビアを形成し、ビア内側に密着層を形成し、密着層上にシリコン層を形成し、タングステンを含むガスをシリコン層と反応させることにより、ビアに埋め込まれたタングステン膜を形成する。

(もっと読む)

半導体装置およびその作製方法

【課題】酸化物半導体膜と金属膜との接触抵抗を低減する。オン特性の優れた酸化物半導体膜を用いたトランジスタを提供する。高速動作が可能な半導体装置を提供する。

【解決手段】酸化物半導体膜を用いたトランジスタにおいて、酸化物半導体膜に窒素プラズマ処理を行うことで酸化物半導体膜を構成する酸素の一部が窒素に置換された酸窒化領域を形成し、該酸窒化領域に接して金属膜を形成する。該酸窒化領域は酸化物半導体膜の他の領域と比べ低抵抗となり、また、接触する金属膜との界面に高抵抗の金属酸化物を形成しにくい。

(もっと読む)

半導体装置および半導体装置の作製方法

【課題】半導体装置の特性を損なうことがない半導体装置およびその作製方法を提供する。

【解決手段】酸化物半導体層を含むトランジスタ(半導体装置)において、電極層を酸化物半導体層の下部に接して形成し、不純物を添加する処理により酸化物半導体層に自己整合的にチャネル形成領域と、チャネル形成領域を挟むように一対の低抵抗領域を形成する。また、電極層および低抵抗領域と電気的に接続する配線層を絶縁層の開口を介して設ける。

(もっと読む)

半導体装置及びそれを用いたSiPデバイス

【課題】高耐圧の能動素子を含む回路と低電圧で動作するロジック回路とが同一基板上に混載された半導体装置を低コストで実現する。

【解決手段】半導体装置が、ロジック回路50と、能動素子回路とを具備している。ロジック回路50は、半導体基板1に形成された半導体素子2を備えている。該能動素子回路は、半導体基板1の上方に形成された拡散絶縁膜7−1の上に形成された半導体層8−1、8−2を用いて形成されたトランジスタ21−1、21−2を備えている。この能動素子回路がロジック回路50により制御される。

(もっと読む)

半導体装置およびその製造方法

【課題】 実施形態は、層間配線抵抗が低減した半導体装置およびその製造方法を提供することを目的とする。

【解決手段】 実施形態の半導体装置は、基板と、前記基板上に第1の触媒金属膜と、前記第1の触媒金属膜上にグラフェンと、前記グラフェン上に層間絶縁膜と、前記層間絶縁膜を貫通するコンタクトホールと、前記コンタクトホール底部に前記グラフェンと電気的に導通する導電膜と、導電膜上に水素、窒素、アンモニアと希ガスの中から選ばれる1種以上のガスのプラズマで処理した第2の触媒金属膜と、前記第2の触媒金属膜上にカーボンナノチューブとを備えることを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】貫通電極を効率良く形成する。

【解決手段】シリコン基板1にビアホール25を形成し、絶縁膜22を形成した後、ビアホール25に低誘電率膜31を埋め込む。ビアホール25内の低誘電率膜31の膜厚を異方性ドライエッチングによって所望の値に減少させる。この異方性ドライエッチングによって、絶縁膜22上の低誘電率膜31が除去される。続いて、ビアホール25内に導電材を埋め込み、トランジスタT1,T2上に多層配線を形成する。この後、シリコン基板1の裏面側を研磨して導電材を露出させると、貫通電極が形成される。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】シールリングの内側領域生じたクラックを低コストで検出することができる半導体装置を提供する。

【解決手段】図2に示すように、本実施形態に係る半導体装置は、多層配線層と、内部回路領域3と、多層配線層に形成され、内部回路領域3を囲うシールリング220と、平面視で内部回路領域3とシールリング220とに挟まれた領域に設けられているTEG200と、を含んでいる。TEG200は、多層配線層の少なくとも2層それぞれに設けられ、互いに接続する導体パターン7と、P型ウェル13と、N型ウェル14とによって構成されている。P型ウェル13とN型ウェル14は、平面視で交互に互いに接続された状態で配置されており、P型ウェル13とN型ウェル14のいずれか一つに導体パターン7が接続されている。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】半導体装置の反りを抑制し、且つ、その反りの経時変化を抑制する。

【解決手段】半導体装置は、基板と、基板上に形成された多層配線層と、を有し、多層配線層は、配線と、配線を覆う層間絶縁膜と、をそれぞれ有する複数層の配線層を有する。少なくとも何れか1つの層間絶縁膜(例えば、層間絶縁膜27、30)は、第1絶縁膜41と第2絶縁膜42とを有する。第1絶縁膜41は、基板を第1方向(例えば下に凸)に反らせる応力を基板に与える。第2絶縁膜42は、第1絶縁膜41よりも表層側に形成され、第1絶縁膜41よりも吸湿性が低く、基板を第1方向に対する反対方向(例えば上に凸)に反らせる応力を基板に与える。

(もっと読む)

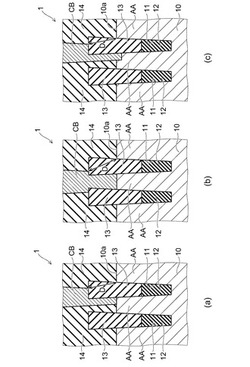

半導体装置及びその製造方法

【課題】プロセス条件の見直しを最小限に抑制しつつ電気的特性を向上させることができる半導体装置及びその製造方法を提供する。

【解決手段】半導体装置1は、半導体構造11の上面領域に形成された島状の絶縁膜20と、絶縁膜20の上面領域に配列された複数の凸状絶縁部23と、これら凸状絶縁部23と絶縁膜20とを被覆する層間絶縁膜26とを備える。

(もっと読む)

半導体チップ、これを含む半導体パッケージ、及びその製造方法

【課題】信頼性を向上させることができる高集積化された半導体チップ及びこれを含む半導体パッケージが提供される。

【解決手段】本発明にしたがう半導体チップは、基板と、前記基板を貫通している貫通ビアと、前記貫通ビアと前記基板との間に介在されたウェッティング膜と、前記ウェッティング膜と前記貫通ビアとの間に介在されたシード膜と、を含む。本発明の実施形態による半導体チップは突出された貫通ビアをウェッティング膜が覆っているので、導電パッドを追加に形成する必要がない。したがって、半導体チップの厚さを減らすことができ、構造が単純化されて半導体装置の高集積化により有利である。また、工程を単純化することができるので、生産収率を増大させ得る。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体装置の外部端子に加わる外力により外部端子の下方の絶縁膜にクラックが生じるのを抑制または防止する。

【解決手段】半導体基板1の主面上には複数の配線層が形成されている。この複数の配線層のうちの最上の配線層MHの直下の第5配線層M5において、最上の配線層MHのボンディングパッドPDのプローブ接触領域PAの直下には、導体パターン(第5配線5F、ダミー配線およびプラグ6C)を形成しない。上記第5配線層M5において、最上の配線層MHのボンディングパッドPDのプローブ接触領域PAの直下以外の領域には、導体パターン(第5配線5F、ダミー配線およびプラグ6C)を形成する。

(もっと読む)

半導体装置の製造方法

【課題】貫通電極を有する半導体装置の製造方法において、埋設導電部間のショートが起き難くすること。

【解決手段】半導体素子を有する素子領域と貫通電極が形成される貫通電極領域とを有する基板の上に第1絶縁膜を形成し、前記素子領域上の前記第1絶縁膜に凹部を形成し、前記貫通電極領域上の前記第1絶縁膜にダミー凹部を形成し、前記第1絶縁膜上、前記凹部内、および前記ダミー凹部内に第1導電材を形成し、前記第1導電材および前記第1絶縁膜の上部を研磨して、前記凹部内に導電部を形成すると共に前記ダミー凹部内にダミー導電部を形成し、前記貫通電極領域上の前記第1絶縁膜および前記貫通電極領域をエッチングして前記基板内に至る貫通電極ホールを形成した後、前記貫通電極ホール内に第2導電材を形成し、前記貫通電極ホール内に形成された第2導電材が露出するまで前記基板の裏面を研磨して、前記貫通電極を形成すること。

(もっと読む)

半導体装置

【課題】Low−k膜を層間絶縁膜として用いた半導体装置であっても、ダイシング時に発生するクラックがシールリング部へ伝播するのを抑制し、半導体装置の信頼性を向上する技術を提供する。

【解決手段】ダイシング領域側の各層にダミービア125,135,145,155,165を形成する。ダミービア125,135,145,155,165は上面からみて、縦横に等間隔に配置、あるいは千鳥配置されるように形成する。ダイシング時にクラックが発生しても、ダミービア125,135,145,155,165によって、クラックがシールリング部190にまで伝播するのを抑制することができる。その結果、回路形成領域の吸湿耐性を向上させ、信頼性の劣化を防止することができる。

(もっと読む)

半導体装置の製造方法

【課題】アライメント光によるアライメントマークの検出感度を向上させて、低コストで貫通孔の位置合わせを行う。アライメントマークの誤検出を防ぐ。また、アライメントマーク検出時のアライメント光の露光マージンを大きくして、微細化に対応可能な半導体装置の製造方法を提供する。

【解決手段】半導体基板の非有効ショット領域において、半導体基板の主面又は主面よりも上方にアライメントマークを形成する。半導体基板の裏面の方から、アライメントマークが形成された位置に対応する開口を形成する。半導体基板内に形成されている半導体装置の構成パターンと露光用マスクパターンとの位置合わせをして、有効ショット領域の半導体基板内に貫通孔を形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】実施形態は、一括して形成することが可能なメモリセルを有し、その直下に制御回路を設けた構成を実現する半導体装置およびその製造方法を提供する。

【解決手段】実施形態は、基板上に設けられたメモリアレイと、前記基板と前記メモリアレイとの間の前記基板の表面に設けられた制御回路と、を有する半導体装置の製造方法であって、前記制御回路のp形半導体領域およびn形半導体領域を覆う絶縁層に、前記p形半導体領域に連通する第1のコンタクトホールを形成する工程と、前記第1のコンタクトホールの内部に、前記p形半導体領域に接したコンタクトプラグを形成する工程と、を備える。さらに、前記n形半導体領域に連通する第2のコンタクトホールを前記絶縁層に形成する工程と、前記コンタクトプラグと、前記第2のコンタクトホールの内部に露出した前記n形半導体領域と、に接する配線を形成する工程と、を備える。

(もっと読む)

不揮発性記憶素子及び不揮発性記憶装置並びにそれらの製造方法

【課題】良好な電気的特性が得られる不揮発性記憶素子及びその製造方法を提供する。

【解決手段】第1の配線103と、第1の配線103上に形成され、第1の配線103に接続される第1のプラグ107及び第2のプラグ108と、第1電極109、第2電極113、及び抵抗変化層112を有し、第1のプラグ107上に形成され、第1電極109が第1のプラグ107と電気的に接続されている抵抗変化素子114と、抵抗変化素子114上に形成され、第2電極113と電気的に接続されている第2の配線119と、第2のプラグ108上に形成され、第2のプラグ108と電気的に接続されている第3の配線121とを備え、第1のプラグ107の上面と第2のプラグ108の上面とが略同一平面内に形成され、かつ第2の配線119の上面と第3の配線121の上面とが略同一平面内に形成されている。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】低抵抗の微細配線構造を有する半導体装置を提供する。

【解決手段】第1配線420は、半導体基板100上に設けられている。第1ビア440は、第1配線420上に設けられている。また、第1ビア440の底面は、第1配線420に接している。第1絶縁層330は、半導体基板100上に設けられ、少なくとも第1配線420の上面および第1ビア440の側面と接している。第1配線420および第1ビア440のうち各々の側面の少なくとも一部は、各々の金属の結晶粒を分断している。

(もっと読む)

3DIC方法および装置

【解決手段】 切り分けられたダイまたはウェハのような素子を3次元的に集積する方法および切り分けられたダイまたはウェハのような素子が接続された集積構造。ダイまたはウェハの一方または両方は、その中に形成された半導体デバイスを有する。第1コンタクト構造を有する第1素子は、第2コンタクト構造を有する第2素子に接着される。第1、第2コンタクト構造は、接着の際に露出されることが可能で、また接着の結果、電気的に接続される。接着後にビアがエッチングされるとともに埋め込まれて電気的配線を露出および形成して第1、第2コンタクト構造を接続するとともに、この電気的配線への表面からの電気的なアクセスが可能になる。または、第1、第2コンタクト構造は接着の際に露出されず、接着後にビアがエッチングおよび埋め込みされて第1、第2コンタクト構造が電気的に接続されるとともに接続された第1、第2コンタクト構造への電気的なアクセスが得られる。 (もっと読む)

41 - 60 / 2,609

[ Back to top ]