Fターム[5F033KK23]の内容

半導体集積回路装置の内部配線 (234,551) | 層間接続の下層配線層の材料 (17,020) | 金属及びその合金(シリサイドを除く) (9,842) | 高融点金属 (3,578) | 高融点金属の合金 (175) | TiW (132)

Fターム[5F033KK23]に分類される特許

21 - 40 / 132

半導体装置及びその製造方法

【課題】従来の半導体装置では、パッケージ端部の樹脂層の一部が剥離し、耐湿性が悪化するという問題があった。

【解決手段】本発明の半導体装置では、シリコン基板2の一主面側に再配線層5、5Aと剥離防止層6が配置され、それらを被覆するように樹脂層3が形成される。剥離防止層6は、再配線層5、5Aの無配置領域であり、半導体装置1の外周端部近傍に配置されることで、樹脂層3の樹脂量が低減される。この構造により、樹脂層3の熱収縮力に起因する樹脂の反り上がりが防止し、樹脂層3が、シリコン基板2上から剥離することが防止され、半導体装置1の耐湿性が向上される。

(もっと読む)

半導体集積回路装置の製造方法

【課題】TEG上のパッド部の浸食を防止し、また、実デバイスのパッド部の半田のぬれ性や半田形成後のシェア強度の向上を図る。

【解決手段】半導体ウエハのチップ領域CAの第3層配線M3およびスクライブ領域SAの第3層配線M3を、それぞれ、TiN膜M3a、Al合金膜M3bおよびTiN膜M3cで構成し、チップ領域CAの再配線49上の第2パッド部PAD2を洗浄し、もしくはその上部に無電界メッキ法でAu膜53aを形成する。さらに、Au膜53a形成後、リテンション検査を行い、その後、さらに、Au膜53bを形成した後、半田バンプ電極55を形成する。その結果、TiN膜M3cによってTEGであるスクライブ領域SAの第3層配線M3の第1パッド部PAD1のメッキ液等による浸食を防止でき、また、Au膜53a、53bによって第2パッド部PAD2の半田のぬれ性や半田形成後のシェア強度の向上を図ることができる。

(もっと読む)

半導体装置及びその製造方法

【課題】従来の半導体装置では、半導体基板が樹脂層により被覆されない構造のため、半導体基板端部が欠け易い問題があった。

【解決手段】本発明の半導体装置1では、シリコン基板2上面に配線層13が形成され、配線層13を被覆するように樹脂層14が形成される。配線層13上には樹脂層14の開口領域15を介してバンプ電極18が形成される。また、保護シート19は、シリコン基板2の裏面及びシリコン基板2の側面20の一部を被覆する。この構造により、シリコン基板2の裏面側では、保護シート19が緩衝材として機能し、シリコン基板2のチッピングが防止される。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体装置の再配線層において配線を狭ピッチ化して隣接する配線間距離が著しく近接しても、配線間でイオンマイグレーションを効果的に抑制する。

【解決手段】一方の主面11aに半導体デバイスおよび電極11cが設けられた半導体基板11と、一方の主面11aの上に形成された層間絶縁層12と、層間絶縁層12上において個々の配線パターンに沿って複数形成されたポリイミドからなる樹脂パターン部13と、樹脂パターン部13の上にそれぞれ形成された再配線層14と、再配線層14の上を封止する封止絶縁層15とを有し、樹脂パターン部13の側面13aが、配線パターンの長手方向に垂直な断面において凹凸状とされている。

(もっと読む)

半導体装置及びその製造方法

【課題】Cu配線層上にCuバンプを形成可能とする半導体装置を提供する。

【解決手段】半導体装置は、シリコン基板1上に形成される保護層6と、前記保護層6に形成され、前記シリコン基板1に形成される半導体素子と電気的に接続するCu配線層9と、前記Cu配線層9を被覆し、前記保護層6上に形成される樹脂膜10と、前記樹脂膜10に形成される開口領域を介して前記Cu配線層9と接続するパッド電極12と、前記パッド電極12上に形成されるCuから成るスタッドバンプ26とを有する。

(もっと読む)

半導体装置及びその製造方法

【課題】Cu配線層上にCuワイヤを実装可能とする半導体装置を提供すること。

【解決手段】本発明の半導体装置は、シリコン基板1上に形成される保護層6と、前記保護層6に形成され、前記シリコン基板1に形成される半導体素子と電気的に接続するCu配線層9と、前記Cu配線層9を被覆し、前記保護層6上に形成される樹脂膜10と、前記樹脂膜10に形成される開口領域11を介して前記Cu配線層9と接続するパッド電極12と、前記パッド電極12上にワイヤボンディングされるCuワイヤ14とを有し、前記Cuワイヤ14と前記Cu配線層9との間には合金層13が配置されることを特徴とする。

(もっと読む)

半導体装置及びその製造方法

【課題】Cu配線層上にCuワイヤを実装可能とする半導体装置を提供すること。

【解決手段】本発明の半導体装置は、シリコン基板1上に形成される保護層6と、前記保護層6に形成され、前記シリコン基板1に形成される半導体素子と電気的に接続するCu配線層9と、前記Cu配線層9を被覆し、前記保護層6上に形成される樹脂膜10と、前記樹脂膜10に形成される開口領域11を介して前記Cu配線層9と接続するパッド電極12と、前記パッド電極12上にワイヤボンディングされるCuワイヤ13とを有することを特徴とする。

(もっと読む)

半導体装置

【課題】外部から侵入する水分に起因した再配線どうしのショートが防止された半導体装置を提供する。

【解決手段】本発明の半導体装置10は、半導体基板12と、半導体基板12上に形成された第1樹脂層30と、第1樹脂層30の上面に形成されてパッド部44を構成する再配線48と、この再配線48および第1樹脂層30の上面を被覆する第2樹脂層32とを備えている。そして、パッド部44は、第2樹脂層の開口部13から露出する露出領域44Aと、第2樹脂層32により被覆される被覆領域44Bとから成り、この被覆領域44Bの幅(L1)を10μm以上としている。

(もっと読む)

表示装置

【課題】オフ電流の低減とともにオフリーク電流の低減が図れ、製造工数の増大をもたらすことなく回路の集積化が図れる薄膜トランジスタを備えた表示装置の提供。

【解決手段】表示部が形成された基板上に複数の薄膜トランジスタが形成されている表示装置であって、

前記薄膜トランジスタは、

ゲート電極と、

前記ゲート電極を跨って形成されたゲート絶縁膜と、

このゲート絶縁膜の上面に形成され、平面的に観て前記ゲート電極の形成領域内に開口が形成された層間絶縁膜と、

前記層間絶縁膜の表面に前記開口を間にして配置された一対の高濃度半導体膜と、

前記層間絶縁膜の前記開口を跨いで形成され、平面的に観て、前記ゲート電極の形成領域内に形成されるとともに前記一対の高濃度半導体膜に電気的に接続された多結晶半導体層と、

前記一対の高濃度半導体膜のそれぞれに重ねられ前記多結晶半導体膜に重ねられることなく形成された一対の電極と、

を備えたものを含む。

(もっと読む)

半導体装置、半導体装置の製造方法、及び電子機器

【課題】端子間の接合性に優れ高い信頼性を備えたものにするとともに、端子の狭ピッチ化も容易に対応できる半導体装置、半導体装置の製造方法、及び電子機器を提供する。

【解決手段】本発明の半導体装置1は、半導体基板10と、半導体基板10に形成された貫通孔7内に設けられるとともに、半導体基板10の能動面10Aと反対側の裏面10Bに部分的に突出する貫通電極5と、を有し、貫通電極5は、樹脂コア9と、樹脂コア9の少なくとも一部を覆う導電膜15と、を有し、貫通孔7は、内壁面7aの少なくとも一部が能動面10A側に向かって貫通孔7の内径を狭めるテーパー形状となっている。

(もっと読む)

半導体装置及びその製造方法

【課題】ウェハ面内の再配線層の厚みのばらつきを低減し、所望の電気的特性を得ることのできる多層再配線構造を有するWCSP型の半導体装置及びその製造方法を提供する。

【解決手段】第1の再配線層を形成する工程において、第1の導電材料をめっき法により成長させて第1の再配線層より厚い第1の導電材料層を形成し、第1のレジスト膜及び第1の導電材料層を主面側から研磨して表面を平坦化して、第1の再配線層を形成する処理、及び、第2の再配線層を形成する工程において、第2の導電材料をめっき法により成長させて第2の再配線層より厚い第2の導電材料層を形成し、第2のレジスト膜及び第2の導電材料層を主面側から研磨して表面を平坦化して、第2の再配線層を形成する処理の少なくとも一方の処理を行う。

(もっと読む)

電子装置、電子装置の製造方法、電子機器

【課題】端子間の接合性に優れ高い信頼性を備えたものにするとともに、端子の狭ピッチ化も容易に対応できる電子装置、電子装置の製造方法、電子機器を提供する。

【解決手段】本発明の半導体装置1は、半導体基板10と、半導体基板10に形成された貫通孔7内に設けられるとともに半導体基板10の能動面10A側に部分的に突出する貫通電極5と、を有し、貫通電極5は、樹脂コア9と、樹脂コア9の少なくとも一部を覆う導電膜15と、を有する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】半導体基板に設けられる貫通孔および貫通電極の形成状態および出来映えを容易に確認可能にし、貫通孔および貫通電極の品質向上と、接続不良の早期発見を可能にする技術を提供する。

【解決手段】半導体基板11と、半導体基板11の表面に設けられた内部電極12Aおよび内部電極12Bと、半導体基板11を厚み方向に貫通して内部電極12Aに到達し、内部電極12Aと電気的に接続された第一の貫通電極17Aと、半導体基板11および内部電極12Bを厚み方向に貫通する第二の貫通電極17Bと、半導体基板11の裏面に設けられ、第一の貫通電極17Aと電気的に接続された金属配線18とを備える。

(もっと読む)

半導体装置およびその製造方法

【課題】 従来のエアギャップ構造より、さらに容量及び容量ばらつきを低減することができる。

【解決手段】 基板上の絶縁膜17上に、銅を主成分として含む配線26を形成する。それから、リザーバーパターン用絶縁膜21、22及びバリア絶縁膜29を形成し、配線26の上面および側面上と絶縁膜17及び絶縁膜29上に銅の拡散を抑制または防止する機能を有する絶縁膜31を形成する。このとき、狭い配線間スペース底部の絶縁膜17の膜厚保は、配線26上の絶縁膜31の膜厚より、薄く成膜することで細線ピッチの配線容量を効率良く低減する。その後、低誘電率からなる絶縁膜36及び絶縁膜37を成膜する。その際、配線26の隣接配線間において、対向する配線側面の上方での堆積速度が下方での堆積速度より大きくなるように絶縁膜36を形成し、エアギャップを形成する。最後に、層間CMPによって、絶縁膜37を平坦化する。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体基板に形成される貫通孔底部での絶縁層のノッチの発生、貫通孔下の配線層へのダメージを抑制し、電気的絶縁性の低下や配線層の接続不良を低減できる半導体装置及びその製造方法を提供する。

【解決手段】第一の絶縁層203と、第一の絶縁層上の第一の配線層204と、半導体基板201を貫通し、底部に第一の絶縁層を厚さ方向に除去した部分的なエッチ部を備えた貫通孔201aと、貫通孔の部分的なエッチ部の底部を除く内壁部から半導体基板の第二の面までを覆う第二の絶縁層206と、貫通孔の底部に、第一の配線層が露出するように第一の絶縁層に形成された開口部203aと、該開口部で第一の配線層と接すると共に貫通孔の第二の絶縁層上から半導体基板の第二の面の第二の絶縁層上に亘る第二の配線層202とを有し、開口部に接する第一の絶縁層が、半導体基板に接する第一の絶縁層より小さい厚さを有する。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体装置の信頼性を向上させることができる製造方法を提供する。

【解決手段】半導体基板1に形成される半導体素子を覆う絶縁膜11が、埋め込み特性が良好とされる熱CVD法等によって形成される。その絶縁膜11を覆うように、耐湿性に優れているとされるプラズマCVD法によって絶縁膜14が形成される。その絶縁膜11および絶縁膜14を貫通するようにプラグ13が形成される。さらに、その絶縁膜14上に、誘電率が比較的低いLow−k膜からなる絶縁膜16が形成され、その絶縁膜16に、ダマシン技術によって、プラグ13に電気的に接続される配線20が形成される。

(もっと読む)

半導体集積回路装置およびその製造方法

【課題】TEG上のパッド部の浸食を防止し、また、実デバイスのパッド部の半田のぬれ性や半田形成後のシェア強度の向上を図る。

【解決手段】半導体ウエハのチップ領域CAの第3層配線M3およびスクライブ領域SAの第3層配線M3を、それぞれ、TiN膜M3a、Al合金膜M3bおよびTiN膜M3cで構成し、チップ領域CAの再配線49上の第2パッド部PAD2を洗浄し、もしくはその上部に無電界メッキ法でAu膜53aを形成する。さらに、Au膜53a形成後、リテンション検査を行い、その後、さらに、Au膜53bを形成した後、半田バンプ電極55を形成する。その結果、TiN膜M3cによってTEGであるスクライブ領域SAの第3層配線M3の第1パッド部PAD1のメッキ液等による浸食を防止でき、また、Au膜53a、53bによって第2パッド部PAD2の半田のぬれ性や半田形成後のシェア強度の向上を図ることができる。

(もっと読む)

半導体装置とその製造方法

【課題】半導体基板の表裏両面間を貫通電極で接続するにあたって、貫通孔底部の角部におけるリーク電流の発生や絶縁膜のクラック等を抑制する。

【解決手段】半導体装置1は貫通孔3を有する半導体基板2を備える。貫通孔3は半導体基板2の第1の面2aに開口された第1の開口3aの開口径が第2の面2bに開口された第2の開口3bに近い側の内径より大きくなるように、第1の面2aの近傍を拡張させる拡張部4を備える。半導体基板2の第1の面2aには第1の絶縁層5と第1の配線層6とが設けられている。貫通孔3には拡張部4を充填しつつ内壁面を覆う第2の絶縁層7が設けられており、さらに第1および第2の絶縁層5、7の開口を介して第1の配線層6と接続された第2の配線層8が設けられている。

(もっと読む)

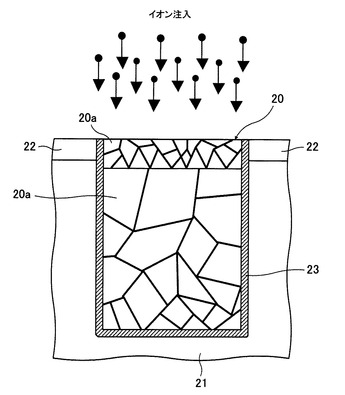

半導体装置の製造方法

【課題】配線のエレクトロマイグレーション耐性を向上させる。

【解決手段】めっき法を用いてCu配線20を形成する際、まず第1の電流密度の条件で第1の平均粒径を有する第1の金属膜を形成し、次いで、第1の電流密度よりも高い第2の電流密度の条件で第1の平均粒径よりも大きい第2の平均粒径を有する第2の金属膜を形成する。その後、第1,第2の金属膜の上部に所定元素を導入し、導入後、第1,第2の金属膜上にキャップ膜を形成する。

【選択図】図5  (もっと読む)

(もっと読む)

半導体装置及び回路基板

【課題】小型の半導体装置においても静電容量の大きなキャパシタを配置することが可能な構造を有する半導体装置を提供する。

【解決手段】半導体装置1は、半導体素子8が形成された半導体基板2と、半導体基板2のパッシベーション膜12を介して配置され1方向に長く形成された開口部4aを有する平面型のスロットアンテナ4と、スロットアンテナ4と並列接続する共振用キャパシタ15とを備え、共振用キャパシタ15はチップ型素子となっている。

(もっと読む)

21 - 40 / 132

[ Back to top ]