Fターム[5F033KK23]の内容

半導体集積回路装置の内部配線 (234,551) | 層間接続の下層配線層の材料 (17,020) | 金属及びその合金(シリサイドを除く) (9,842) | 高融点金属 (3,578) | 高融点金属の合金 (175) | TiW (132)

Fターム[5F033KK23]に分類される特許

41 - 60 / 132

半導体装置

【課題】 容量低減とビア加工マージンの確保を効率的に達成する。

【解決手段】 複数の配線層を有する半導体装置であって、所定領域を有する第1配線層26と、第1配線層の上層に位置する第2配線層47と、第1配線層と第2配線層との間に設けられる層間絶縁膜36と、層間絶縁膜と第1配線層の配線との間に設けられるバリア絶縁膜(29,31)とを有し、所定領域における配線上部のバリア絶縁膜の厚さは、所定領域以外の領域における配線上部のバリア絶縁膜の厚さよりも厚く、所定領域においては隣接する配線間にエアギャップ35が形成され、所定領域以外においては隣接する配線間にエアギャップが形成されない。

(もっと読む)

光電変換装置及び撮像システム

【課題】プラグに対する信号配線層の接続抵抗を低減しながら暗電流を抑制する。

【解決手段】光電変換装置は、光電変換部と、前記光電変換部の上方に設けられ、画素における少なくとも前記光電変換部を除く領域を遮光する遮光層と、前記光電変換部で発生した電荷を電圧に変換する半導体領域と、前記半導体領域又は配線層にプラグを介して接続された信号配線層と、前記遮光層の下面に沿って配された第1のバリアメタル層と、前記信号配線層の上面又は下面に沿って前記信号配線層と前記プラグとの間に配された第2のバリアメタル層とを備え、前記第1のバリアメタル層は、前記光電変換部における暗電流を抑制するように、前記第2のバリアメタル層より水素吸蔵能力の低い材料で形成されており、前記第2のバリアメタル層は、前記信号配線層と前記プラグとの接続抵抗を低減するように、前記第1のバリアメタル層より比抵抗の小さい材料で形成されている。

(もっと読む)

半導体装置、通信モジュールおよび電子機器

【課題】安定した利得が得られるアンテナ素子を備えた半導体装置、通信モジュールおよび電子機器を提供すること。

【解決手段】半導体装置10は、能動素子が形成された能動面1aを有する半導体基板1と、能動面1a上に少なくとも1層以上の絶縁性樹脂層を介して設けられた第1の配線層8と、第1の配線層8に形成されたスロットアンテナ11と、スロットアンテナ11に接続された共振用キャパシタ13とを備え、スロットアンテナ11は、矩形状の開口部11bを有する平面型のアンテナ素子である。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】貫通孔底部にノッチを有する半導体装置のノッチ部に被覆性良好な連続した金属膜を積層するプロセスを提供し、半導体装置の歩留まりと信頼性向上をはかること。

【解決手段】ノッチ部を含む貫通孔にCVD絶縁膜を積層した後に、バリア層およびシード層のメタル層をスパッタ法により形成する。メタル層のスパッタ成膜中に基板バイアス(負電圧)を印加して、アルゴンやクリプトン等の希ガスのプロセスガスイオンを貫通孔内部へ引き込み、既にある程度貫通孔底部に積層したメタル層をスパッタエッチングするか、貫通孔底部にメタル層を積層すると同時にスパッタエッチングしたメタル材料を貫通孔底部周辺のノッチ部分へ飛散させる。飛散したメタル材料はノッチ部分の絶縁膜上に付着し積層する。Ar+イオン等により飛散されたメタルは高いエネルギーを有する為、メタル層がノッチ内部へ強固に付着する。

(もっと読む)

相変化メモリデバイスに電極を形成する方法

サブリソグラフィックな寸法又は高アスペクト比を含む、小寸法の開口内に電極材料を均一に形成する方法を提供する。この方法は、内部に形成された開口を有する絶縁層を提供するステップと、開口の上部及び内部に非等質的導電又は準抵抗性材料を形成するステップと、導電材料を移動化して開港内に圧縮するステップとを有する。この方法は、導電又は準抵抗性材料における空孔又は欠陥密度を堆積されたままの状態に対して低減する。移動化するステップは、押出又は熱的リフローによって達成され、空隙又は欠陥を合体、崩壊、染み透り又は他の方法によって堆積したままの導電又は準抵抗性材料から除去する。  (もっと読む)

(もっと読む)

半導体装置

【課題】合計長が長くなることにより抵抗値が大きくなり、また、表皮効果により、実施的な抵抗値が大きくなった。

【解決手段】インダクタを含む半導体装置であって、前記インダクタは、(1)第1の導体と、当該第1の導体の表面に形成されている、前記第1の導体より導電性が高い第2の導体と備える渦巻状の巻線本体と、(2)第3の導体と、当該第3の導体の表面に形成されている、前記第3の導体より導電性が高い第4の導体とを備え、前記巻線本体の両端部のうち中心側の端部を起点として外側に向けて延在する配線と、(3)前記巻線本体の中心側の端部と前記配線の中心側の端部とを斜めに接続するビアと、を有する。

(もっと読む)

半導体装置の製造方法

【課題】ウエハレベルCSPにおいて、傾斜面を有する樹脂ポストが存在する場合であっても、樹脂ポスト近辺に微細な再配線を設計どおりに高密度に形成することができ、チップの小型化及び端子数の増加に対応することが可能な半導体装置の製造方法を提供する。

【解決手段】本発明に係る半導体装置の製造方法は、少なくとも一面に電極3を備えた基板2上の所定位置に、面状をなす第一頂部4aを備えた突起状の第一樹脂ポスト4を形成する工程αと、前記第一樹脂ポストの第一頂部上に、該第一頂部の一部を少なくとも露出させるように、該第一頂部よりも小さい面状をなす第二頂部5aを備えた突起状の第二樹脂ポスト5を形成する工程βと、を少なくとも備えたことを特徴とする。

(もっと読む)

半導体装置及びその製造方法

【課題】Cu膜からなる配線層と封止樹脂層との密着性を向上させ、両層間での剥離を防止し信頼性の高い半導体装置を提供する。

【解決手段】本発明に係る半導体装置1A(1)は、一面に電極3を配してなる半導体基板2と、前記半導体基板の一面を覆うように配され、前記電極と整合する位置に電極用の開口部αを有する絶縁樹脂層4と、前記絶縁樹脂層の一部を覆うように配され、前記開口部αを通して前記電極と電気的に接続される配線層5と、を少なくとも備える半導体装置であって、前記配線層は、Cu膜からなり、該配線層の表面が10nm〜300nmの凹凸形状を有することを特徴とする。

(もっと読む)

寄生容量が減らされた半導体デバイス

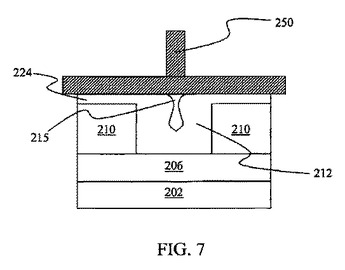

【課題】高速ショットキーデバイス及びpn接合デバイスにおける寄生容量を低減すると共にボンディング強度を改善する。

【解決手段】基板303と、基板303の上に配置される半導体デバイス300、302、及び半導体デバイス300、302との電気的接触を行うボンディング用パッド307を有し、ベンゾシクロブテンの層304が半導体デバイスの周辺に設けられ、ボンディング用パッド307がベンゾシクロブテンの層304の頂面に設けられる。

(もっと読む)

多層配線の形成方法

【課題】実効的な低配線間容量を維持しつつ、高密着性かつ高い配線間絶縁信頼性を有する多層配線の形成方法を提供する。

【解決手段】本発明に係る多層配線の形成方法は、シロキサン構造を含むビア層間絶縁膜43及び配線層間絶縁膜44を金属配線41a上に形成する第一の工程(図1[1])と、ビア層間絶縁膜43及び配線層間絶縁膜44の一部に金属配線41aに達する凹部としてのデュアルダマシン溝48を形成する第二の工程(図1[2]〜図2[2])と、ビア層間絶縁膜43及び配線層間絶縁膜44とデュアルダマシン溝48内で露出した金属配線41aとに水素プラズマ処理を施すことにより、ビア層間絶縁膜43及び配線層間絶縁膜44の表面に改質層49を形成するとともに金属配線金属配線41aの表面を還元する第三の工程(図3[1])と、を含むことを特徴とする。

(もっと読む)

半導体装置及び電子機器

【課題】アンテナが半導体チップの回路に及ぼす悪影響を最小限に抑えることができる半導体装置、電子機器の提供。

【解決手段】半導体装置は、集積回路12が形成される半導体チップ10と、少なくとも1つのスロット52を有し、半導体チップ10の主面13に直交する方向を第1の方向D1とした場合に半導体チップ10の第1の方向D1に少なくとも絶縁層30を介して設けられ、半導体チップ10の集積回路12に電気的に接続されるスロットアンテナ50と、を含む。

(もっと読む)

半導体装置の製造方法

【課題】貫通電極の導通確認をウェハ単位で簡便に行なうことができる半導体装置の製造方法を提供すること。

【解決手段】シリコンウェハ250の能動面10aに形成された複数の集積回路を個片化して複数の半導体装置1を製造する方法であって、複数の集積回路を個片化する前に、集積回路のそれぞれに形成された能動面電極120a,120b,外部接続用電極122,及びダミー電極を覆って導電膜190を形成する工程と、能動面10aと反対の裏面10bからシリコンウェハ250を貫通して能動面電極120a,120bに達する貫通電極112a,112bを形成する工程と、裏面10bから一対の貫通電極112a,112bをプロービングして貫通電極112a,112bと能動面電極120a,120bとの導通を検査する工程と、を有することを特徴とする半導体装置の製造方法とした。

(もっと読む)

半導体装置及びその製造方法

【課題】従来の半導体装置では、層間絶縁層のSOG膜から発生する脱ガスにより接続用電極が酸化し、接続用電極上の抵抗値が低減され難いという問題があった。

【解決手段】本発明の半導体装置では、接続用電極26上のTEOS膜27、SiN膜28に開口領域29、33が形成される。開口領域29、33では、接続用電極26上にメッキ用金属層34、Cuメッキ層36が積層される。そして、接続用電極26が開口領域29、33から露出する際、SOG膜14、22が露出することがなく、接続用電極26がSOG膜14、22から発生する脱ガスにより酸化されず、接続用電極26上の抵抗値が低減される。

(もっと読む)

半導体装置及びその製造方法

【課題】従来の半導体装置では、層間絶縁層のSOG膜から発生する脱ガスにより接続用電極が酸化し、接続用電極上の抵抗値が低減され難いという問題があった。

【解決手段】本発明の半導体装置では、接続用電極26上のTEOS膜27、SiN膜28に開口領域29、31が形成される。開口領域29、31では、接続用電極26上にメッキ用金属層32、Cuメッキ層34が積層される。そして、接続用電極26が開口領域29、31から露出する際、SOG膜14、22が露出することがなく、接続用電極26がSOG膜14、22から発生する脱ガスにより酸化されず、接続用電極26上の抵抗値が低減される。

(もっと読む)

半導体装置およびその製造方法

【課題】高耐圧の半導体装置に対する小型化要求と電極配線の信頼性確保を両立するため、高温封止工程に耐えうる電極配線を持った半導体装置を提供する。

【解決手段】本発明の半導体装置は、シリコン単結晶基板の主表面に形成された1つ以上の半導体素子と、シリコン単結晶基板の前記主表面上に形成された層間絶縁層と、前記層間絶縁層上に形成され前記半導体素子に電力を供給する電極配線を有する半導体装置であって、前記電極配線は前記層間絶縁層に形成されたコンタクトホールを介して前記半導体素子に接続されており、酸化アルミニウム保護層が前記電極配線の表面に形成されており、パシベーション膜が前記電極配線を被覆するように形成されている。

(もっと読む)

半導体装置及びその製造方法

【課題】従来の半導体装置では、層間絶縁層のSOG膜から発生する脱ガスにより接続用電極が酸化し、接続用電極上の抵抗値が低減され難いという問題があった。

【解決手段】本発明の半導体装置では、接続用電極26上のTEOS膜27、SiN膜28に開口領域29が形成される。開口領域29では、接続用電極26上にメッキ用金属層34、Cuメッキ層36が積層される。そして、接続用電極26が開口領域29から露出する際、SOG膜14、22が露出することがなく、接続用電極26がSOG膜14、22から発生する脱ガスにより酸化されず、接続用電極26上の抵抗値が低減される。

(もっと読む)

半導体装置とその製造方法

【課題】半導体基板の表裏両面間を貫通配線層で接続した半導体装置において、グランド特性や放熱性を改善する。

【解決手段】半導体装置1は貫通孔3を有する半導体基板2を備える。半導体基板2の第1の主面2aには活性層4が設けられている。貫通孔3の内壁面、活性層4で塞がれた貫通孔3の底面、および半導体基板2の第2の主面2bは絶縁層5で覆われている。貫通孔3の底面に存在する絶縁層5には第1の開口部6が設けられている。半導体基板2の第2の主面2bに存在する絶縁層5には第2の開口部7が設けられている。第1の配線層8は貫通孔3内から半導体基板2の第2の主面2bに亘って設けられている。第2の配線層9は第2の開口部7を介して第2の主面2bと接続するように設けられている。

(もっと読む)

半導体装置及びその製造方法

【課題】微小ビアでの接続信頼性を確保した信頼性の高い半導体装置を提供すること。

【解決手段】半導体基板11と、半導体基板11上に配されるとともに、少なくとも1以上の第1配線層、少なくとも1以上の第1絶縁層、及び第1ビアを有する第1配線構造体12と、第1配線構造体12上に配されるとともに、少なくとも1以上の第2配線層15、少なくとも1以上の第2絶縁層14、第2ビア16、及び第3ビア19を有する第2配線構造体17と、第2配線構造体17上に設けられた外部端子18と、を備える半導体装置において、第2配線構造体17の第2配線層15と外部端子18に接合される第2ビア16は、外部端子18側の端部に接合界面16aが配されている。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】半導体基板の貫通接続部において、表面側配線層の貫通孔底部での剥離および破断が防止され、接続不良等が改善された半導体装置と、そのような半導体装置を製造する方法を提供する。

【解決手段】貫通孔3を有する半導体基板2の表面に、該貫通孔3と同径の開口4aを有する第1の絶縁層4が被覆され、その上に第1の配線層5が開口4aを覆い形成されている。また、貫通孔3内および半導体基板2の裏面に第2の絶縁層6が被覆されている。第2の絶縁層6は、第1の配線層5と内接するように形成され、内接部に第1の絶縁層4の開口4aよりも小径の複数の開口6aを有している。さらに、貫通孔3内に第2の配線層7が充填・形成され、この第2の配線層7は第2の絶縁層6の複数の開口6aを介して第1の配線層5に内接している。

(もっと読む)

半導体装置の製造方法

【課題】製造時における半導体素子へのプラズマダメージの影響を小さくすることができる半導体装置の製造方法を提供する。

【解決手段】半導体基板上に半導体素子を形成する工程と、マイクロ波をプラズマ源とし、半導体基板の表面近傍において、プラズマの電子温度が1.5eVよりも低く、かつプラズマの電子密度が1×1011cm−3よりも高いマイクロ波プラズマを用いたCVD処理によって半導体素子上に膜を形成する工程とを含む。

(もっと読む)

41 - 60 / 132

[ Back to top ]