Fターム[5F033LL02]の内容

半導体集積回路装置の内部配線 (234,551) | 導電膜材料の特徴点 (1,721) | 不純物、イオンを含むもの (1,142) | 金属 (317)

Fターム[5F033LL02]に分類される特許

181 - 200 / 317

半導体のマイクロパッド形成

第1の半導体素子(12,52,74)の外部コンタクト(14,54,78)に達するマイクロパッド(30,70,42)を形成する方法である。銅から成るスタッド(20,24,66,88,82)を外部コンタクトの上に形成する。スタッドは、第1の半導体素子の表面上を延在する。銅から成るスタッドを錫溶液に浸漬する。錫(28)で、スタッドの銅の少なくとも95パーセントを、好ましくは99パーセント超を置換する。結果として、5重量パーセント未満の銅を含む錫マイクロパッドが得られる。マイクロパッドがほぼ純粋な錫であるので、金属間化合物ボンドは、第1の半導体素子のマイクロパッドがボンディングされない状態が続いている間は形成されない。より小さいマイクロパッド寸法が、金属間化合物ボンドが形成されないので得られる。第1の半導体素子を、当該第1の半導体素子に覆い被さる第2の半導体素子にボンディングする場合、ボンド寸法によって、積層チップの高さが極めて高くなることはない。  (もっと読む)

(もっと読む)

スパッタターゲットの製造方法

【課題】ヒロック、エッチング残渣、ITO等との電気化学反応の発生を防止した低抵抗な配線膜を再現性よく成膜することができ、かつスパッタ時におけるダスト発生を抑制したスパッタターゲットの製造方法を提供する。

【解決手段】Y、Sc、La、Ce、Nd、Sm、Gd、Tb、Dy、Er、Th、Sr、Ti、Zr、V、Nb、Ta、Cr、Mo、W、Mn、Tc、Re、Fe、Co、Ni、Pd、Ir、Pt、Cu、Ag、Au、Cd、Si、PbおよびBから選ばれる少なくとも1種の第1の元素を0.001〜30原子%の範囲で含み、残部がAlからなるインゴットまたは焼結体を、大気溶解法、真空溶解法、急冷凝固法、粉末冶金法で作製するにあたって、インゴットまたは焼結体にCを第1の元素量に対して20原子ppm〜37.8原子%の範囲で含有させ、得られたインゴットや焼結体を加工してスパッタターゲットを作製する。

(もっと読む)

薄膜トランジスタパネルの製造方法

【課題】 液晶表示装置の薄膜トランジスタパネルにおいて、比較的簡単な方法により、ゲート配線の上面による外光反射に起因するコントラスト低下を抑制する。

【解決手段】 ゲート電極2およびゲート配線3を、Alを主成分としてNiを含有するAl合金によって形成し、それらの上面に変色用処理液を用いて変色層2a、3aを形成すると、変色層2a、3aの反射率がAl合金の反射率よりも低くなるので、ゲート配線3の上面による外光反射に起因するコントラスト低下を抑制することができる。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】層間絶縁膜上に析出しためっき成分を選択的に除去して、埋め込み配線を有する半導体装置を提供する。

【解決手段】半導体装置の製造方法が、半導体基板上に層間絶縁膜を形成する工程と、層間絶縁膜にトレンチを形成する工程と、層間絶縁膜の表面およびトレンチの内部を覆うように、バリアメタル層を形成する工程と、バリアメタル層の上に、トレンチを埋め込むように銅からなる金属層を形成する工程と、層間絶縁膜上の金属層とバリアメタル層とを、CMP法を用いて除去し、バリアメタル層と金属層をトレンチ内に残す工程と、金属層の上にキャップメタル層を形成する工程と、熱処理によりキャップメタル層の材料を金属層内に拡散させ、キャップメタル層の下部にキャップ拡散層を形成する工程と、CMP法を用いてキャップメタル層を除去し、キャップ拡散層で被覆された金属層をトレンチ内に残して配線層とする工程とを含む。

(もっと読む)

画像表示装置

【課題】Al合金の配線を用いた画像表示装置において、ヒロックが発生せず、かつ、配線内にボイドが形成されないAl合金の配線を形成する。

【解決手段】下部電極112とトンネル絶縁膜115と薄膜電極117によってMIM電子源114が形成される。トンネル絶縁膜115は下部電極112を陽極酸化することによって形成する。下部電極112は信号線131の上に形成される。信号線131はヒロックを防止するために、Ndを添加するが、Ndの添加量を基板111側から連続的に減少させる。その結果トンネル絶縁膜は純Alを陽極酸化した質の良い絶縁膜とすることが出来る。また、本発明では信号線131膜内に界面は形成されず、界面に起因したボイドの発生も無い。

(もっと読む)

配線構造および半導体装置

【課題】電気を流すことができる。

【解決手段】基板11と、基板11上に形成された、開口孔を有する絶縁膜12と、開口孔の底部に形成された、内部にアルカリ金属原子(またはハロゲン原子)16aを有する筒状炭素構造体14と、を有する配線構造10により、基板11と、基板11上に形成された、開口孔を有する絶縁膜12と、開口孔の底部に形成された、内部にアルカリ金属原子(またはハロゲン原子)16aを有する筒状炭素構造体14とにより、筒状炭素構造体14が金属性を示す。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】電極の接触抵抗の低減によって高性能化した半導体装置の製造方法および半導体装置を提供する。

【解決手段】半導体基板上にゲート絶縁膜を形成する工程と、ゲート絶縁膜上にゲート電極を形成する工程と、半導体基板上に第1の金属を堆積する工程と、第1の熱処理により第1の金属と半導体基板を反応させて、前記ゲート電極両側の前記半導体基板表面に金属半導体化合物層を形成する工程と、金属半導体化合物層中に、Siの原子量以上の質量を有するイオンをイオン注入する工程と、金属半導体化合物層上に第2の金属を堆積する工程と、第2の熱処理により、第2の金属を金属半導体化合物層中に拡散させることで、金属半導体化合物層と半導体基板の界面に、第2の金属を偏析させて界面層を形成する工程を有することを特徴とする半導体装置の製造方法。

(もっと読む)

電気光学素子および該電気光学素子の製造方法

【課題】AlあるいはAl合金など腐食しやすい金属を補助容量配線に用いた電気光学素子の製造方法において、後続画素エッチング工程における補助容量配線の腐食断線を防止する。

【解決手段】電気光学素子では、対向配置された一対の基板間に電気光学材料が挟持されており、一方の基板上に形成されたゲート配線と、ゲート配線と同一層で形成され、互いに分離された第1の金属薄膜で形成された複数の補助容量配線と、複数の補助容量配線と互いに分離されている集合引出し配線とを備える。

(もっと読む)

積層導電膜、電気光学表示装置及びその製造方法

【課題】ITO等の酸化物透明導電膜の上に直接、光反射率が高いAl系合金膜を成膜した欠陥のない積層導電膜を提供すること。

【解決手段】本発明の一態様に係る積層導電膜は、光透過性を有する透明導電膜と、前記透明導電膜上に直接積層して形成され、前記透明導電膜との界面近傍に窒素原子、酸素原子の少なくとも1種類以上を含むことにより、前記透明導電膜に電気的に接続されるAl又はAlを主成分とするメタル導電膜とを有する。また、メタル導電膜は、透明導電膜との界面近傍にさらに周期律の8族元素のFe、Co、Ni、4b族元素のC、Si、Geから選ばれる少なくとも1種類以上の原子を含む。

(もっと読む)

埋め込み配線の形成方法

【課題】配線抵抗が低く、EM耐性及び信頼性に優れた埋め込み配線の形成方法を提供することにある。

【解決手段】半導体基板10上に形成された絶縁層11内に溝12を形成した後、溝12の側面及び底面を覆うように、絶縁層11上にALD法でバリアメタル層13を形成し、その表面に、イオン注入法またはALD法により不純物層14、17を形成する。その後、バリアメタル層13と不純物層14、17とを合金化した後、溝12内にCuシード層15及びCuメッキ層16からなる埋め込み配線層を形成し、然る後、合金化されたバリアメタル層13内の不純物元素を埋め込み配線層内に熱拡散させる。

(もっと読む)

半導体装置の製造方法

【課題】多層配線構造のバリアメタル膜の欠陥を、CuMn層のMnと層間絶縁膜との自己形成反応による拡散バリア膜で補間する半導体装置の製造方法において、CuMn層上のCu層の比抵抗を低減する半導体装置の製造方法を提供する。

【解決手段】層間絶縁膜の上面と、凹部の側壁面および底面を含めて、第1金属元素を含みCuの拡散防止膜として作用する第1導電膜26を形成し、第1導電膜を、CuおよびCuとは異なる第2金属元素を含む第2導電膜26Mにより覆い、第1および第2導電膜を介して、Cuを主成分とする配線層27を堆積し、配線層を熱処理して第2導電膜中の第2金属元素を、欠陥部分26Xにおいて露出された表面部分と反応させ、Cuの拡散防止化合物を形成し、反応に使われなかった余剰の第2金属元素を、配線層を介して、配線層表面27Mまで拡散させる。前期熱処理は、配線層の温度を7℃/秒未満の平均昇温速度で昇温させる。

(もっと読む)

金属粒子分散液、金属粒子分散液の製造方法、導電膜形成基板の製造方法、電子デバイスおよび電子機器

【課題】分散媒中での分散性および安定性に優れ、配線、導電性パターン等の導電膜として加工する際に紫外線照射を併用することで焼成温度を低く抑えることのできる金属粒子分散液を提供すること、前記金属粒子分散液を容易かつ確実に製造することができる金属粒子分散液の製造方法を提供すること、性能、信頼性に優れた導電膜形成基板の製造方法、性能、信頼性に優れた電子デバイスおよび電子機器を提供すること。

【解決手段】本発明の金属粒子分散液は、硫黄原子を含む化合物と、貴金属材料を含む材料で構成され、粒径が1〜100nmの金属粒子と、分散媒とを含み、金属粒子が前記化合物で被包されていることを特徴とする。金属粒子は、主としてAgで構成されたものであるのが好ましい。

(もっと読む)

電界効果トランジスタ、半導体チップ及び半導体装置

【課題】均一性や生産性が高いと共に、高周波性能として、雑音指数が小さく、かつ付随利得の大きい電界効果トランジスタ(FET)、このFETを備える半導体チップ及び半導体装置を提供すること。

【解決手段】本発明のFET1は、GaAs半導体基板2の上に、i形GaAsバッファ層3と、i形InGaAs二次元電子ガス層4と、n形AlGaAs電子供給層5と、が積み上げられ、n形AlGaAs電子供給層5の上に線状にショットキー性接触するゲート電極12があり、ゲート電極12の両横から離れ、かつn形AlGaAs電子供給層5の上に、n形InGaPエッチング停止層6と、続いて同程度の横位置でn形GaAsコンタクト層7とが積み上げられ、n形GaAsコンタクト層7の上にコンタクト層7の端から離れて帯状にオーム性接触をする電極として各側にソース電極9とドレイン電極10とを備える。

(もっと読む)

Al合金膜、電子デバイス及び電気光学表示装置用アクティブマトリックス基板

【課題】ITOやSiとの界面拡散を防止するとともに、低温プロセスが要求される各種電子デバイスに適用可能な低抵抗の電極膜用Al合金膜を提供すること。

【解決手段】本発明の一態様に係るAl合金膜は、Niからなる第1の添加元素と、元素周期表の周期2又は3に属する2a族のアルカリ土類金属、3b、4b族の半金属から選ばれる少なくとも1種類以上の第2の添加元素とを含む。また、第1の添加元素の組成比は0.5〜5at%であり、第2の添加元素の組成比は0.1〜3at%である。

(もっと読む)

厚さが減少した半導体素子、これを採用する電子製品及びその製造方法

【課題】厚さが減少した半導体素子、これを採用する電子製品及びその製造方法を提供する。

【解決手段】この半導体素子の製造方法は第1及び第2活性領域を有する半導体基板を準備する工程を含む。前記第1活性領域に第1ゲートパターン及び第1不純物領域を含む第1トランジスタを形成する。前記第2活性領域に第2ゲートパターン及び第2不純物領域を含む第2トランジスタを形成する。前記第1トランジスタ上に第1導電性パターンを形成する。前記第1導電性パターンの少なくとも一部と前記第2ゲートパターンの少なくとも一部は前記半導体基板の上部表面から同一距離に配置される。前記第1導電性パターンは前記第2ゲートパターンを形成する間に形成される。

(もっと読む)

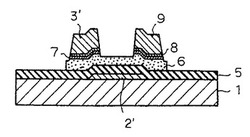

薄膜トランジスター

【課題】薄膜トランジスターを提供する。

【解決手段】ガラス基板1の上にゲート電極膜2を形成し、前記ガラス基板1およびゲート電極膜2の上に窒化珪素膜3を形成し、前記窒化珪素膜3の上にアモルファスSi膜4を形成し、前記アモルファスSi膜4の上にバリア膜を介していずれもCu−O−Zn銅合金膜15の下地層を有するCu−Zn銅合金からなるドレイン電極膜5およびソース電極膜6を形成し、前記アモルファスSi膜4、ドレイン電極膜5およびソース電極膜6の上に窒化珪素膜3´を被覆形成してなる薄膜トランジスターにおいて、前記バリア膜は、Cu−Si−O−Zn銅合金膜19で構成されていることを特徴とする。

(もっと読む)

基板配線用導電性組成物、回路基板及び電子デバイス

【課題】貫通電極又は回路パターンの凝固収縮に起因する問題を解決しえる基板配線用導電性組成物、回路基板、及び、電子デバイスを提供すること。

【解決手段】50wt%以上のビスマス(Bi)と、30wt%以下のインジウム(In)と、30wt%以下の錫(Sn)と、1〜5wt%の範囲で選択された銅(Cu)とを含有する導電性組成物によって、貫通電極3及び回路パターン2を形成する。Biの体積膨張特性を利用することにより、課題を解決することができる。

(もっと読む)

薄膜トランジスター

【課題】薄膜トランジスターを提供する。

【解決手段】ガラス基板1の上にゲート電極膜2を形成し、前記ガラス基板1およびゲート電極膜2の上に窒化珪素膜3を形成し、前記窒化珪素膜3の上にアモルファスSi膜4を形成し、前記アモルファスSi膜4の上にバリア膜を介していずれもCu−O−AEM(アルカリ土類金属)銅合金膜15の下地層を有するCu−AEM(アルカリ土類金属)銅合金からなるドレイン電極膜5およびソース電極膜6を形成し、前記アモルファスSi膜4、ドレイン電極膜5およびソース電極膜6の上に窒化珪素膜3´を被覆形成してなる薄膜トランジスターにおいて、前記バリア膜は、Cu−Si−O−AEM(アルカリ土類金属)銅合金膜19で構成されていることを特徴とする。

(もっと読む)

貫通配線基板の製造方法

【課題】貫通配線基板を他基板に実装する際には圧力と熱が掛かる場合でも、貫通配線基板及び被実装物の耐久性を向上せしめた貫通配線基板の製造方法を提供する。

【解決手段】基板に設けられた貫通孔に貫通配線を備える貫通配線基板の製造方法において、基板部材7の両面に絶縁層9を形成する工程と、基板部材7下面の絶縁層9の窓開けを行い、前記基板をエッチングし基板部材7に貫通孔3を形成する工程と、貫通孔3の内周面に絶縁層9を形成する工程と、貫通孔3における基板部材7の上面側の絶縁層9の窓開けを行う工程と、貫通孔3を充填すると共に、貫通孔3から所定距離離れた位置まで貫通配線基板の一方の面上に伸延した貫通伸延配線13を形成する工程と、貫通孔3の位置を除く貫通伸延配線13上に導電性を有するバンプ15を形成する工程とを備える。

(もっと読む)

Al合金膜を用いた低接触電気抵抗型電極およびその製造方法並びに表示装置

【課題】Al合金中の合金元素を少なくしても、透明酸化物導電膜との接触抵抗を低くすることのできる低接触電気抵抗型電極、およびこうした電極を製造するための有用な方法、並びにこうした電極を備えた表示装置を提供する。

【解決手段】本発明の低接触電気抵抗型電極は、酸化物透明導電膜と直接接触するAl合金薄膜からなる低接触電気抵抗型電極において、前記Al合金は、Alよりもイオン化傾向が小さい金属元素を0.1〜1.0原子%の割合で含有し、且つAl合金薄膜の酸化物透明電極と直接接触するAl合金薄膜表面は、最大高さ粗さRzで5nm以上の凹凸が形成されたものである。

(もっと読む)

181 - 200 / 317

[ Back to top ]