Fターム[5F033LL06]の内容

半導体集積回路装置の内部配線 (234,551) | 導電膜材料の特徴点 (1,721) | 結晶性 (266)

Fターム[5F033LL06]の下位に属するFターム

Fターム[5F033LL06]に分類される特許

21 - 40 / 109

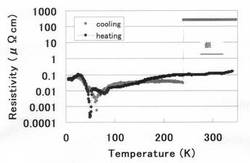

良伝導性非晶質合金、弱電用良伝導性非晶質合金および強電用良伝導性非晶質合金

【課題】単電子トンネリングを利用して、低温から室温まで動作可能な良伝導性非晶質合金、弱電用良伝導性非晶質合金および強電用良伝導性非晶質合金を提供する。

【解決手段】伝導島を有する孤立した複数の金属クラスターが、サブナノスケールの絶縁層を介して連続して連なった集積ナノ構造を有している。電子が、伝導島を介して、極低温から500℃の範囲で各金属クラスター間をトンネリングするよう構成されており、直流・交流のバリスティック伝導を示す。また、各金属クラスター間にサブナノスケールの原子空孔が均一に分布している。水素原子が各金属クラスター間に侵入固溶した、Ni-Nb-Zr系非晶質合金またはTi-Ni-Cu系非晶質合金から成っていてもよい。

(もっと読む)

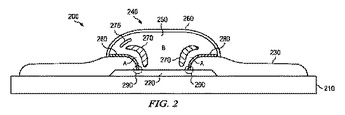

半導体デバイスにおける無電解ニッケルおよび金めっき

説明した例の半導体デバイスは、半導体基板及び金属コンタクトパッドの上に形成される不活性化層を含む。ENIG無電解めっきプロセスを用いて不活性化層及び金属コンタクトパッドの上にニッケルが、ニッケルの上に金が堆積される。ニッケルは、ニッケルの不活性化層とのインタフェースに及びニッケルの不活性化層及び金属コンタクトパッドとの接合に多孔質ニッケルのない第1非多孔質ニッケル領域(250A)を含み、第1ニッケル層の上の多孔質ニッケル領域(270)も含む。多孔質ニッケル層の上に金領域(260)がある。第2非多孔質ニッケル領域(250B)が多孔質ニッケル領域と金領域との間にあってもよい。金リッチ・ニッケル領域(275)が、多孔質ニッケル領域と金領域との間にあってもよい。堆積されるニッケル及び堆積される金の相対的厚さは、無電解金めっきプロセス中にニッケル層の腐食がデバイス層に達しないように選択される。

(もっと読む)

(もっと読む)

回路基板及び電子デバイス

【課題】導体の亀裂、基板のクラック、絶縁膜の破壊等を生じ難い高信頼度・高品質の回路基板及び電子デバイスを提供する。

【解決手段】基板1と、導体3とを含んでおり、導体3は、金属または合金でなり、基板1に設けられ、少なくとも基板1と対面する領域に、等軸晶31の領域を有する。この構造によれば、基板1と対面する領域で、導体3の等軸晶組織による等方性が得られるため、導体3の亀裂、絶縁膜の破壊及び基板1のクラックなどの発生が抑制される。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】酸化物半導体層を用いた、表示装置に代表される半導体装置において、画面サイズの大型化や高精細化に対応し、表示品質が良く、安定して動作する信頼性のよい半導体装置を提供することを課題の一つとする。

【解決手段】引き回し距離の長い配線にCuを含む導電層を用いることで、配線抵抗の増大を抑える。また、Cuを含む導電層を、TFTのチャネル領域が形成される酸化物半導体層と重ならないようにし、窒化珪素を含む絶縁層で包むことで、Cuの拡散を防ぐことができ、信頼性の良い半導体装置を作製することができる。特に、半導体装置の一態様である表示装置を大型化または高精細化しても、表示品質が良く、安定して動作させることができる。

(もっと読む)

Cu配線の形成方法

【課題】配線形成後に500℃以上の高温プロセスが存在する場合に適用可能なCu配線を形成すること。

【解決手段】500℃以上の温度の処理をともなう後工程が施されるCu配線の形成方法は、表面にトレンチおよび/またはホールを有する基板上の少なくともトレンチおよび/またはホールの底面と側面に、Cuの格子面間隔との差が10%以内の格子面間隔を有する金属からなる密着膜を形成する工程と、密着膜の上に前記トレンチおよび/またはホールを埋めるようにCu膜を形成する工程と、 Cu膜形成後の基板に350℃以上のアニール処理を行う工程と、Cu膜を研磨してCu膜のトレンチおよび/またはホールに対応する部分のみを残存させる工程と、研磨後のCu膜にキャップを形成してCu配線とする工程とを有する。

(もっと読む)

コンタクトプラグ、配線、半導体装置およびコンタクトプラグ形成方法

【課題】薄膜であっても銅(Cu)原子の金属シリサイド膜などへの拡散を充分に安定して抑止でき、尚且つ、小さな接触抵抗をもたらす比抵抗の小さな銅(Cu)からコンタクトプラグを形成できるようにする。

【解決手段】 本発明のコンタクトプラグ100は、半導体装置の絶縁膜104に設けられたコンタクトホール105に形成され、コンタクトホール105の底部に形成された金属シリサイド膜103と、コンタクトホール105内で金属シリサイド膜103上に形成された酸化マンガン膜106と、酸化マンガン膜106上に、コンタクトホール105を埋め込むように形成された銅プラグ層107と、を備え、酸化マンガン膜は非晶質からなる膜である、ことを特徴としている。

(もっと読む)

回路基板の製造方法

【課題】信頼性の高い回路基板を低コストで供給する。

【解決手段】開口部101を介してチップ取り出し電極2を含む基板1の一部表面が露出するようメタルマスク100を基板1に被せ、イオンプレーティング法により金属導体を形成した後、メタルマスク100を剥離することによって、基板1の一部表面に形成された金属導体からなる配線層21を形成する。これにより、フォトリソグラフィー法を用いることなく、基板上に配線層21を直接形成することができるため、生産性が高く低コストな回路基板を提供することが可能となる。

(もっと読む)

半導体装置及びその製造方法

【課題】信頼性の高い半導体基板上の回路基板を低コストで供給する。

【解決手段】開口部101を介してチップ取り出し電極2を含む半導体基板1の一部表面が露出するようメタルマスク100を半導体基板1に被せ、イオンプレーティング法により金属導体を形成した後、メタルマスク100を剥離することによって、半導体基板1の一部表面に形成された金属導体からなる配線層21を形成する。これにより、フォトリソグラフィー法を用いることなく、半導体基板上に配線層21を直接形成することができるため、生産性が高く低コストな回路基板を提供することが可能となる。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】配線間の寄生容量を十分に低減できる構成を備えた半導体装置を提供することを課題の一とする。

【解決手段】金属薄膜の一部または全部を酸化させた第1の層と酸化物半導体層の積層を用いるボトムゲート構造の薄膜トランジスタにおいて、ゲート電極層と重なる酸化物半導体層の一部上に接するチャネル保護層となる酸化物絶縁層を形成し、その絶縁層の形成時に酸化物半導体層の積層の周縁部(側面を含む)を覆う酸化物絶縁層を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、ウエハが反るのを防止できる半導体装置及びその製造方法を提供することを目的とする。

【解決手段】本発明に係る半導体装置は、互いに対向する第1及び第2の主面を有するGaAs基板と、前記GaAs基板の前記第1の主面上に形成され、Pd、Ta、Moの少なくとも1つから構成された第1の金属層と、前記第1の金属層上に形成され、Ni系合金又はNiから構成された第2の金属層と、を備えることを特徴とする。

(もっと読む)

半導体装置及びその製造方法

【課題】 半導体装置及びその製造方法に関し、バリアメタルの絶縁膜及びCuに対する密着性と、Cu拡散防止とを両立する。

【解決手段】 絶縁膜に設けた凹部の側壁にシール絶縁膜を形成し、シール絶縁膜の内側に順にシール絶縁膜との密着性が優れている第1の導電性バリア層、Cu拡散阻止能力が高い第2の導電性バリア層、及び、Cu系埋込電極との密着性が優れている第3の導電性バリア層の3層構造のバリア層を介してCu系埋込電極を設ける。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】LDMOSFETを有する半導体装置では、ソース電極が裏面にあることから、表面のソース・コンタクト領域と裏面のソース電極間の電気抵抗を低減するため、上面からP型エピタキシャル層を貫通してP+型基板内に伸びるボロンを高濃度にドープしたポリ・シリコン埋め込みプラグが設けられている。このポリ・シリコン埋め込みプラグの周辺のシリコン単結晶領域に転位が発生しており、これにより、リーク不良が誘発されていることが明らかとなった。

【解決手段】本願発明は、相互に不純物濃度の異なる第1及び第2の半導体層の境界面を貫通するシリコン系プラグを有する半導体装置であって、このプラグの少なくとも内部は多結晶領域であり、この多結晶領域表面の内、先の境界面の両側近傍は、固相エピタキシャル領域で覆われている。

(もっと読む)

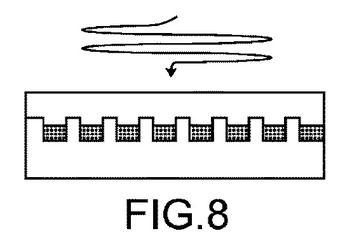

金属結晶領域、特に集積回路における金属結晶領域を生成する方法

本方法は、例えば相互接続ラインを形成するために、薄い結晶(8)のシートを、基板(1)のトレンチに堆積される、このシートと同一のタイプであるが、アモルファスであるか小さな粒径である金属(6)に固定することを含む。焼鈍しは、このラインにシートの結晶構造を徐々に与える。結晶(8)が除去されると、高度の導電結晶ラインが得られる。それは、その粒径が非常に拡大されているからである。金属は、銅、銀及びアルミニウムから選択される。  (もっと読む)

(もっと読む)

アモルファスなタンタル−イリジウム拡散バリアを用いた銅相互接続構造、その形成方法、および該方法による半導体デバイス製造方法

【課題】ライナ/銅界面のボイド生成部位の排除により、高い信頼性および生産歩留まりが得られる半導体デバイス製造方法を提供する。

【解決手段】半導体デバイス製造に用いる拡散バリアを形成する方法は、物理蒸着(PVD)工程によって、パターン形成された中間誘電体(ILD)層の上に、イリジウム・ドープされたタンタル・ベースのバリア層を堆積するステップを含み、該バリア層は、原子量で少なくとも60%のイリジウム濃度で、バリア層が結果としてアモルファス構造を有するように堆積される。

(もっと読む)

W含有膜の製造方法および電気光学装置の製造方法

【課題】WSi膜上にSiO2膜を形成し、SiO2膜を緻密化するため成膜温度より高い温度でアニールを行った場合、SiO2膜中にクラックが入る欠陥が生じる場合がある。このクラックの発生を抑えるために、アニール時の温度変化速度を抑え、急激な熱膨張/熱収縮を避けているが、クラック欠陥を十分抑えられないという課題がある。

【解決手段】WSi膜を用いた、走査線前駆体11cをスパッタリングにより200nmの膜厚に堆積させる。そして、無機絶縁膜100としてSiO2膜を堆積する。そして、約700℃で熱処理を行う。そして、無機絶縁膜100を除去する。走査線前駆体11cの改質に伴い、無機絶縁膜100との間には応力が掛かっている。ここで、無機絶縁膜100を除去することで、走査線前駆体11cの改質に伴う応力を開放することが可能となり、クラック欠陥の発生を抑えることが可能となる。

(もっと読む)

半導体装置の製造方法及び半導体装置

【目的】配線抵抗の上昇を抑制したまま、EM特性を改善させる半導体装置或いはその製造方法を提供することを目的とする。

【構成】本発明の一態様の半導体装置の製造方法は、基体上に絶縁膜を形成する工程(S104)と、絶縁膜に開口部を形成する工程(S106)と、開口部内に、ケイ化物の形成エネルギーがCuケイ化物の形成エネルギーよりも小さい金属含有膜を形成する工程(S108)と、前記金属含有膜が形成された開口部内に銅(Cu)膜を埋め込む工程(S112)と、Cu膜上に、300℃未満の温度でCuとSiとを含有する化合物膜を選択的に形成する工程(S120)と、を備えたことを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】銅層形成の下地となるシード層のオーバーハングが抑制された半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、半導体基板の上方に、絶縁膜を形成する工程と、絶縁膜に凹部を形成する工程と、凹部の内面に、バリアメタル層を形成する工程と、バリアメタル層上に、RuとCuを含むシード層を形成する工程と、シード層上に銅層を形成する工程とを有する。

(もっと読む)

半導体装置及びその製造方法、並びに表示装置

【課題】高融点バリアメタル層を形成すること無く、Si膜又はSiを主成分とする膜と良好なコンタクト特性を実現するAl合金膜を提供する。

【解決手段】半導体デバイス(TFT)は、チャネル部11を形成する様にSi半導体膜7上に配設された被酸化のオーミック低抵抗Si膜8と、オーミック低抵抗Si膜8と直接に接続し、且つ、接続界面近傍に、少なくともNi原子、N原子及びO原子を含むアルミニウム合金膜から成る、ソース電極9及びドレイン電極10とを有する。

(もっと読む)

半導体装置の製造方法

【課題】例えばエアギャップ構造の形成に好適な、半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、半導体基板上方に第1の絶縁膜を形成する工程と、第1の絶縁膜に溝を形成する工程と、第1の絶縁膜上面及び溝の内面を覆うように、Ruを含む第1の金属層を形成する工程と、第1の金属層上に、銅を含む第2の金属層を形成する工程と、第1の絶縁膜上の第2の金属層及び第1の金属層を研磨し除去して、第1の絶縁膜を露出させ、溝内に形成された第1の金属層及び第2の金属層を残す工程と、研磨によって露出した第1の絶縁膜を上面から少なくとも一部除去する工程と、第1の絶縁膜の上方に、第1及び第2の金属層の少なくとも上面を覆う第2の絶縁膜を形成する工程とを有する。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体装置において、微細パターンへのCuの埋め込みを良好にし、且つCuの層間絶縁膜中への拡散を抑制する。

【解決手段】半導体装置は、半導体基板上の層間絶縁膜101に形成されたトレンチ102と、トレンチ102の底部及び側壁を覆うように形成され、白金族元素、高融点金属及び窒素を含有する導電体からなる第1のバリアメタル膜103と、トレンチ102において、第1のバリアメタル膜103上に形成された金属膜105とを備える。

(もっと読む)

21 - 40 / 109

[ Back to top ]