Fターム[5F033LL06]の内容

半導体集積回路装置の内部配線 (234,551) | 導電膜材料の特徴点 (1,721) | 結晶性 (266)

Fターム[5F033LL06]の下位に属するFターム

Fターム[5F033LL06]に分類される特許

61 - 80 / 109

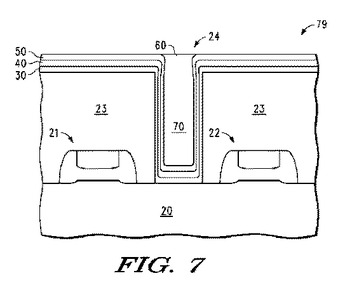

ボイドの無いコンタクトプラグ

コンタクトプラグを形成する半導体素子形成プロセスでは、チタンまたはタンタルコンタクト層(30)、窒化チタンバリア層(40)、及びタングステンシード層をコンタクト開口部(24)に順番に堆積させる。次に、コンタクトホール(24)への充填を、コンタクト開口部の底面から上に向かって、銅層(60)を電気メッキすることにより行なって、ボイドがコンタクト開口部(24)内に形成されることがないようにする。全ての余分な材料をCMPプロセスにより除去してコンタクトプラグ(70)を形成し、この場合、CMPプロセスを使用して、コンタクト層/シード層/バリア層(30,40,50)のうちの一つ以上の層を薄くする、または除去することもできる。  (もっと読む)

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】信頼性及び生産性が高い装置として得られる半導体装置及び生産性の高い半導体装置の製造方法を提供する。

【解決手段】半導体基板0上に形成された層間絶縁膜10に設けられ、表面にバリアメタル層2が形成された溝にCu配線100が形成されてなる。これらの層により前記リード表面を被膜している。前記Cu配線100は、Ag、As、Bi、P、Sb、Si、Tiのうち少なくとも1つを0.1重量%以上、Cuに対する最大固溶限未満の範囲で含有するCu合金1で構成されている。

(もっと読む)

半導体装置およびその作製方法

【課題】無線信号から生成できる電流値及び電圧値の範囲内で駆動できるメモリを搭載した半導体装置を提供することを課題とする。また、半導体装置製造後にデータの書き込みを行える追記型のメモリを提供することも課題とする。

【解決手段】絶縁表面を有する基板上にアンテナと、アンチヒューズ型のROMと、駆動回路とを形成する。アンチヒューズ型のROMを構成する一対の電極の間に、シリコン膜とゲルマニウム膜との積層を設ける。この積層を有するアンチヒューズ型のROMは、書き込み電圧のバラツキを低減することができる。

(もっと読む)

電気光学装置とその製造方法および電子機器

【課題】エッチング液の浸透による反射電極の侵食を回避でき、反射電極を透明導電層の縁まで拡大することができ、かつ生産性を向上することができる電気光学装置とその製造方法および電子機器を提供する。

【解決手段】基板上に絶縁層14を形成する工程と、絶縁層14上の一部に金属からなる反射電極2を形成する工程と、反射電極2上を含む絶縁層14上を覆うように非晶質透明導電層を形成する工程と、反射電極2を加熱し、反射電極2上の非晶質透明導電層を選択的に結晶化して結晶化透明導電層3pを形成する工程と、反射電極2上の結晶化透明導電層3pを透明電極3として残しつつ絶縁層14上の非晶質透明導電層をエッチングによって選択的に除去する工程と、を有する。

(もっと読む)

絶縁膜積層体、絶縁膜積層体の製造方法、半導体装置及び半導体装置の製造方法

【課題】ボロン漏れの抑制とリーク電流増加の抑制とを同時に実現可能な、絶縁膜及びこの絶縁膜を備えた半導体装置と、絶縁膜の製造方法及び半導体装置の製造方法を提供する。

【解決手段】微結晶組織からなるハフニウム含有窒化シリコン酸化物層3aと、非晶質組織からなるハフニウム含有窒化シリコン酸化物層3bとが半導体基板2上に積層されてなる積層膜からなり、積層膜の窒素濃度が15原子%以上40原子%以下の範囲であることを特徴とする半導体装置用の絶縁膜積層体3を採用する。

(もっと読む)

半導体装置の製造方法

【課題】強誘電体キャパシタが備えるキャパシタ誘電体膜の特性を向上させることが可能な半導体装置の製造方法を提供すること。

【解決手段】第1導電膜の上に、ゾル・ゲル法により強誘電体膜24を形成する工程と、強誘電体膜24上に第1導電性酸化金属膜25dを形成する工程と、第1導電性金属酸化膜25dに対して第1のアニールを行う工程と、第1導電性酸化金属膜25d上に第2導電性酸化金属膜25eを形成する工程と、第1導電膜23、強誘電体膜24、及び第2導電膜25をパターニングしてキャパシタを形成する工程とを有し、第1導電性酸化金属膜25dを形成する工程において、スパッタガスにおける酸素流量比が増大することにより強誘電体膜24の強誘電体特性が向上することを利用し、強誘電体特性を酸素流量比で調節する半導体装置の製造方法による。

(もっと読む)

半導体装置とその製造方法

【課題】強誘電体キャパシタが備えるキャパシタ誘電体膜の特性を向上させることが可能な半導体装置とその製造方法を提供すること。

【解決手段】第1導電膜23の上に、少なくともゾル・ゲル法による成膜ステップを含む成膜方法により第1強誘電体膜24bを形成する工程と、第1強誘電体膜24bの上に、スパッタ法により第2強誘電体膜24cを形成する工程と、第2強誘電体膜24cの上に第2導電膜25を形成する工程と、第1導電膜23、第1、第2強誘電体膜24b、24c、及び第2導電膜25をパターニングして、下部電極23a、キャパシタ誘電体膜24a、及び上部電極25aを備えたキャパシタQを形成する工程とを有する半導体装置の製造方法による。

(もっと読む)

半導体装置およびその製造方法

【課題】ダマシン構造の多層配線およびCoWP等の導電性バリア膜を有する半導体装置において、従来よりも電気特性に優れた半導体装置およびその製造方法を提供する。

【解決手段】下層配線12に至るビア孔17を開口する際、下層配線12表面に残存する導電性バリア膜13と下層配線12との間で形成される反応層14が除去される。よって、ビア17下面と下層配線12とが接合する界面において、導電性バリア膜13と下層配線12との間で形成される反応層14が存在しないため、ビア抵抗を十分に下げることができる。

(もっと読む)

低抵抗コンタクト構造体及びその製造方法

【課題】 半導体デバイスと後工程の相互接続体との間の誘電体材料層内にコンタクト構造体を製造する方法を提供すること。

【解決手段】 本発明の実施形態は、半導体デバイスと後工程の相互接続体との間の誘電体材料層内にコンタクト構造体を製造する方法を提供する。この方法は、誘電体材料層内に少なくとも1つのコンタクト開口部を作成するステップと、化学気相堆積プロセスによって第1のTiN膜を形成するステップであって、第1のTiN膜はコンタクト開口部をライニングする(内側を覆う)ステップと、物理的気相堆積プロセスによって第2のTiN膜を形成するステップであって、第2のTiN膜は第1のTiN膜をライニングするステップとを含む。本発明の実施形態によって製造されるコンタクト構造体も提供される。

(もっと読む)

半導体装置の製造方法

【課題】配線溝および接続孔の内部に、良好な埋め込み形状を有するCu膜を電解めっきにより形成する。

【解決手段】半導体装置の製造方法であって、半導体基板上に絶縁膜11を形成する工程と、絶縁膜11に配線溝および接続孔の少なくとも一方の被埋め込み領域12を形成する工程と、被埋め込み領域12上に、導電性を有し、かつ被埋め込み領域12の内部を埋め込まない厚さの非晶質膜15を形成する工程と、非晶質膜15上に被埋め込み領域12の内部を埋め込む厚さの導電膜16をめっきにより形成する工程と、を有する。

(もっと読む)

半導体素子及びその製造方法

【課題】本発明は、半導体素子の層間接続のための金属の拡散を効率よく防止できる半導体素子及びその製造方法を提供する。

【解決手段】本発明は、半導体基板1;前記半導体基板1上にダマシンパターンが形成された層間絶縁膜2、3;前記ダマシンパターン内に形成され、三元系物質であるCoFeBからなる拡散防止膜4;前記拡散防止膜上に形成されるシード膜5;及び、前記シード膜上に充填される銅配線7を含む。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】膜厚の縮小とキャパシタ容量の増加を実現すると共に、界面反応を抑制してMIMキャパシタの信頼性を向上することを目的とする。

【解決手段】MIMキャパシタ11の少なくとも下部電極をスタッフト結晶構造を有する導電性金属窒化膜6から形成することにより、膜厚の縮小とキャパシタ容量の増加を実現すると共に、界面反応が抑制してMIMキャパシタの信頼性を向上することができる。

(もっと読む)

半導体素子のビットライン形成方法

【課題】ビットラインの抵抗を減らすための半導体素子のビットライン形成方法を提供する。

【解決手段】半導体素子のビットライン形成方法に関するものであり、所定の構造物が形成された半導体基板上にバリア金属膜を形成する段階と、バリア金属膜上に非晶質チタンカーボンニトリド膜を形成する段階と、ボロンガスが含まれた雰囲気で非晶質チタンカーボンニトリド膜上にタングステンシード層を形成する段階と、タングステンシード層上にタングステン膜を形成してビットラインを形成する段階を含む。

(もっと読む)

半導体装置及びその製造方法

【課題】プラグを介した導電接続構造を具備した半導体装置におけるデバイス構成層の結晶配向性を向上させた半導体装置を提供する。

【解決手段】本発明の半導体装置は、基板10上の層間絶縁膜26に形成された貫通孔24内に設けられてなるプラグ20を介した導電接続構造を具備した半導体装置であり、前記プラグ20が、前記貫通孔24内に埋め込まれたプラグ導電層22と、該プラグ導電層22上に埋め込まれた第2導電膜21と、前記第2導電膜21の表面部21aに形成されたアモルファス層とを有しており、前記プラグ20表面のアモルファス層上に窒化チタン層12が形成されている構成である。

(もっと読む)

半導体装置及びその製造方法

【課題】プラグを介した導電接続構造を具備した半導体装置におけるデバイス構成層の結晶配向性を向上させた半導体装置を提供する。

【解決手段】本発明の半導体装置100は、基板10上の層間絶縁膜26に形成された貫通孔24内に設けられてなるプラグ20を介した導電接続構造を具備した半導体装置であり、前記プラグ20は、前記貫通孔24内に第1導電膜を埋め込んでなるプラグ導電層22を有しており、少なくとも前記プラグ導電層22上には、シリコンを含む導電材料からなる第2導電膜21が形成されており、前記第2導電膜21上には、自己配向性を有する導電材料からなる窒化チタン層12(第3導電膜)が形成されている。

(もっと読む)

金属配線形成方法及びアクティブマトリクス基板の製造方法

【課題】下地層に対する導電層の密着性を向上させる。

【解決手段】基板P上に下地層F1を形成する工程と、金属微粒子及び分散安定剤を含む溶液を下地層F1上に塗布する工程と、塗布した溶液を加熱処理して導電層F2を形成する工程とを有する。塗布した溶液中の下地層F1との界面近傍における分散安定剤の量に基づいて、加熱処理を開始するまでの時間を設定する。

(もっと読む)

強誘電体メモリおよびその製造方法

【課題】強誘電体層の結晶配向性が良好に制御された強誘電体メモリおよびその製造方法を提供する。

【解決手段】本発明にかかる強誘電体メモリ100の製造方法は、基体の上方にチタンを構成元素として含む第1の金属層を形成する工程と、第1の金属層を窒化して窒素化合物からなる第1の配向制御層12を形成する工程と、第1の配向制御層の上方にチタンを構成元素として含む第2の金属層を形成する工程と、第2の金属層を窒化して窒素化合物からなる第2の配向制御層112を形成する工程と、第2の配向制御層の上方に第1電極32を形成する工程と、第1電極の上方に強誘電体層34を形成する工程と、強誘電体層の上方に第2電極36を形成する工程と、を含む。

(もっと読む)

強誘電体メモリおよびその製造方法

【課題】強誘電体層の結晶配向性が良好に制御された強誘電体メモリおよびその製造方法を提供する。

【解決手段】

本発明にかかる強誘電体メモリ100の製造方法は、絶縁層26を形成する工程と、前記絶縁層を貫通するコンタクトホール22を設ける工程と、コンタクトホールの側面および底面と、絶縁層の上方に配向制御層12を形成する工程と、配向制御層の上方に導電層20aを成膜する工程と、絶縁層の上方において配向制御層が露出するように、導電層を研磨する工程と、配向制御層の上方に第1電極32を形成する工程と、第1電極の上方に強誘電体層34を形成する工程と、強誘電体層の上方に第2電極36を形成する工程と、を含む。

(もっと読む)

シリコン−ゲルマニウム立体構造CMOS上の局所配線の製造方法

【課題】シリコン−ゲルマニウム立体構造CMOSにおいて、シリコンCMOS素子とゲルマニウムCMOS素子との間の局所配線を容易に形成する。

【解決手段】シリコンCMOS素子を有するシリコン基板を準備し(12)、該素子の上部に絶縁層を形成する(14)。上記絶縁層を部分的に開口し(16)、その上にゲルマニウム薄膜を形成する(18)。アニール処理により、上記薄膜のゲルマニウムを流動化する(24)。これにより、開口部に上記ゲルマニウムが流れ込み、該ゲルマニウムと上記シリコン基板および上記シリコンCMOS素子との間に接点が形成される。さらに冷却することで、上記ゲルマニウムがLPE成長により結晶化される(26)。そして、単結晶のゲルマニウム上にゲルマニウムCMOS素子を形成する。

(もっと読む)

強誘電体メモリおよびその製造方法

【課題】強誘電体層の結晶配向性が良好に制御された強誘電体メモリおよびその製造方法を提供する。

【解決手段】本発明にかかる強誘電体メモリ100の製造方法は、(a)導電層20を形成する工程と、(b)導電層の表面をアモルファス化してアモルファス層を形成する工程と、(c)導電層の上方に配向制御層12を形成する工程と、(d)配向制御層の上方に第1電極32を形成する工程と、(e)第1電極の上方に強誘電体層34を形成する工程と、(f)前記強誘電体層の上方に第2電極36を形成する工程とを含む。

(もっと読む)

61 - 80 / 109

[ Back to top ]