Fターム[5F033LL06]の内容

半導体集積回路装置の内部配線 (234,551) | 導電膜材料の特徴点 (1,721) | 結晶性 (266)

Fターム[5F033LL06]の下位に属するFターム

Fターム[5F033LL06]に分類される特許

41 - 60 / 109

半導体装置及びその製造方法

【課題】エレクトロマイグレーションの抑制が図られた半導体装置を提供する。

【解決手段】半導体装置は、半導体素子の形成された半導体基板と、半導体基板の上方に、水分を含み、凹部が形成された層間絶縁膜と、凹部の内面上に形成され、非晶質及び多結晶の一方の結晶性を有する第1のバリアメタル層と、第1のバリアメタル層上に形成され、非晶質及び多結晶の他方の結晶性を有する第2のバリアメタル層と、第2のバリアメタル層上に形成された銅配線と、銅配線を覆って前記層間絶縁膜上に形成された銅拡散防止絶縁膜と、銅配線と銅拡散防止絶縁膜との界面に形成された金属酸化物層とを有する。

(もっと読む)

表示装置

【課題】表示パネルに設けられるパッド部として適した構造を提供することを目的の一とする。酸化物半導体の他、絶縁膜及び導電膜を積層して作製される各種用途の表示装置において、薄膜の剥がれに起因する不良を防止することを目的の一とする。

【解決手段】走査線と信号線が交差し、マトリクス状に配列する画素電極層と、該画素電極層に対応して設けられた画素部を有し、該画素部に酸素の含有量が異なる少なくとも二種類の酸化物半導体層とを組み合わせて構成され、ゲート電極層と重なるチャネル形成領域となる半導体層上にチャネル保護層が設けられた逆スタガ型薄膜トランジスタが設けられた表示装置である。この表示装置において画素部の外側領域には、走査線、信号線を構成する同じ材質の導電層によって、画素電極層と対向する共通電極層と電気的に接続するパッド部が設けられている。

(もっと読む)

不揮発性記憶装置及びその製造方法

【課題】多数の積層膜を有する構造においても基板の反りが小さい不揮発性記憶装置及びその製造方法を提供する。

【解決手段】基板と、前記基板の上に交互に積層され、積層方向に貫通する貫通孔が形成されたそれぞれ複数の絶縁膜及び電極膜と、前記貫通孔の内部に形成された半導体ピラーと、少なくとも前記半導体ピラーと前記電極膜との間に設けられた電荷蓄積層と、を備え、前記絶縁膜は、圧縮応力及び引張応力のいずれか一方を発現する膜を含み、前記電極膜は、前記圧縮応力及び引張応力のいずれか他方を発現する膜を含むことを特徴とする不揮発性記憶装置が提供される。

(もっと読む)

半導体装置の製造方法

【課題】信頼性の高い半導体装置を効率良く製造できるようにする。

【解決手段】シリコン基板1上に強誘電体キャパシタ37を形成する際、下部電極膜25の上に、アモルファス又は微結晶の酸化導電膜26を形成する。酸化導電膜26を熱処理により結晶化した後、強誘電体膜27の初期層27Aの形成時に酸化導電膜26を還元することにより、結晶粒が小さく且つ配向が整った第2の導電膜26Aを形成する。強誘電体膜27は、MOCVD法により形成し、その初期層27Aは第2の導電膜26Aの結晶配向に倣って成長する。これにより、強誘電体膜27の表面モフォロジが良好になる。

(もっと読む)

薄膜トランジスタ基板とその製造方法

【課題】工程効率が向上し、かつ、信頼性が向上した酸化物半導体薄膜トランジスタ基板とその製造方法を提供する。

【解決手段】酸化物半導体薄膜トランジスタは、絶縁基板上に形成され、ゲート電極を含むゲート線と、ゲート線と交差しドレイン電極接続部を含むデータ線と、ゲート電極の周辺に形成される酸化物半導体活性層パターンと、データ線と酸化物半導体活性層パターンの上に形成されドレイン電極接続部を露出する第1開口部、及び酸化物半導体活性層パターンを露出する第2開口部を有するパシベーション層と、第1開口部及び第2開口部によって酸化物半導体活性層パターンとドレイン電極接続部とを電気的に接続するドレイン電極とを含む。

(もっと読む)

半導体装置、及び薄膜キャパシタの製造方法

【課題】 下部電極となるTiN膜の表面のラフネスを低減させるために、化学機械研磨、Arによるスパッタリング、Ta膜の堆積等の工程が必要になる。

【解決手段】 半導体基板(10)の上に薄膜キャパシタが配置されている。この薄膜キャパシタは、少なくとも表層部が非晶質または微結晶の金属で形成された下部電極(21a,22a)、該下部電極の上に配置された誘電体膜(23a)、及び該誘電体膜の上に配置された上部電極(24a)を含む。

(もっと読む)

半導体装置の製造方法

【課題】MISトランジスタを備える半導体装置の性能を向上させる。

【解決手段】シリコン基板1の主面s1上のうち、nMIS領域RnにnMIS用ゲート電極GEnを形成し、pMIS領域RpにpMIS用ゲート電極GEpを形成し、それらの側方下部に、それぞれ、n型ソース・ドレイン領域sdnおよびp型ソース・ドレイン領域sdpを形成する。続いて、シリコン基板1の主面s1と両ゲート電極GEn,GEpとを覆うようにして、引張応力を持つ第1応力膜N1aを形成する。その後、pMIS領域Rpの第1応力膜N1aにイオン注入300を施すことで応力を緩和させる。その後、熱処理を施すことで両ゲート電極GEn,GEpを結晶化してから、第1応力膜N1aを除去する。両ゲート電極GEn,GEpを結晶化する工程では、第1応力膜N1aの引張応力をnMIS用ゲート電極GEnに記憶させる。

(もっと読む)

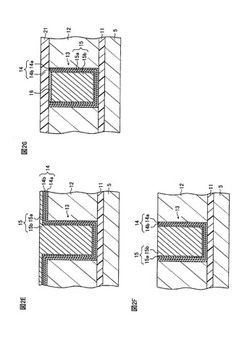

半導体装置及び半導体装置の製造方法

【目的】コンタクトプラグ材料の基板への拡散を抑制する半導体装置及び半導体装置の製造方法を提供することを目的とする。

【構成】本発明の一態様の半導体装置は、半導体基板200と導通するコンタクトプラグとなるCu膜260と、Cu膜260の少なくとも底面側に、半導体基板200と接触して配置された柱状結晶構造をもつTiN膜242と、Cu膜260の少なくとも底面側に、TiN膜242と接触して配置された、TiNのアモルファス膜244と、Cu膜260の底面側と側面側に、少なくとも一部がアモルファス膜244とCu膜260とに接触して配置された、TiN膜242材と同じ材料で柱状結晶構造をもつTiN膜246と、Cu膜260の側面側に配置されたSiO2膜220と、を備えたことを特徴とする。

(もっと読む)

配線形成方法

【課題】 成膜時間や工数を大幅に削減することができ、生産性良く配線を形成することできるとともに、結晶性の良い無電解めっき膜の形成が可能で、配線の主体となる無電解めっき膜の形状も安定なものとすることが可能な配線形成方法を提供する。

【解決手段】 銅とマンガンを含む合金膜を形成する工程と、合金膜を熱処理してマンガンを表面及び下側界面に偏析させ、銅薄膜の上下にマンガン層が形成された複合膜とする工程と、銅薄膜上に形成されたマンガン層を除去する工程と、銅薄膜をシード層として無電解めっきを行う工程とを有する。無電解めっきを行う工程においては、レジストを用いたリフトオフ法により配線パターンを決定する。無電解めっき工程の後、レジストを除去し、露呈する銅薄膜及びマンガン層の不要部分を除去する。

(もっと読む)

三次元構造体の製造方法および三次元構造体

【課題】導電体内の欠陥の発生を抑制し、導電体が連続的に形成される三次元構造体の製造方法および三次元構造体を提供する。

【解決手段】第1の導電体上に、絶縁体と、この絶縁体内に、第1の導電体と異なる第2の導電体で構成される縦構造体と横構造体が組み合わされた三次元の擬似導電体構造とを形成する工程と、擬似導電体構造を溶解除去して三次元の空洞を形成し、第1の導電体を露出させる工程と、第1の導電体をシード層として、電解めっき法により第3の導電体を空洞に充填し、三次元の導電体構造を形成する工程を有することを特徴とする三次元構造体の製造方法およびこれによる三次元構造体。

(もっと読む)

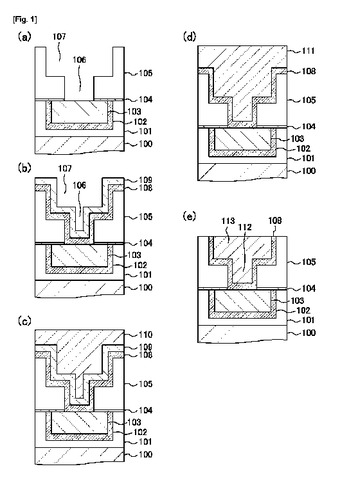

半導体装置および半導体装置の製造方法

【課題】微細パターンのCuの埋め込みが良好であり、Cuの層間絶縁膜中への拡散を抑制することを目的とする。

【解決手段】半導体装置では、下層配線102が半導体基板上の絶縁膜101内に形成され、上層配線112が絶縁膜101の上の層間絶縁膜104内に形成され、下層配線102と上層配線112とは層間絶縁膜104内に形成されたビアプラグ111を介して接続されている。ビアプラグ111および上層配線112では、それぞれ、第1および第2のバリアメタル膜107,108とCu膜110とが順に積層されており、第1のバリアメタル膜107は窒素を含有し、第2のバリアメタル膜108は白金族元素を含有している。

(もっと読む)

半導体装置及びその製造方法

【課題】金属ナノ微粒子を用いた、電極、配線形成方法では、金属ナノ微粒子溶液を塗布、印刷後抵抗値を落とすために200℃程度の熱処理が必要である。プラスチックなどのフレキシブル基板では、耐熱性が150℃程度であるため、この熱処理により基板の変形が出てしまう。

【解決手段】本発明は、ハロゲンを有するガスに金属ナノ微粒子を所望の形状に印刷した後に暴露する事によって、なんら過熱焼成することなく、金属電極、配線を形成できる。

(もっと読む)

半導体装置およびその製造方法

【課題】層間絶縁膜の損傷を抑えながらタンタルを主成分とするバリア膜をスパッタによって成膜する半導体装置の製造方法を提供する。

【解決手段】層間絶縁膜113上に、キセノンガスを用いたスパッタリングで、タンタルまたは窒化タンタルを主成分とするバリア膜116を形成するスパッタ成膜工程を備える。スパッタ成膜工程は、層間絶縁膜113の上に、基板にRFバイアスを印加して行うキセノンガスを用いるスパッタリングにより、窒化タンタルを主成分とするバリア膜116Aを形成する工程と、RFバイアスを印加せずに行うキセノンガスを用いるスパッタリングにより、バリア膜116Aの上に、タンタルを主成分とするバリア膜116Bを形成する工程とを備えてもよい。バリア膜116はRFバイアスを連続的に変化させて、層間絶縁膜113側をRFバイアスを印加して、配線層117側をRFバイアスを印加せずに形成することもできる。

(もっと読む)

半導体装置及びその製造方法

【課題】信頼性の高い半導体装置を提供する。

【解決手段】半導体基板101と、前記半導体基板の上方に設けられた、誘電体膜116を下部電極115と上部電極117とで挟んでなるキャパシタと、を備え、前記下部電極は、貴金属膜115aと、前記貴金属膜上に島状に複数形成された導電性酸化物膜115bと、を有する。

(もっと読む)

半導体装置及びその製造方法

【課題】ビア抵抗の上昇を抑制できる構造を有する半導体装置を提供する。

【解決手段】半導体装置は、半導体基板100上のビアホール105bを有する絶縁膜105と、ビアホール105bの底部及び壁部に沿うように形成されたIVa族、Va族又はVIa族元素の金属窒化膜106と、金属窒化膜106の上に、ビアホール105bの底部及び壁部に沿うように形成されたTa膜107と、Ta膜107の上に、ビアホール105bを充填するように形成された導電膜よりなるビア109bとを備える。ビアホール105bの底部における金属窒化膜106の膜厚は、4nm以上であって且つ8nm未満である。

(もっと読む)

半導体装置及びその製造方法

半導体装置は、半導体基板上に形成された絶縁膜と、絶縁膜中に形成され、銅又は銅合金からなる埋め込み配線とを備え、絶縁膜と埋め込み配線との間に、白金族元素、又は白金族元素の合金からなるバリアメタル層を有しており、バリアメタル層は、相対的にバリア性が高くなる非晶質度を有する非晶質構造を一部に含んでいる。  (もっと読む)

(もっと読む)

半導体装置およびその製造方法

【課題】寄生容量が低く、かつ、熱処理による抵抗値の変動が小さい抵抗素子を有する半導体装置を得ることのできる技術を提供する。

【解決手段】スパッタリングターゲット材料としてタンタルを用い、スパッタリングガスとしてアルゴンと窒素との混合ガスを用いた反応性直流スパッタリング法により、窒化タンタル膜からなる厚さ20nm、窒素濃度30原子%未満の第1抵抗層5a、及び窒化タンタル膜からなる厚さ5nm、窒素濃度30原子%以上の第2抵抗層5bを順次形成した後、第1及び第2抵抗層5a,5bを加工して抵抗素子R1を形成する。窒素濃度が30原子%以上の上部領域を設けることにより、配線工程において熱負荷が与えられても抵抗素子R1の抵抗変動率を1%未満に抑えることができる。

(もっと読む)

半導体装置及びその製造方法

【課題】nチャネル型電界効果トランジスタとpチャネル型電界効果トランジスタを有する半導体装置において、nチャネル型電界効果トランジスタ、pチャネル型電界効果トランジスタ共にドレイン電流特性に優れた半導体装置を実現する。

【解決手段】nチャネル型電界効果トランジスタ10と、pチャネル型電界効果トランジスタ30とを有する半導体装置において、nチャネル型電界効果トランジスタ10のゲート電極15を覆う応力制御膜19には、膜応力が引張応力側の膜を用いる。pチャネル型電界効果トランジスタ30のゲート電極35を覆う応力制御膜39には、膜応力が、nチャネル型トランジスタ10の応力制御膜19より、圧縮応力側の膜を用いることにより、nチャネル型、pチャネル型トランジスタの両方のドレイン電流の向上が期待できる。このため、全体としての特性を向上させることができる。

(もっと読む)

半導体装置の製造方法

【課題】反射防止膜としてTiN膜を用いる場合において、アッシング工程にてTiN膜がAl合金配線から剥離するのを抑制できるようにする。

【解決手段】シリコン基板上に形成されるAl合金配線層の反射防止膜としてのTiN膜13f、16fの結晶粒界に充填物質13g、16gを充填する。このようにすれば、Al−Cu膜13c、16cへの酸素(O2)ラジカルの進入を防ぐことが可能となる。従って、酸素(O2)ラジカルとAl−Cu膜13cとが反応してAlxOyが形成されることが防止され、ポリマー除去時にAlxOyがフッ素ラジカルによって還元され、反射防止膜13f、16fがAl−Cu膜13cから剥離することもない。

(もっと読む)

半導体装置及びその製造方法

【課題】従来の半導体装置では、配線層間に形成される酸化膜により、配線層間の接続抵抗値が低減され難いという問題があった。

【解決手段】本発明の半導体装置では、第1の配線層3と第2の配線層とを接続する開口領域8〜12を埋設する第1の金属層14〜18上のスピンコート樹脂膜21に開口部22が形成されている。開口部22内では、メッキ用金属層23を構成するCr層とCuメッキ層24とが接続している。この構造により、第1の金属層14〜18上のCr層は、結晶粒子間が広くなり、粗な領域となる。そして、Cr層の粗な領域には、第2の金属層19とCuメッキ層24との合金層が形成され、接続抵抗値が低減される。

(もっと読む)

41 - 60 / 109

[ Back to top ]