Fターム[5F033MM21]の内容

半導体集積回路装置の内部配線 (234,551) | 配線構造、形状の特徴点 (15,803) | 配線の平面形状 (698)

Fターム[5F033MM21]の下位に属するFターム

スリットを有するもの (119)

凹凸を有するもの (91)

Fターム[5F033MM21]に分類される特許

41 - 60 / 488

半導体装置の製造方法及び半導体装置

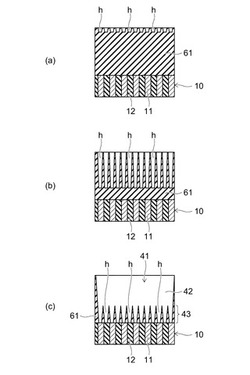

【課題】実施形態によれば、ホールの深さのばらつきを防ぐ半導体装置の製造方法及び半導体装置を提供する。

【解決手段】実施形態によれば、半導体装置の製造方法は、複数の第1の開口と第1の開口よりも密に並んだ複数の第2の開口とを有するマスクを用いて層間絶縁層61をドライエッチングし、第1の開口の下で下地層10に達する第1のホールと、第2の開口の下で下地層10に達する第2のホール41とを同時に形成する工程を備えている。第1のホールは他の第1のホールとは接することなく下地層10に達する。ドライエッチングの開始後、複数の第2の開口のそれぞれの下に複数のホールhが形成され、ドライエッチングの進行に伴って、複数のホールhは少なくとも開口端を含む上部42で互いにつながる。

(もっと読む)

半導体集積回路及び半導体集積回路の設計方法

【課題】電位ドロップに起因するセルの動作不良を防止すること。

【解決手段】本発明に係る半導体集積回路は、チップ1上に配置された電源パッド2aと、電源配線構造10を介して電源パッド2aに接続された回路群21,22とを備える。その電源配線構造10は、異なる配線層に形成され複数の交差点IS1,IS2においてオーバーラップする複数の第1電源配線11及び複数の第2電源配線12と、それら複数の第1電源配線11と複数の第2電源配線12を接続するビア13とを有する。上記回路群は、第1領域R1に配置された機能ブロック21を含む。ビア13は、第1領域R1と電源パッド2aの間の第2領域R2における複数の交差点IS2の一部に配置されていない。

(もっと読む)

半導体装置

【課題】半導体装置の特性を向上させる。

【解決手段】LDMOSと、LDMOSのソース領域と電気的に接続されるソースプラグP1Sと、ソースプラグP1S上に配置されるソース配線M1Sと、LDMOSのドレイン領域と電気的に接続されるドレインプラグP1Dと、ドレインプラグP1D上に配置されるドレイン配線M1Dと、を有する半導体装置のソースプラグP1Sの構成を工夫する。ドレインプラグP1Dは、Y方向に延在するライン状に配置され、ソースプラグP1Sは、Y方向に所定の間隔を置いて配置された複数の分割ソースプラグP1Sを有するように半導体装置を構成する。このように、ソースプラグP1Sを分割することにより、ソースプラグP1SとドレインプラグP1D等との対向面積が低減し、寄生容量の低減を図ることができる。

(もっと読む)

配線パターン及びその製造方法並びに半導体装置

【課題】配線パターンを覆う絶縁層をできる限り薄くする。

【解決手段】配線パターン1は、第一の一対の端子3,4及び該第一の一対の端子3,4間を接続する複数の第一の引き回し部5を有する第一の配線2と、第二の一対の端子7,8及び該第二の一対の端子7,8間を接続する少なくとも一つの第二の引き回し部9を有する第二の配線6とを含む。

(もっと読む)

半導体装置

【課題】半導体装置の小型化、特に、狭ピッチ化に対する技術を提供する。

【解決手段】半導体チップ1C上に設けられたパッド2と、プローブ領域10Aおよび接続領域10Bのパッド2上に開口部11を有し、半導体チップ1C上に設けられたパッシベーション膜3と、接続領域10Bのパッド2上に開口部12を有し、パッド2上およびパッシベーション膜3上に設けられたパッシベーション膜5と、パッド2と電気的に接続され、接続領域10B上およびパッシベーション膜5上に設けられた再配線7とを備える。接続領域10Bより半導体チップ1Cの外周部側に設けられたプローブ領域10Aのパッド2にプローブ痕100が存在し、接続領域10Bから半導体チップ1Cの中央部側に延びて再配線7が存在している。

(もっと読む)

半導体装置およびその製造方法

【課題】シェアードコンタクトの接触不良を防止して、半導体装置の製造歩留まりを向上させることのできる技術を提供する。

【解決手段】高密度版回路における電界効果トランジスタTr3のゲート電極G3と電界効果トランジスタTr4のゲート電極G4とのピッチは、高速版回路における電界効果トランジスタTr1のゲート電極G1と電界効果トランジスタTr2のゲート電極G2のピッチよりも小さいが、シェアードコンタクトホールSCが達する部分のゲート電極G3に切欠を設けることにより、シェアードコンタクトホールSCと不純物領域S/Dとの接触面積を広くする。

(もっと読む)

半導体装置

【課題】短いチップリング幅で、優れたクラックストップ機能や水分浸入防止機能を発揮することが可能な半導体装置を提供する。

【解決手段】基板と、基板上に形成された基板の外周に沿って環状に形成された第1のダミー環状配線3Aを含む第1の配線層3と、第1の配線層上に形成された基板の外周に沿って環状に形成された第2のダミー環状配線5Aを含む第2の配線層5と、第1の配線層と前記第2の配線層との間に形成された複数のビアプラグ4とを備え、複数のビアプラグ4は、第1のダミー環状配線3Aと第2のダミー環状配線5Aとの間に形成され、それぞれが環状の平面形状を有し、基板の外周に沿う方向に延びるよう、互いに接続された複数の環状ビアプラグ4Aと、環状ビアプラグ4Aの外部において、環状ビアプラグ同士が接続された部分付近に存在する環状ビアプラグの窪み付近に、窪みに面するように配置された外部ビアプラグ4Cを含む。

(もっと読む)

半導体装置

【課題】機械的強度が比較的弱い材料を層間絶縁膜の材料として用いる場合であっても、集積度が高く、信頼性の高い半導体装置を提供する。

【解決手段】支持基板10と、支持基板上に形成され、絶縁層26,28,38,44,50,56,62,68を介して複数の配線36,42,48,54,60,66を積層して成る多層配線構造と、多層配線構造上に形成された電極パッド78と、多層配線構造を貫いて支持基板に達し、電極パッドを支持する構造物76であって、断面が十字形又はY字形である構造物とを有している。この構造物により電極パッドが支持されているため、ボンディングを行った際に電極パッドの下方に存在する構成要素に大きなストレスが加わるのを防止することができ、多層配線構造の一部に、機械的強度が比較的弱い層間絶縁膜を用いた場合であっても、微細な配線パターンの変形や断線等、トランジスタの破壊等を防止することができる。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、多層配線構造を有する半導体装置及びその製造方法に関し、信頼性や製造歩留りが高く、設計的な制約の小さい半導体装置及びその製造方法を提供することを目的とする。

【解決手段】基板10上に形成された配線20、40、60、80と、配線20、40、60、80の周囲に形成された低誘電率膜12、32、52、72、92と、低誘電率膜12、32、52、72、92の形成材料より弾性係数の大きい誘電体材料で形成され、基板面に垂直に見て配線20、40、60、80に重なって配置された補強用絶縁膜42a、62a、82a、102aと、配線20、40、60、80に交差して配置された補強用絶縁膜22b、42b、62b、82b、102bとを有するように構成する。

(もっと読む)

半導体装置

【課題】チップ面積を拡大することなく信頼性の高い配線レイアウトを実現する。

【解決手段】信号線S1〜S3と電源線VDD1,VSS1がY方向に延在する下層配線層と、信号線S4〜S6と電源線VDD2,VSS2がX方向に延在する上層配線層と、対応する信号線が重なり合うオーバーラップ領域OL1に設けられたビア導体VE1と、対応する電源線が重なり合うオーバーラップ領域OL2,OL3に設けられたビア導体VE2,VE3とを備える。領域OL1のX方向における幅は、領域OL2,OL3のX方向における幅よりも広く、これにより、領域OL1には複数のビア導体VE1a,VE1bが設けられる。また、電源線VDD1,VSS1は、領域OL1との干渉を避けるようY方向に分断されている。複数の下層配線は、一つのビアを含むミニマムピッチで2つのビアを配置している。

(もっと読む)

半導体装置、回路基板及び電子機器

【課題】信頼性の高い半導体装置及びその製造方法、回路基板並びに電子機器を提供することにある。

【解決手段】電極114は集積回路112に電気的に接続されている。半導体基板110の電極114が形成された面に、電極114を避けて樹脂層118が形成されている。配線122は、電極114に電気的に接続されており、樹脂層118の側面121と上面120の境目に形成された第1の部分150と、第1の部分150に接続されて樹脂層118の上面120に形成された第2の部分152と、を有する。第1の部分150は第2の部分152よりも広い幅で形成されている。外部端子124が配線122に電気的に接続されている。

(もっと読む)

半導体装置

【課題】コンタクトパッドを含む所定領域内に形成できる配線数を増加させることができ、設計レイアウトの自由度を向上させることができるパターンレイアウトを有する半導体装置を提供する。

【解決手段】第1方向に所定ピッチでラインとスペースが交互に配列された第1配線パターンと、第1配線パターンのライン間に配置され、所定ピッチの3倍の幅を有するコンタクトパッド30Bとを有する。第1配線パターンのラインとコンタクトパッドとの間隔は所定ピッチであり、所定ピッチは100nm以下である。

(もっと読む)

半導体装置及びその作製方法

【課題】マスク枚数を増加させることなく、積層構造の導電層の下層が露出した構造を有する半導体装置の作製方法を提供する。

【解決手段】ソース電極及びドレイン電極層を形成する導電膜を2層の積層構造で形成し、該導電膜上にエッチングマスクを形成し、該エッチングマスクを用いて該導電膜をエッチングし、該エッチングマスクを残した状態で該導電膜の上層をサイドエッチングして該導電膜の下層の一部を露出させてソース電極及びドレイン電極層とする。このように形成したソース電極及びドレイン電極層と画素電極層は、露出された下層の部分において接続される。ソース電極及びドレイン電極層を形成する導電膜は、例えば、下層をTi層とし、上層をAl層とすればよい。エッチングマスクに開口部が複数設けられていてもよい。

(もっと読む)

半導体装置、パターンレイアウト作成方法および露光マスク

【課題】 高集積化に有効な複数の配線パターンを含む配線パターン群を備えた半導体装置を提供すること。

【解決手段】 同一の配線用途のN(N≧3)本の配線パターンを含む配線パターン群を含む。N本の配線パターンの各々は別の層の配線郡内の配線パターンと電気的に接続するための接続領域を含む。N本の配線パターンは、配線パターンN1と、配線パターンN1の長手方向と異なる一方向に配置された二つ以上の配線パターンNi(i≧2)を含む。二つ以上の配線パターンNiはiの値が大きいほど配線パターンN1から離れた位置に配置され、二つ以上の配線パターンNiは少なくとも一つ以上のパターンNp(2≦p<N)と少なくとも一つ以上の配線パターンNq(p<q≦N)を含む。少なくとも一つ以上の配線パターンNpはpの値が大きいほど長手方向の寸法が長く、少なくとも一つ以上の配線パターンNqは、qの値が大きいほど、長手方向の寸法が短い。

(もっと読む)

半導体装置

【課題】2つのトランジスタを混載した半導体装置において、ダミー配線を介して配線間で短絡が発生するのを防止し、信頼性の高い混載デバイスを実現可能にする。

【解決手段】本発明の半導体装置は、微細CMOS4Aと、微細CMOS4Aに接続される微細配線15とを有する微細CMOS領域と、微細CMOS4Aよりも耐圧が高い高耐圧デバイス4Bと、高耐圧デバイス4Bに接続され、平面視において微細配線15よりも配線幅が広いドレイン配線115及びソース配線116と、を有する高耐圧デバイス領域と、を具備し、高耐圧デバイス領域には、電気的に孤立したダミー配線14が少なくともドレイン配線115及びソース配線116に隣接して配置されない。

(もっと読む)

半導体素子及びその半導体素子のパターン形成方法

【課題】 フォトリソグラフィ工程の解像限界内で、具現可能なサイズのパターンを利用して超微細な幅及び間隔を持つ高密度パターンを形成できる配置構造を持つ半導体素子及びその半導体素子パターン形成方法を提供する。

【解決手段】 半導体素子は、コネクション領域に隣接するメモリセル領域を含む基板、メモリセル領域からコネクション領域まで第1方向に延びて配され、第1ライン幅及び第1ライン間隔を持つ複数の第1導電ライン、第1導電ラインそれぞれに連結されるように配され、第2ライン幅及び第2ライン間隔を持つ複数の第2導電ライン、コネクション領域に配され、第1導電ラインに電気的に連結された複数のパッド、を備える。半導体素子上のパターン形成方法は、微細ライン幅及び間隔を提供するために2段階のスペーサ形成工程を含むことができる。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】容量増加による高周波特性の劣化及び裏面電極に起因する絶縁破壊を抑止し、チップ面積を増加させることなく、インパクトイオン化により生成したホールを容易且つ確実に引き抜いて排出することを可能として、高耐圧性及び高信頼性を実現する化合物半導体装置及びその製造方法を提供する。

【解決手段】絶縁性又は半絶縁性の基板1の表面に電子走行層3、電子供給層4が形成され、電子供給層4内には局所的なp型領域7が形成されており、基板1の裏面にp型領域7の一部を露出させる開口1aが形成され、開口1aを導電材料で埋め込みp型領域7とオーミック接続された裏面電極8を備え、AlGaN/GaN・HEMTが構成される。

(もっと読む)

半導体装置のレイアウト方法及びその半導体装置

【課題】トランジスタのしきい電圧の変化を減らすことにより、半導体装置の信頼性を向上させることができる半導体装置のレイアウト方法及びその半導体装置を提供する。

【解決手段】半導体基板内に形成された少なくとも1つの第1電極と第2電極を有する複数個のトランジスタのアクチブ領域を配置する段階と、前記複数個のトランジスタのアクチブ領域のそれぞれの少なくとも1つの第1電極と第2電極との間に位置し、前記半導体基板上に所定の幅と長さを有する1つ以上の実質的に同一間隔に分離された前記複数個のトランジスタのゲートを配置する段階と、前記複数個のトランジスタの間に、所定の幅と長さを有し、前記半導体基板上に前記複数個のトランジスタの分離されたゲートの間隔と実質的に同一間隔に配置された複数個のダミーゲートを配置する段階とを有する。

(もっと読む)

半導体装置

【課題】ボンディングパッドの直下の酸化膜を壊すことなくウエハテストを行う。

【解決手段】半導体基板9と、半導体基板9上に形成された5層の配線層と、前記5層の配線層のうち、最上層の第5配線層5に形成され、それぞれ一部が露出した複数のボンディングパッド5eと、半導体基板9上に形成され、かつボンディングパッド5eの下において平面視でボンディングパッド5eと重なる位置に配置され、さらにボンディングパッド5eと電気的に接続されたトランジスタ素子等の能動素子と、を有しており、ボンディングパッド5eの直下には、5層の配線層のうちのいずれの配線層も設けられていない緩衝膜7が形成されている。

(もっと読む)

半導体装置

【課題】信号線の上面に微小な凹凸が形成されても、伝送線路の伝送特性が劣化することを抑制できるようにする。

【解決手段】信号線522は、多層配線層400及び再配線層500の第a層(a≧2)に形成されている。プレーン配線444は多層配線層400及び再配線層500の第b層(b<a)に形成されており、平面視で信号線522と重なっている。2つのコプレーナ配線524は多層配線層400及び再配線層500の第c層(b≦c≦a)に形成されており、平面視で信号線522と平行に延伸しており、かつ信号線522を挟んでいる。信号線522からプレーン配線444までの距離hは、信号線522からコプレーナ配線524までの距離wより短い。信号線522の上方のうち、信号線522からwと同じ高さの範囲内には、電源線、グランド線、及び他の信号線が位置していない。

(もっと読む)

41 - 60 / 488

[ Back to top ]