Fターム[5F033MM21]の内容

半導体集積回路装置の内部配線 (234,551) | 配線構造、形状の特徴点 (15,803) | 配線の平面形状 (698)

Fターム[5F033MM21]の下位に属するFターム

スリットを有するもの (119)

凹凸を有するもの (91)

Fターム[5F033MM21]に分類される特許

161 - 180 / 488

配線パターンの形成方法、トランジスタ素子基板並びに表示装置

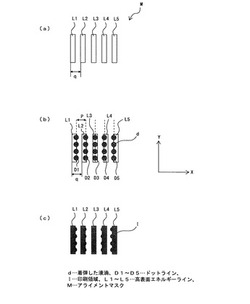

【課題】濡れ性制御パターンとインクジェット印刷パターンとのアライメントを容易に高精度で合わせる配線パターンの形成方法を提供し、トランジスタ素子基板並びに表示装置を提供する。

【解決手段】濡れ性変化層に高表面エネルギーラインL1〜L5がピッチqで配列されてなるアライメントマークMを形成する工程と、ドットラインD3の目標着弾点の中心線が高表面エネルギーラインL3の中心線に一致するように、仮に設定された印刷開始位置からインクジェット法によりピッチqとは異なる間隔の印刷ピッチpでドットラインD1〜D5をテスト印刷するテスト印刷工程と、テスト印刷ラインごとの高表面エネルギーラインからのインクのはみ出し状態からドットラインとお互いの中心線が略一致する高表面エネルギーラインのライン配列における位置を検出する検出工程と、前記検出結果を基に、前記印刷開始位置を調整する印刷位置調整工程とを有する。

(もっと読む)

半導体デバイスにおけるはんだバンプ接続を改善するための構造体及び方法

【課題】 改善されたはんだバンプ接続を有する構造体及びそのような構造体を製造する方法を提供する。

【解決手段】 改善されたはんだバンプ接続を有する構造体及びこのような構造体を製造する方法が、提供される。この構造体は、コンタクト・パッドを露出させるように誘電体層内に形成されたビアと、ビア内及び誘電体層の上に形成されたキャプチャ・パッドとを含む。キャプチャ・パッドは、セグメント化された構造部を形成するように、誘電体層の上に開口部を有する。はんだバンプは、キャプチャ・パッド及び誘電体層の上の開口部上に堆積される。

(もっと読む)

エレクトロマイグレーション耐性を有するビア・ライン相互接続体

【課題】 エレクトロマイグレーション耐性を有するビア・ライン間相互接続構造体及びその製造方法を提供する。

【解決手段】 導電性ビアの上層金属ライナと、下方の金属ラインの下層金属ライナとの間に、ライナ・ライナ間接触を形成する。ライナ・ライナ間接触は、急激なエレクトロマイグレーションによる故障を抑制し、金属相互接続構造体のエレクトロマイグレーション耐性を強化する。少なくとも1つの誘電体材料部分は、上層金属ライナと下層金属ライナの間の直接接触を保証するように配置された複数の誘電体材料部分を含むことができる。代替的に、少なくとも1つの誘電体材料部分は、リソグラフィ・オーバーレイ変動の許容範囲内でライナ・ライナ間直接接触が形成されるのを保証するのに十分な、導電性ビア領域との横方向の重なりを有する領域の単一の誘電体部分を含むことができる。

(もっと読む)

半導体素子及びそのパターン形成方法

【課題】多様な幅を有するパターンを同時に形成しつつ、一部領域ではダブルパターニング技術によりパターン密度を倍加させる半導体素子のパターン形成工程、及びその工程を容易に適用しうる構造を有する半導体素子を提供する。

【解決手段】半導体素子であって、基板上で第1方向に延長される第1ライン部分と該第1ライン部分の一端から前記第1方向とは異なる第2方向に延長される第2ライン部分とを含む複数の導電ラインと、前記複数の導電ラインの各々の前記第2ライン部分の一端と一体に接続されている複数のコンタクトパッドと、前記複数のコンタクトパッドのうち、選択された一部のコンタクトパッドから前記第2方向に沿って前記第2ライン部分と平行に延長される第1ダミー部分を各々有する複数のダミー導電ラインとを有する。

(もっと読む)

半導体素子及び半導体素子のパターン形成方法

【課題】多様な幅を有するパターンを同時に形成しつつ、一部領域ではダブルパターニング技術によりパターン密度を倍加させる半導体素子のパターン形成工程及び該工程を容易に適用可能な構造の半導体素子を提供する。

【解決手段】半導体素子は、第1方向に相互平行に延びている複数のラインパターンを含む。複数のラインパターンのうちから選択される複数の第1ラインパターンは、第2方向に沿って交互に選択されて両側で各々隣接している2つのラインパターンの両端部のうち、素子領域の第1端部にさらに近い各端部に比べて、第1端部からさらに遠く位置する第1端部を有する。複数のラインパターンのうちから選択される複数の第2ラインパターンは、第2方向に沿って交互に選択され、両側で各々隣接している2つのラインパターンの両端部のうち、第1端部にさらに近い各端部より、第1端部からさらに近く位置する第2端部を有する。

(もっと読む)

半導体装置およびその製造方法

【課題】

厚い配線を形成すると、絶縁膜との間に剥離が生じやすい。

【解決手段】

半導体装置は、複数の半導体素子を形成した半導体基板と、半導体基板上方において、半導体基板表面とほぼ平行な第1レベルに延在する第1の配線パターンであって、異なるレベルの配線またはパッドとの接続領域を含む平面形状を有し、第1の厚さを有する主配線領域と主配線領域の側壁から1つ以上の段差を形成して外側に張り出し、第1の厚さより薄い第2の厚さを有し、主配線領域から連続する張り出し配線領域とを有する第1の配線パターンと、第1の配線パターンを囲む第1の絶縁領域と、を有する。

(もっと読む)

パッシベーション層のクラックの発生を防止した集積回路の製造方法

【課題】パッシベーション層のクラックの発生を防止する。

【解決手段】エッチング及びダマシン法を用いて製造される集積回路においては、金属配線層から周囲の誘電体材料に応力が伝達されることによって、デバイスに組み込まれる配線層(400)の周囲の誘電体材料にクラックが発生することが一般的である。本発明は、周囲の誘電体層に伝達される応力を低減することができると考えられる丸められたコーナを有する配線層を形成することにより、この問題を解決する。

(もっと読む)

半導体装置及びその製造方法

【課題】能動素子、受動素子等の損傷や特性変化を防止しつつ、より小型化が図れる半導体装置を提供する。

【解決手段】複数の層2〜4が積層された半導体装置において、最上部に位置する第1配線層59と、最上部から下方の2番目に位置する第2配線層54と、第1配線層59と第2配線層54の間に形成された金属膜56と、金属層56の外周に形成され、第1配線層59と第2配線層54を接続する第1導電性プラグ58と、金属膜56及び第1配線層59の上方に形成されたパッド62と、パッド62と第1配線59を接続する第2導電性プラグ61とを有する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】半導体装置に設けられた半導体部品等の電極パッドとそれに接続されるべくインクジェット法により形成される配線との電気的な接続を好適に確保することのできる半導体装置、及びその半導体装置の製造方法を提供する。

【解決手段】半導体装置の第2電極パッド15に電気的に接続される金属配線膜19が、銀微粒子を分散媒に分散させた導電性インクからなる液滴(液層25L)の配置及び乾燥により形成される。このとき、第2電極パッド15の表面のメッキ層21に銀微粒子の結合層からなる中間層23Dを形成した後、中間層23Dを覆うかたちに上記分散媒を撥液する撥液材料を含む撥液層24を積層する。これにより、金属配線膜19は、その乾燥焼成を通じて中間層23Dと物理的に接続するようになり、撥液層24を間に挟みつつ第2電極パッド15と物理的に接続され、すなわち電気的にも接続されるようになる。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】溝の交差部分の中央部に窪みが形成されることを抑制でき、かつ半導体装置の歩留まりが低下することを抑制できる半導体装置の製造方法を提供する。

【解決手段】この半導体装置の製造方法は、基板100に第1の溝110及び第1の溝110と交差する第2の溝120を形成する工程と、基板100に対して成膜処理を行うことにより、第1の溝110内及び第2の溝120内に膜200を埋め込む工程と、基板100上に位置する膜200を除去する工程とを備える。そして第1の溝110及び第2の溝120を形成する工程において、第1の溝110と第2の溝120の交差部分130に、平面視において交差部分130の角の一つから交差部分130の中央に向けて延伸する凸部140を形成する。

(もっと読む)

半導体装置

【課題】パッドとバンプとの接触端を起点にクラックが発生したとしても、該クラックによって半導体基板が受けるダメージを低減することができる構造を提供する。

【解決手段】第1半導体チップ10において第1パッド部12を貫通して第1絶縁層11cに達する第1トレンチ13を設け、第2半導体チップ20において第2パッド部22を貫通して第2半導体基板21に達する第2トレンチ23を設ける。そして、バンプ30によって第1半導体チップ10と第2半導体チップ20とをフリップチップ接合する。このとき、各トレンチ13、23が、各パッド部12、22にバンプ30が接触した接触面のうちの外縁部に配置されるようにする。これにより、該接触面において各トレンチ13、23よりも内側に進展するクラック15、25を阻止することができる。

(もっと読む)

半導体装置

【課題】従来の透過型液晶パネル向け半導体装置を小型化し、マイクロディスプレイを実現しようとするとき、半導体装置と透明電極とを接続するビアホールの径が縮小するため、接触抵抗が高くなるという問題があった。また、接触抵抗低減のために、半導体装置と透明電極との間に中間金属層を設けると、画素の開口率が低下し、画面が暗くなるという課題があった。

【解決手段】本発明の半導体装置は、半導体装置と透明電極との間に設ける中間金属層に切欠部を有する。この切欠部により、中間金属層の側面の面積を拡大し、透明電極との接触面積を従来よりも大きくすることができる。また、中間金属層の側面部面積を利用するため、画素表面に対する投影面積を小さく設定でき、画素の開口率を大きくすることができる。このため、十分な明るさをもつ、超小型のマイクロディスプレイを提供できる。

(もっと読む)

電子デバイス及びその製造方法

【課題】塗布プロセス(印刷やIJ)により製造が可能であって、電磁波照射による異常放電がなく、生産効率及び生産安定性が高く、かつキャリア移動度及びon/off比が向上した電子デバイス及びその製造方法を提供することにある。

【解決手段】基板上に、電極を有し、少なくとも1部に熱変換材料または熱変換材料を含むエリアと、前記熱変換材料または熱変換材料を含むエリアに隣接もしくは近接して電磁波吸収能を持つ物質または電磁波吸収能を持つ物質を含むエリアを配置し、電磁波を照射して、該電磁波吸収能を持つ物質が発生する熱により、熱変換材料を機能材料に変換する電子デバイスの製造方法において、前記電極の辺が形成する角が全て90°より大きく180°より小さい、または、曲面であることを特徴とする電子デバイスの製造方法。

(もっと読む)

チップを有する半導体装置

【課題】チップの基板への実装工程前の、パッドとバンプ間の接続状態の良否判定の信頼性を高める。

【解決手段】チップ10が基板に実装された半導体装置であって、チップ10に配置され、チップ10の内部回路と電気的に接続するパッド群Aと、チップ10のうちパッド群Aが配置された領域以外の領域に配置されたテスト用パッドパターンBとを備え、パッド群Aは、チップ10の主面に形成された複数のパッド12aと、複数のパッド12aの各々の上にバリアメタル膜を介して形成され、基板と電気的に接続するバンプ16aとを有し、テスト用パッドパターンBは、チップ10の主面に形成された複数のテスト用パッド12bと、複数のテスト用パッド12bの各々の上にテスト用バリアメタル膜を介して形成されたテスト用バンプ16bと、複数のテスト用パッド12bのうち互いに隣り合うテスト用パッド12b間を電気的に接続する配線11bとを有する。

(もっと読む)

半導体素子

【課題】半導体素子に形成する出力パッドと内部回路の出力端子とを接続する配線の配線抵抗を抑える。

【解決手段】出力端子18の各々が基板の外周の一辺(第1の辺31)の側に沿って配列されるように基板の中央部に第1の辺31に沿って複数の内部回路16が形成される。第1の辺31に沿った領域には、複数の第1出力パッド14Aが形成され、第1の辺31に対向する第2の辺32に沿った領域には、複数の第2出力パッド14Bが形成される。複数の内部回路16の出力端子のいずれかと複数の第2出力パッド14Bのいずれかとを各々接続する複数の第2配線42の単位配線長当たりの抵抗値が、複数の内部回路16の出力端子18のいずれかと複数の第1出力パッド14Aのいずれかとを各々接続する複数の第1配線41の単位配線長当たりの抵抗値より低くなるように第2配線42の各々を形成する。

(もっと読む)

半導体装置

【課題】チャネル長を、トランジスタごとに自由に設計が可能な半導体装置を提供する。

【解決手段】複数の半導体柱2が立設された半導体基板1と、半導体柱2の外周面に設けられたゲート絶縁膜7と、半導体柱2の外周面を覆うゲート電極8と、半導体柱2の上側に設けられた第1不純物拡散領域3と、半導体柱2の下側に設けられた第2不純物拡散領域4と、を備え、第1不純物拡散領域3の厚さが半導体柱2ごとに異なっていることを特徴とする半導体装置。

(もっと読む)

半導体装置及び該半導体装置のレイアウト方法

【課題】半導体装置及び該半導体装置のレイアウト方法を提供する。

【解決手段】複数のビットラインパターンと、複数のビットラインパターンにそれぞれ連結されて形成される複数のパッドパターンと、パッドパターンに形成される少なくとも一つのコンタクトと、を備え、パッドパターンのピッチは、ビットラインパターンのピッチより長い半導体装置とする。

(もっと読む)

半導体装置

【課題】ソース/ドレインの配線抵抗の上昇を抑制し、ゲート配線の低抵抗化を図る。

【解決手段】もっとも半導体基板10側に位置する第1配線層20は、半導体素子のソース領域15に電気的に接続された第1ソース配線21と、半導体素子のドレイン領域12に電気的に接続された第1ドレイン配線22と、ゲート電極17に電気的に接続された中継部23とを備えている。そして、第1ソース配線21および第1ドレイン配線22にそれぞれ設けられたソース側凹部21aおよびドレイン側凹部22aによって設けられた間隙24にこの中継部23を配置する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】バンプの配列に疎密差があったときに発生する応力を緩和できる、半導体装置及び半導体装置の製造方法を提供する。

【解決手段】電極端子群を備える配線基板と、バンプ3群が形成されたバンプ形成面7を備え、バンプ3群が前記電極端子群と対向するように前記配線基板上に実装された半導体チップとを具備し、バンプ形成面7は、バンプ3が配置された領域の面積密度が第1密度である第1領域9と、バンプ3が配置された領域の面積密度が前記第1密度よりも小さい第2密度である第2領域10と、第1領域9と第2領域10との境界部分に設けられた第3領域11とを備え、第3領域11は、バンプ3が配置された領域の面積密度が、前記第2密度よりも大きく、前記第1密度よりも小さい。

(もっと読む)

リバースエンジニアリングを防ぐための導電性チャネル擬似ブロック処理方法及びその回路

【課題】リバースエンジニアリングに対して集積回路構造を偽装するための技術及び構造を提供する。

【解決手段】集積回路構造は、制御された外形を有する材料の複数の層により構成される。シリサイド金属層は、基板の活性領域において備えられ、活性領域に隣接して接続しているチャネル接続においてギャップを有する。そのチャネルはチャネルブロック構造を有し、チャネルブロック構造は、導電性又は絶縁性のどちらかであるように、リバースエンジニアリングにおいて識別可能であるようにみえる。

(もっと読む)

161 - 180 / 488

[ Back to top ]