Fターム[5F033MM26]の内容

半導体集積回路装置の内部配線 (234,551) | 配線構造、形状の特徴点 (15,803) | 表面状態 (80) | 配線の表面に凹凸やうねりがあるもの (72)

Fターム[5F033MM26]に分類される特許

21 - 40 / 72

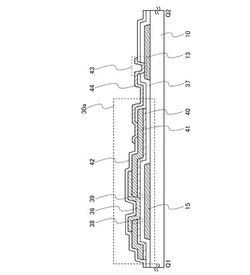

表示装置

【課題】動作特性に優れ低温で製造可能な酸化物半導体を用いた表示装置の特性を活かすには、適切な構成を備えた保護回路等が必要となる。

【解決手段】ゲート電極15を被覆するゲート絶縁層37と、ゲート絶縁層37上においてゲート電極15と端部が重畳し、第2酸化物半導体層40と導電層41が積層された一対の第1配線層38及び第2配線層39と、少なくともゲート電極15と重畳しゲート絶縁層37及び該第1配線層38及び該第2配線層39における導電層41の側面部及び上面部の一部と第2酸化物半導体層40の側面部と接する第1酸化物半導体層36とを有する非線形素子30aを用いて保護回路を構成する。

ゲート絶縁層37上において物性の異なる酸化物半導体層同士の接合を形成することで、ショットキー接合に比べて安定動作をさせることが可能となり、接合リークが低減し、非線形素子30aの特性を向上させることができる。

(もっと読む)

半導体装置及びその製造方法

【課題】 ソフトエラーを低減することが可能な半導体装置及びその製造方法を提供することを目的とする。

【解決手段】 電極パッドを有する半導体チップが形成される半導体基板と、前記電極パッドに設けられる内部接続端子と、前記複数の半導体チップと前記内部接続端子とを覆うように設けられる絶縁層と、前記絶縁層を挟んで前記内部接続端子と接続される配線パターンと、を有する半導体装置であって、前記絶縁層は、ポリイミド及び/又はポリイミド系化合物等のα線を遮蔽する材料を含んで構成されることを特徴とする。

(もっと読む)

不揮発性記憶装置の製造方法

【課題】微細な構造でも安定して製造可能な不揮発性記憶装置の製造方法を提供する。

【解決手段】第1の方向に延在する第1の配線と、前記第1の方向と非平行な第2の方向に延在する第2の配線と、前記第1の配線と前記第2の配線との間に挟持され、前記第1の配線と前記第2の配線とを介して供給される電流により、第1の状態と第2の状態との間を可逆的に遷移可能な記録層と、を有する不揮発性記憶装置の製造方法であって、前記第1の配線の層を形成する工程と、前記第1の配線の層の主面上に前記記録層の層を形成する工程と、前記記録層の層と前記第1の配線の層を選択的にエッチングして、前記第1の方向に延在する複数の積層体を形成する工程と、前記複数の積層体の間隙の表面に、気相成長法を用いて第1の絶縁層を形成する工程と、前記第1の絶縁層の上に、塗布法を用いて第2の絶縁層を形成する工程と、を備えたことを特徴とする不揮発性記憶装置の製造方法を提供する。

(もっと読む)

半導体装置、電気光学装置及び電子機器

【課題】基板上の受動素子を用いてインピーダンス制御を行うために、高精度の抵抗部を容易に形成する。

【解決手段】半導体装置121の能動面121aの周縁部には、複数の電極パッド24が配列形成され、半導体装置121の能動面全体に保護膜としてのパッシベーション膜26が形成されており、上述した各電極パッド24の表面に、パッシベーション膜26の開口部26aが形成されている。パッシベーション膜26上には、応力緩和性の高い有機樹脂膜が形成される。そのパッシベーション膜26の表面であって、電極パッド列24aの内側には、樹脂突起12が形成されている。樹脂突起12は、半導体装置121の能動面121aから突出して形成され、略同一高さで直線状に延在しており、電極パッド列24aと平行に配設されている。

(もっと読む)

凹型ソケットを有する環状バイアを備えるダイスタッキング

凹型導電性ソケットを備える環状バイアを有するダイを含むダイスタックおよびそのダイスタックを形成する方法は、様々な電子システムで使用するための構造を提供する。一実施形態において、ダイスタックは、別のダイの凹型導電性ソケット中に挿入されたダイの頂部上に導電性ピラーを含む。 (もっと読む)

半導体チップ、光電変換チップおよび半導体チップの製造方法

【課題】衝撃や振動になどに対して強度を向上させることで高い信頼性が得られる半導体チップ、光電変換チップおよび半導体チップの製造方法を提供する。

【解決手段】半導体基板2と、受光部3および制御回路部4とを形成する集積回路と、前記半導体基板2の側面に形成され、半円筒形状に形成された外部端子5と、底面を除く全体を覆う樹脂封止部6とを備えた光電変換チップ1は、プリント配線基板に搭載する場合に、ワイヤによる接続が不要なので、ワイヤボンディング工程が不要である。

(もっと読む)

半導体装置及びその製造方法

【課題】歩留りが高く且つ配線間容量を十分に低減でき、且つ機械的強度を十分に得られるようにする。

【解決手段】半導体装置は、半導体基板の上に形成された第1の層間絶縁膜101と、第1の層間絶縁膜101に形成された複数の配線105と、第1の層間絶縁膜101に複数の配線105の少なくとも1つと接続するように形成されたビア113及びダミービア106とを有している。第1の層間絶縁膜101における互いに隣り合う配線105同士の間には空隙部109が選択的に形成されており、ダミービア106は、空隙部109と接する配線105Aの下側に該配線105Aと接続して形成され、ビア113及びダミービア106は、空隙部109を介することなく第1の層間絶縁膜101により周囲を覆われている。

(もっと読む)

半導体装置及びその製造方法

【課題】Cu膜からなる配線層と封止樹脂層との密着性を向上させ、両層間での剥離を防止し信頼性の高い半導体装置を提供する。

【解決手段】本発明に係る半導体装置1A(1)は、一面に電極3を配してなる半導体基板2と、前記半導体基板の一面を覆うように配され、前記電極と整合する位置に電極用の開口部αを有する絶縁樹脂層4と、前記絶縁樹脂層の一部を覆うように配され、前記開口部αを通して前記電極と電気的に接続される配線層5と、を少なくとも備える半導体装置であって、前記配線層は、Cu膜からなり、該配線層の表面が10nm〜300nmの凹凸形状を有することを特徴とする。

(もっと読む)

半導体集積回路装置の製造方法

【課題】デバッグ等のために、完成した半導体集積回路装置の配線をFIB加工を用いて事後的に修正する場合がある。修正配線は配線として最適に材料を使用すべきである。しかし、たとえば、比抵抗の低い金属は、比較的その後の検査・試験環境に弱い等の問題がある。

【解決手段】本願発明は、ほぼ完成した半導体集積回路装置の配線を変更するために、FIB加工を用いて半導体集積回路チップの配線を修正するに当たり、半導体集積回路チップの主面上の絶縁膜に金属修正配線をFIBCVDにより形成後、その上を覆うように、金属修正配線よりも耐酸化性または耐腐食性の高い金属被覆膜を、FIBCVDにより形成するものである。

(もっと読む)

半導体装置及びその製造方法

【課題】電極間において強度の高い接合が可能で、かつ低コスト化が可能な半導体装置及びその製造方法を提供すること。

【解決手段】本発明は、第1半導体チップ10と、第1半導体チップ10に設けられた第1電極12と、第1半導体チップ10が実装される第2半導体チップ20と、第2半導体チップ20に設けられた、突起24を有する第2電極22と、第1電極12と第2電極22を接合し、前記突起24の側面の少なくとも一部を覆う半田バンプ14とを具備している半導体装置及びその製造方法である。

(もっと読む)

半導体装置及びその製造方法並びに電子デバイス

【課題】本発明は、接着剤の特性に依存せずに電気的な絶縁信頼性を確保することを目的とする。

【解決手段】電子デバイスは、半導体装置と、複数の基板電極40を有する配線パターン36が形成されて半導体装置が搭載された配線基板34と、を有する。複数の配線24と複数の基板電極40とが対向して電気的に接続する。樹脂突起18は、半導体装置と配線基板34の対向方向に圧縮されて、露出部28が基板電極40に密着する。樹脂突起18の表面は、複数の第1の領域20と、複数の第1の領域20よりも低くなった複数の第2の領域22と、を交互に有する。それぞれの第1の領域20は、いずれかの配線24が載る支持部26と、支持部26及び第2の領域22の間で配線24から露出する露出部28と、を含む。

(もっと読む)

半導体装置およびその製造方法

【課題】 突起電極と電極パッドとの接着性が良好な半導体装置と、この半導体装置を短い処理工程で形成可能な製造方法を提供することである。

【解決手段】 半導体基板1に形成した絶縁膜3の開口から露出する電極パッド2と、電極パッド表面に形成されたプローブ痕5と電極パッド上とに設ける共通電極層8、9と、共通電極層8、9上に設ける突起電極13を有する半導体装置において、プローブ痕5の庇5aの下に感光性樹脂6を設ける半導体装置と、電極パッド2表面にプローブ針4を接触させてプローブテストを行なうプローブテスト工程と、このプローブテスト工程にて電極パッド2表面に生じるプローブ痕5の庇5aの下に自己整合的に感光性樹脂6を形成する感光性樹脂形成工程と、共通電極層8、9を形成する工程と、共通電極層8、9の上に突起電極13を形成する工程を有する半導体装置の製造方法。

(もっと読む)

電気回路素子およびその製造方法

【課題】誘電体層に新たな材料を用いる必要がなく、構造が単純で低コストのキャパシタを実現する。

【解決手段】基板1上に設けられた第1の樹脂層2と、第1の樹脂層2上に設けられた第1の配線層3と、第1の配線層3を覆い第1の樹脂層2上に設けられた第2の樹脂層4と、第2の樹脂層4上に設けられた第2の配線層5とを少なくとも備え、第1の配線層3および第2の配線層5がキャパシタを構成した電気回路素子とする。第1の配線層3または第2の配線層5の少なくとも一方が金属めっき層からなることが好ましい。

(もっと読む)

半導体装置およびその製造方法

【課題】小型化が可能で、信頼性の高い外部接続(パッド)構造をもつ半導体装置を提供する。また、低コストで製造作業性が良好な外部接続構造をもつ半導体装置を提供する。

【解決手段】所望の素子領域の形成された半導体基板1と、外部接続用端子部3の外部接続領域4の周縁を覆うように塗布形成された保護膜6とを具備した半導体装置であって、前記外部接続領域を囲むように前記保護膜の内縁を画定する画定領域5を具備している。

(もっと読む)

半導体装置およびその製造方法

【課題】容量素子の歩留まりおよび信頼性の低下を抑制する。

【解決手段】半導体装置100は、半導体基板の上部に設けられ、SiO2膜103およびSiO2膜103中に埋設された第一銅配線105を含む第一配線層、第一配線層上に設けられたSiO2膜109、SiO2膜109上に設けられたSiO2膜111、SiO2膜111上に設けられた容量素子121を含む。容量素子121は、SiO2膜111上に設けられた下部電極115、下部電極115の上部に対向して設けられた上部電極119およびこれらの間に設けられた容量絶縁膜117から構成されている。第一銅配線105の上面に突起部135が設けられている。SiO2膜111の上面は平坦である。

(もっと読む)

Al合金膜を用いた低接触電気抵抗型電極およびその製造方法並びに表示装置

【課題】Al合金中の合金元素を少なくしても、透明酸化物導電膜との接触抵抗を低くすることのできる低接触電気抵抗型電極、およびこうした電極を製造するための有用な方法、並びにこうした電極を備えた表示装置を提供する。

【解決手段】本発明の低接触電気抵抗型電極は、酸化物透明導電膜と直接接触するAl合金薄膜からなる低接触電気抵抗型電極において、前記Al合金は、Alよりもイオン化傾向が小さい金属元素を0.1〜1.0原子%の割合で含有し、且つAl合金薄膜の酸化物透明電極と直接接触するAl合金薄膜表面は、最大高さ粗さRzで5nm以上の凹凸が形成されたものである。

(もっと読む)

電子部品の実装方法

【課題】本発明の目的は、製造から実装までの工程を効率的に行うことができる電子部品及び半導体装置、その製造方法及び実装方法、回路基板並びに電子機器を提供することにある。

【解決手段】パッケージサイズがチップサイズに近くて応力吸収層を有し、パターニングされたフレキシブル基板を省略でき、かつ、複数の部品を同時に製造することができる半導体装置である。ウエーハ10に電極12を形成する工程と、電極12を避けてウエーハ10に応力緩和層としての樹脂層14を設ける工程と、電極12から樹脂層14の上にかけて配線としてのクローム層16を形成する工程と、樹脂層14の上方でクローム層16に外部電極としてのハンダボールを形成する工程と、ウエーハ10を個々の半導体チップに切断する工程と、を有し、クローム層16及びハンダボールの形成工程には、ウエーハプロセスにおける金属薄膜形成技術が適用される。

(もっと読む)

半導体装置

【課題】多層配線構造を有する半導体装置において、製造工程を増加させることなく形成される、外部との電気接続信頼性の高い電極パッドを備える半導体装置を提供すること。

【解決手段】 この半導体装置1において、第2配線層4の上には、第3配線層5が形成されている。第3配線層5には、所定パターンのAl配線36(各バリア膜34,35,37を含む)が形成されている。Al配線36は、層間膜38に被覆されている。この層間膜38の上には、表面保護膜39が積層されている。そして、表面保護膜39および層間膜38には、これらの膜を膜厚方向に貫通する、パッド開口40が形成されている。Al配線36は、パッド開口40内に臨む部分が、外部との電気接続のための電極パッドとして露出している。

(もっと読む)

集積回路のためのコンタクトパッドおよびコンタクトパッドの形成方法

集積回路中のコンタクトパッドが開示される。コンタクトパッドは、コンタクトパッドの底部(302)を含む平坦部と、平坦部から延在し平坦部に実質的に垂直な複数の突起(304、306、308、310、312)と、突起および平坦部に取付けられたはんだボール(108、124)とを含む。コンタクトパッドを形成する方法も開示される。  (もっと読む)

(もっと読む)

素子搭載用基板およびその製造方法、半導体モジュールおよびその製造方法、ならびに携帯機器

【課題】回路素子にダメージをあまり与えることなく配線を形成する技術を提供する。

【解決手段】半導体モジュールの製造方法において、絶縁層16の一方の面上に導電性バンプ20を形成する第1の工程と、絶縁層16の他方の面から導電性バンプ20を露出させる第2の工程と、導電性バンプ20の露出した箇所および絶縁層16の他方の面上に第1の配線層18を設ける第3の工程と、回路素子が形成された半導体基板であって、基板の表面に電極が形成されている半導体基板を用意する第4の工程と、第3の工程により第1の配線層18が設けられた導電性バンプ20と、電極とを対向させた状態で、絶縁層16と半導体基板とを圧着して導電性バンプ20を絶縁層16に埋め込む第5の工程と、を含む。

(もっと読む)

21 - 40 / 72

[ Back to top ]