Fターム[5F033NN33]の内容

半導体集積回路装置の内部配線 (234,551) | 層間構造の特徴点 (9,232) | コンタクトホールの形状 (1,366) | コンタクトホールの平面形状 (560)

Fターム[5F033NN33]の下位に属するFターム

コンタクトホールの大きさ、数 (291)

Fターム[5F033NN33]に分類される特許

41 - 60 / 269

半導体装置、半導体装置の製造方法、及び半導体装置の検査方法

【課題】層間絶縁膜に生じたボイドを高感度に検出する。

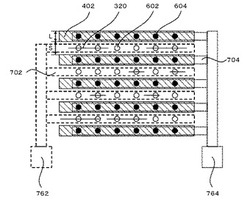

【解決手段】この半導体装置は、多層配線層(非図示、以下略)と、多層配線層中に形成された第一TEGパターン(非図示)を備える。第一TEGパターンは、互いに平行に延伸した複数の第一下層配線402と、層間絶縁膜(非図示)を貫通し、平面視で第一下層配線402間に位置する第一ビア602と、多層配線層の最上層(非図示)に形成され、第一ビア602に接続している第一端子762と、上記した同一の最上層に形成され、第一下層配線402に接続している第二端子764と、を備える。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体基板に設けられた穴に、絶縁体を介して2つの導電体を充填してなる電極部を有する半導体装置において、2つの導電体間の容量を大きくするのに適した構成を提供する。

【解決手段】半導体基板10の第1の領域1には、表面11に開口する複数個の有底穴20が設けられ、第2の領域2には貫通穴30が設けられ、有底穴20は貫通穴30よりも小さい穴幅を有する。絶縁体50を両導電体40、60で挟んでなる積層構造体が、有底穴20および貫通穴30に充填され、さらに、第1の領域1において複数個の有底穴20間にて連続して形成されており、第1の領域1は、当該積層構造体による容量形成部として構成される。有底穴60における各導電体40、60は、それぞれ貫通穴30における各導電体40、60に電気的に接続されて、半導体基板10の表裏両面11、12に取りだされている。

(もっと読む)

半導体装置およびその製造方法

【課題】ソース・ドレイン領域とコンタクトプラグの接続部分の電気抵抗が低減され、かつ短チャネル効果の発生が抑えられたトランジスタを有する、n型およびp型トランジスタを含む半導体装置、およびその半導体装置の製造方法を提供すること。

【解決手段】不純物高濃度領域を有する半導体装置を提供する。前記不純物高濃度領域は、第1のソース・ドレイン領域内の前記第1のソース・ドレイン領域と前記第1のコンタクトプラグとの界面近傍に形成される。前記不純物高濃度領域の前記第1のコンタクトプラグの底面の長手方向の前記第1のコンタクトプラグの前記底面の輪郭からの前記不純物高濃度領域の輪郭の広がり幅の少なくとも一方は、前記第1のコンタクトプラグの前記底面の短手方向の前記第1のコンタクトプラグの前記底面の輪郭からの前記不純物高濃度領域の輪郭の広がり幅よりも大きい。

(もっと読む)

半導体装置、パターンレイアウト作成方法および露光マスク

【課題】 高集積化に有効な複数の配線パターンを含む配線パターン群を備えた半導体装置を提供すること。

【解決手段】 同一の配線用途のN(N≧3)本の配線パターンを含む配線パターン群を含む。N本の配線パターンの各々は別の層の配線郡内の配線パターンと電気的に接続するための接続領域を含む。N本の配線パターンは、配線パターンN1と、配線パターンN1の長手方向と異なる一方向に配置された二つ以上の配線パターンNi(i≧2)を含む。二つ以上の配線パターンNiはiの値が大きいほど配線パターンN1から離れた位置に配置され、二つ以上の配線パターンNiは少なくとも一つ以上のパターンNp(2≦p<N)と少なくとも一つ以上の配線パターンNq(p<q≦N)を含む。少なくとも一つ以上の配線パターンNpはpの値が大きいほど長手方向の寸法が長く、少なくとも一つ以上の配線パターンNqは、qの値が大きいほど、長手方向の寸法が短い。

(もっと読む)

半導体装置及びその製造方法

【課題】Cdsubの低減を通じて、出力容量Cossの低減に寄与する半導体装置及びその製造方法を提供する。

【解決手段】半導体基板と半導体基板上に絶縁膜を介して形成された第1導電型の半導体層とを有するSOI基板と、第1導電型の半導体層からなる活性領域内に、第2導電型の半導体層からなるウェルを形成するとともに、ウェル内および第1導電型の活性領域内に、第1導電型の半導体層からなるソース・ドレイン領域を形成した横型MOSFETにおいて、活性領域のうち、ドレイン領域にコンタクトするように形成されるドレインパッド形成領域9p下の少なくとも一部は、SOI基板の絶縁膜に到達するように形成された絶縁性領域11で構成される。

(もっと読む)

半導体素子及びその製造方法

【課題】半導体素子のビア構造物及び導電構造物を提供する。

【解決手段】前記ビア構造物は、平坦部及び突出部を含む表面を有する。前記導電構造物は前記平坦部のうち、少なくとも一部上に形成され、前記突出部のうち、少なくとも一部上には形成されない。例えば、前記導電構造物は前記平坦部上のみに形成されて前記突出部上には全く形成されない。これによって、前記導電構造物と前記ビア構造物との間に高品質の接続を形成することができる。

(もっと読む)

貫通電極を持つ半導体装置

【課題】貫通電極を持つ半導体装置を提供する。

【解決手段】パッドと、パッドの下部に配される貫通電極と、を備える半導体装置。貫通電極は、円筒形の第1金属プラグと、第1金属プラグの外周を取り囲む第1半導体レイヤと、第1半導体レイヤの外周を取り囲む第2金属プラグと、第1金属プラグの外周を取り囲む第2半導体レイヤと、第1金属プラグの外周に、第1半導体レイヤ及び第2金属プラグの内周及び外周に、そして第2半導体レイヤの内周に形成される少なくとも一つの絶縁膜と、を備え、第1半導体レイヤ内に第1絶縁膜との界面から広がる空乏層が形成されるように、第1半導体レイヤに第1バイアス電圧を印加するが、第1バイアス電圧は、第2半導体レイヤに印加される第2バイアス電圧とは異なる。

(もっと読む)

半導体素子、及びその形成方法

【課題】 信頼性が向上する半導体素子、及びその形成方法を提供する。

【解決手段】 半導体素子の形成方法は、半導体基板100の上にゲート電極120及びゲート電極120の両側にスペーサー110を形成する段階、ゲート電極120の上にキャッピングパターン170を形成する段階、ゲート電極120の間にメタルコンタクト195を形成する段階を含み、キャッピングパターン170の幅はゲート電極120の幅より大きく形成される。これにより、形成された半導体素子は、メタルコンタクト195とゲート電極120との間での電気的な短絡を效果的に防止することができる。

(もっと読む)

液晶表示装置の製造方法

【課題】配線破断を軽減する構造を有する液晶表示装置の製造方法を提供する。

【解決手段】基板上にゲート配線及び信号配線、ゲート絶縁膜、半導体パターン、データ配線、保護膜、ドレーン電極を露出させる第1接触孔及び信号配線を露出させ、側辺の長さが幅より大きく形成される複数の第2接触孔、第1及び第2接触孔を通じてドレーン電極に連結される画素電極及び信号配線に連結される信号配線補助パッドを形成する液晶表示装置の製造方法であって、信号配線を形成する段階では、信号配線に一対一に対応する複数の信号リードを有する信号伝送用フィルムを含み、信号伝送用フィルムには複数の信号リードのうちの高電圧信号を伝送する第1信号リードと低電圧信号を伝送する第2信号リードとの間にダミーリードが形成され、ダミーリードに対応するダミー配線が基板に形成され、ダミー配線は信号配線より酸化傾向が小さい特性を有する導電物質で形成される。

(もっと読む)

固体撮像装置およびその製造方法

【課題】高速動作に有利な固体撮像装置およびその製造方法を提供する。

【解決手段】固体撮像装置は、多層配線層73と、前記多層配線層上に設けられ、貫通トレンチを有する半導体層64と、前記貫通トレンチ内部に埋め込まれた第1導電層69と、前記第1導電層の周囲に形成された第1絶縁膜32と、前記第1絶縁膜の周囲に形成された第1導電型の第1不純物拡散層36とを備える。

(もっと読む)

基板の製造方法、半導体装置の製造方法、電気光学装置

【課題】任意の方向に傾斜した開口部を形成可能な基板の製造方法、半導体装置の製造方法、およびこれを適用した半導体装置を備えた電気光学装置を提供すること。

【解決手段】本適用例の素子基板101の製造方法は、素子基板101上に設けられた半導体装置としてのTFT110を覆うと共に第1開口部としての孔104aが設けられた第2絶縁膜としての層間絶縁膜104をマスクとして、素子基板101の面法線101aと交差する一の方向からドライエッチングを第1絶縁膜としてのゲート絶縁膜103に施して、孔104aに連通すると共にTFT110のドレイン電極110dに開口する第2開口部としての孔103aを形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】ウェーハの裏面研削やダイシングの際に生じる、水分の浸入による汚れ、あるいは割れ、クラック、チッピング、層間剥離等の物理的損傷を抑制することを目的とする。

【解決手段】基板11上のチップ領域12の周縁部にその内側の部分を連続して取り囲むよう有機保護膜23’を形成する。また、パッシベーション膜22および有機保護膜23がキャップ層47上に閉環状開口部を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】信頼性を損なうことなく更なる集積化を実現し得る半導体装置を提供する。

【解決手段】第1のトランジスタL1のゲート電極を含み、第1のコンタクト層48aを介して第2のトランジスタL2のソース/ドレイン拡散層20に電気的に接続される、直線状の第1のゲート配線16aと、第2のトランジスタL2のゲート電極を含み、第2のコンタクト層48bを介して第1のトランジスタのソース/ドレイン拡散層22に電気的に接続される、第1のゲート配線と平行な直線状の第2のゲート配線16bと、第1のゲート配線及び第2のゲート配線を覆うように形成された絶縁膜であって、第1のゲート配線と第2のトランジスタのソース/ドレイン拡散層とを露出し、長辺方向が第1のゲート配線の長手方向である第1の開口部46aが形成された絶縁膜と、第1の開口部内に埋め込まれた第1のコンタクト層とを有している。

(もっと読む)

半導体集積回路装置

【課題】フリップチップ構造を有する半導体集積回路装置において、パッドからチップ内部素子へ加わる応力の影響に起因するタイミング信頼性の劣化を低コストで防止する。

【解決手段】フリップチップ構造を有する半導体集積回路装置において、応力の影響を受ける半導体チップ101の外周列におけるパッド102の構造及び配置位置等について、応力の影響に起因するLSIの動作不具合が発生しにくいように予めレイアウトする。

(もっと読む)

貫通電極、微小構造体及びそれらの製造方法

【課題】短時間で製造することができ、十分な気密性を有するとともに、基板の反りを低減させることができる貫通電極、微小構造体及びそれらの製造方法を提供する。

【解決手段】導電性を有する基板10の所定領域を貫通トレンチ21で囲み、貫通トレンチ21内に絶縁膜50を形成して周囲から絶縁分離した貫通電極60において、絶縁膜50は、貫通トレンチ21の側面から化学気相成長させたシリコン膜40を熱酸化したシリコン熱酸化膜50である。

(もっと読む)

配線基板の製造方法

【課題】スループットが向上し、且つ少ない液滴量でも第1の電極と第2の電極とを導通性を確保する。

【解決手段】基体10の表面10aに形成された微細穴2の底部2aとなる下面電極3と、基体10の表面10aであって微細穴2の内壁部2bの上端近傍に配置された上面電極5とを導通させる導電層12を形成する。この導電層12の形成において、まず、金属ナノ粒子11を分散させるためのクリアインク8を微細穴2に充填する。次に、微細穴2に金属ナノ粒子11を含有する液滴を供給し、金属ナノ粒子11を微細穴2内のクリアインク8で分散させる。次に、微細穴2内のクリアインク8を揮発させることで、微細穴2の底部2a及び内壁部2bに析出した金属ナノ粒子膜11Aを有する導電層12を形成する。

(もっと読む)

半導体装置

【課題】半導体装置の微細化を犠牲とすることなく、ビアの冗長性を向上させ、歩留まりが高い半導体装置を実現できるようにする。

【解決手段】半導体装置は、半導体基板の上に形成された第1の配線211aと、第1の配線211aよりも上層に形成された第3の配線231aと、第1の配線211aと第3の配線231aとを接続する第1のビア221aとを備えている。第1のビア221aの形成位置と第3の配線231aの端部との間隔t1は、第2の配線と第2の配線よりも上層の第4の配線とを接続する第2のビアの形成位置と第4の配線の端部との間隔よりも小さい。第1のビア221aの半導体基板と平行な方向の断面積は、第2のビアの半導体基板と平行な方向の断面積よりも大きい。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】上層の電極のコンタクトホール内でのカバレージを向上させること。

【解決手段】本発明の実施形態に係る半導体装置の製造方法において、第1エッチング工程で形成されるコンタクトホール300aの上部領域300Uaの中心部分からずれた位置に、第2エッチング工程で形成されるコンタクトホールの下部領域300Daが形成される。これにより、上部領域300Uaの下底部分に水平領域が存在し、その近くにおいては、第2電極30のオーバハング30hが生じにくくなり、カバレージが向上する。

(もっと読む)

半導体装置

【課題】低誘電率誘電体材料などからなる層間絶縁膜を用いた多層配線構造を有する半導体装置において、機械的ストレス又は熱的ストレスに起因する層間絶縁膜のクラック又は剥離等を確実に防止する。

【解決手段】半導体基板のチップ領域の外周部にシールリング4が設けられていると共に、当該チップ領域におけるシールリング4の近傍にチップ強度強化用構造体5が設けられている。チップ強度強化用構造体5は複数のダミー配線構造(例えばダミー配線構造5A〜5E等)から構成されている。各ダミー配線構造5A〜5E等はそれぞれ、最下層及び最上層の配線層のいずれか一方のみを含むか又はいずれも含まない2層以上の配線層に亘ってビア部を介して連続的に形成されている。

(もっと読む)

絶縁性外郭部と、該外郭部内に位置しかつ該外郭部から分離された導電性領域と、で構成されたTSV相互接続構造体の製造

【課題】本発明は、相互接続構造体の製造方法に関する。

【解決手段】本発明の相互接続構造体の製造方法は、基板(100)内における、閉じた外郭部を形成する少なくとも一つのトレンチ(103,105)及び前記閉じた外郭部の内側に位置する少なくとも一つのホール(102,104)の形成を含み、トレンチ及びホールが、基板の領域によって分離され、また、本方法は、トレンチを誘電性材料(111)で充填するステップと、ホールを導電性材料(117,122)で充填するステップと、を含む。

(もっと読む)

41 - 60 / 269

[ Back to top ]