Fターム[5F033NN33]の内容

半導体集積回路装置の内部配線 (234,551) | 層間構造の特徴点 (9,232) | コンタクトホールの形状 (1,366) | コンタクトホールの平面形状 (560)

Fターム[5F033NN33]の下位に属するFターム

コンタクトホールの大きさ、数 (291)

Fターム[5F033NN33]に分類される特許

61 - 80 / 269

半導体装置

【課題】 貫通穴の開口寸法が小さく小型化や微細化を容易にでき、貫通穴全体の金属層形成速度を向上する事が容易で、金属層形成工程に要する時間を短縮する事が容易な貫通穴形状を構成した半導体装置を提供することを目的とする。

【解決手段】 基板の表面と裏面とを接続する貫通穴内に金属層を設けた半導体装置において、貫通穴側壁に表面と裏面とを結ぶ向きに複数の突起を設けた事を特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】ゲート電極と拡散層に接続する共通コンタクトにおけるリークを防ぐ。

【解決手段】半導体装置は、拡散層が形成された基板と、基板上に形成されたゲート電極と、基板上にゲート電極よりも高い位置まで形成された第1絶縁層と、拡散層に電気的に接続され、第1絶縁層を貫通する第1コンタクトと、ゲート電極と電気的に接続された第2コンタクトと、第1絶縁層の上に形成された第2絶縁層とを備える。第1コンタクトと第2コンタクトとは第1絶縁層の上面以上の高さにおいて電気的に接続する。ゲート電極上と拡散層上は異なるコンタクトで形成されているため、ゲート電極のサイドウォールが減少することなく、リークを防ぐことができる。

(もっと読む)

クラックストップを備えたデバイス

基板上のデバイスと基板内のクラックストップとを備える装置である。デバイスを形成する方法も開示される。これらの方法は、半導体デバイスのようなデバイスを第1の厚さを有する基板上に設けることと、基板の厚さを第2の厚さまで低減することと、クラックストップを基板内に設けることとを含み得る。基板の厚さを低減することは、この基板を支持用の担体基板に取り付けることと、その後、この担体基板を取り外すこととを含み得る。クラックストップは、クラックがデバイスに到達することを妨げ得る。  (もっと読む)

(もっと読む)

インダクターおよび集積回路装置

【課題】 インダクター配線のインピーダンスの低減と、インダクター配線と基板等との間に形成される寄生容量の低減とを共に実現する。

【解決手段】 多層配線を利用して基板上に構成されるインダクターは、第n層の導体層ME(n)により形成される第1インダクター配線100と、第1インダクター配線100と電気的に接続される、第(n+α)層(αは、1以上の整数)の導体層ME(n+1)により形成される第2インダクター配線200と、を有し、第1インダクター配線100にはスリットが設けられておらず、第2インダクター配線200には、第2インダクター配線の延在方向に沿う少なくとも一つのスリットSL1が設けられている。

(もっと読む)

積層型半導体装置

【課題】積層された複数の半導体チップ間で貫通電極切替情報を共有する。

【解決手段】複数の半導体チップ間でデータ転送を行うための複数の貫通電極を互いに共有した積層型半導体装置であって、複数の半導体チップに含まれる第1の半導体チップIFは、複数の貫通電極のうちデータ転送を行う貫通電極を指定する貫通電極切替情報SWを保持し、複数の半導体チップに含まれる第2の半導体チップCC0〜CC7に貫通電極切替情報SWを転送する。本発明によれば、貫通電極切替情報SWが第1の半導体チップIFから第2の半導体チップCC0〜CC7に転送されることから、第2の半導体チップには貫通電極切替情報SWを不揮発的に記憶する回路を設ける必要がない。これにより、第2の半導体チップのチップ面積を縮小することが可能となる。

(もっと読む)

半導体記憶装置

【課題】層間接続により生ずるチップ面積の増大を抑制し、コスト削減を実現する半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、半導体基板と、前記半導体基板上に前記半導体基板と垂直方向にそれぞれ複数層形成された互いに交差する複数の第1及び第2の配線、並びにこれら第1及び第2の配線の各交差部に接続された複数のメモリセルを有するセルアレイブロックと、前記セルアレイブロックの第n層目(nは自然数)の第1の配線と前記第n層目の第1の配線以外の第1の配線、前記半導体基板、又は他の金属配線とを接続する前記セルアレイブロックの積層方向に延びる第1のビア配線とを備える。前記第1のビア配線は、前記セルアレイブロックの積層方向と直交する断面が楕円形状であり、この断面の長径方向が前記第1の配線方向に対し垂直であることを特徴とする。

(もっと読む)

半導体装置及びその製造方法

【課題】プログラム後の誤読み出しを抑制でき、高い信頼性を備える半導体装置及びその製造方法を提供すること。

【解決手段】半導体基板1上のチャンネル領域に形成されたゲート酸化膜3と、前記ゲート酸化膜3上に形成されたゲート電極4と、前記チャンネル領域の少なくとも一部に形成されたシリサイド層2と、を有し、前記シリサイド層2は、前記チャンネル領域のうち前記ゲート電極4の全体を除く領域の少なくとも一部を被覆する。

(もっと読む)

半導体基板の製造方法

【課題】半導体基板が厚い場合においても貫通電極を高生産性、高品質で低コストで実現できる半導体基板の製造方法を提供することを目的とする。

【解決手段】半導体基板(101)にアクティブ面が露出する開口部(104)を有する電極パッド(102)を形成し、開口部(104)からアクティブ面の反対側の面に向かって凹部(105a)を形成し、凹部(105a)の内側に絶縁膜(106)を形成し、絶縁膜(106)と電極パッド(102)の表面に導電経路(107)を形成し、アクティブ面の反対側の面から半導体基板(101)を薄型化して凹部(105a)の底部を貫通させる。

(もっと読む)

半導体装置

【課題】 入出力部の電源配線の近傍にバイパスコンデンサを配置する場合、LSIの端子数が多くなると、バイパスコンデンサを配置するための領域を確保することが困難になる。

【解決手段】 半導体基板の表面に、電子回路素子が形成されている電子回路領域が画定される。半導体基板の上に、一方に基準電位が印加され、他方に電源電圧が印加される第1及び第2の配線が配置される。シールリングが、電子回路領域を取り囲むように、半導体基板の上に配置される。シールリングは、第1の配線に電気的に接続される。第1の不純物拡散領域が、シールリングよりも内側において、半導体基板の表層部に形成される。第1の不純物拡散領域の上に誘電体膜が配置される。誘電体膜の上に、シールリングに電気的に接続され、導電材料で形成されたキャパシタ導電膜が配置される。

(もっと読む)

半導体装置およびその製造方法

【課題】チップサイズを大きくすることなく、チップ外周のガードリングの、外部応力に対する耐性を強化する。

【解決手段】この半導体装置は、半導体基板と、半導体基板上に形成された集積回路部と、半導体基板上の集積回路部の周辺に存在する絶縁層中に形成された、集積回路部を包囲するガードリング4と、を有する。ガードリング4は、半導体基板に対して垂直な方向に関して重なる位置に配された少なくとも2層の配線層M1,M2,M3と、これらの配線層間を接続するビア9a,9bと、で構成される。ビア9a,9bの形状が、ガードリング4の近傍に位置する一のダイシングライン3から垂直に集積回路部側へ向かう外部応力10を分散させる形状となっている。

(もっと読む)

貫通電極工程性能の試験ウエハ

【課題】ウエハを張り合わせて高集積デバイスを製造するためにウエハを貫通する電極を形成する。その製造工程を広い性能水準で評価するために共通に使用できるウエハ、即ちテストウエハが必要であった。

【解決手段】工程の広い性能水準を評価できるように、孔の形や深さ、底面の形、設計仕様を表す文字の入れ方を貫通電極の工程の特徴を踏まえて設計した。そのために、トレンチのパターンと孔の混在、丸から多角形・四角までの平面形状、異なる深さ、丸い底面を持つテストウエハを発明した。

(もっと読む)

半導体装置の製造方法

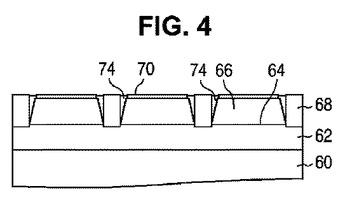

【課題】フォトリソグラフィーのプロセスマージンを確保すると共に、ゲート電極とコンタクトプラグとの短絡が生じにくい半導体装置の製造方法を実現できるようにする。

【解決手段】半導体装置の製造方法は、層間絶縁膜114の上に第1の下部開口部115aを有する第1のマスク層115を形成する工程と、第1のマスク層115の上に第1の下部開口部115aを通して層間絶縁膜114を露出する第1の上部開口部116aを有する第2のマスク層116を形成する工程とを備えている。第1の下部開口部115aは、隣接するゲート電極102同士の間に形成され、ゲート電極102と平行な方向に延びる長辺と、ゲート電極102と交差する方向に延びる短辺とを有する平面方形状である。第1の上部開口部116aは、各辺の長さが第1の下部開口部115aの短辺よりも長い平面方形状である。

(もっと読む)

配線形成方法及び半導体装置

【課題】パターン設計工数、使用マスク枚数及び重ね合わせずれを低減しつつ、微細なビアパターンの形成を可能にする。

【解決手段】ハードマスク膜18における2層目配線パターンと対応する開口部21と、第3のレジストパターン22における1層目配線パターンと対応する開口部23とが重なった領域に露出する部分の層間絶縁膜19Aに対してエッチングを行うことによって、ビア開口部26及び27を形成する。

(もっと読む)

半導体発光デバイス上に誘電体層を形成する方法

n型領域とp型領域との間に配置された発光層を有する半導体構造が形成される。n型領域の一部上に第1のメタルコンタクトが形成され、p型領域の一部上に第2のメタルコンタクトが形成される。第1及び第2のメタルコンタクトは半導体構造の同一面上に形成される。第1のメタルコンタクトと第2のメタルコンタクトとの間の誘電体材料が配置される。該誘電体材料は、半導体構造の一部、第1のメタルコンタクトの一部、及び第2のメタルコンタクトの一部と直接的に接触する。第1のメタルコンタクトの表面と、第2のメタルコンタクトの表面と、該誘電体材料の表面とを含む平坦面が形成される。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】導電層を自己整合的に形成する場合において、第1の拡散層コンタクトプラグのコンタクトマージンを比較的大きく取る。

【解決手段】半導体装置10は、第1のシリコンピラー14Aと、第1のシリコンピラー14Aの上面に設けられ、導電性材料が充填されたスルーホール30aを有する層間絶縁膜30と、スルーホール30aの上側開口部に設けられた第1の拡散層コンタクトプラグDC1とを備え、スルーホール30aの下側開口部の面積は前記第1のシリコンピラー14Aの上面の面積に等しくなっているとともに、スルーホール30aの上側開口部の面積はスルーホール30aの下側開口部の面積より大きくなっており、それによって、スルーホール30a内の導電性材料の第1の拡散層コンタクトプラグDC1との接続面の面積が第1のシリコンピラー14Aの上面の面積より大きくなっている。

(もっと読む)

重ね合わせ測定マーク及びパターン形成方法

【課題】重ね合わせ測定の精度を向上できる重ね合わせ測定マークを提供する。

【解決手段】第1パターンと第2パターンの重ね合わせ測定のためのマークにおいて、プラグ用ホールの開口パターンからなる第1パターンが形成された層間絶縁膜に該プラグ用ホールと同時に形成された第1ホールの開口パターンからなる第1マークと、前記層間絶縁膜に第1ホールと同時に形成され、前記プラグ用ホールの開口サイズと同程度で且つ第1ホールの開口サイズより小さい開口サイズを有する第2ホールの開口パターンからなる第2マークと、前記層間絶縁膜上の導電膜上に形成されたレジスト膜をパターニングして第2パターンと同時に形成されたレジストパターンからなる第3マークを含む構成とする。

(もっと読む)

半導体装置及びその製造方法

【課題】絶縁破壊に至らない微量の電荷の蓄積を抑制した半導体装置を実現できるようにする。

【解決手段】半導体装置は、半導体基板11の上に形成された半導体素子1及び保護ダイオード2を備えている。半導体基板11の上には、半導体素子1及び保護ダイオード2を覆うように第1の層間絶縁膜22が形成されている。第1の層間絶縁膜22には、半導体素子1と電気的に接続された第1のプラグ25と、保護ダイオード2と電気的に接続された第2のプラグ23、24とが形成されている。第2のプラグ23、24の上面の面積は、第1のプラグ25の上面の面積よりも大きい。

(もっと読む)

半導体装置

【課題】異なる配線層内に設けられた配線同士をコンタクト部を介して接続する際に、コンタクト部の特定の部分への電流集中を回避しうる構造を提供する。

【解決手段】半導体装置は、下層配線2と、配線部分32、及び配線部分32より配線幅の広い第1の幅広部22を有する上層配線1と、下層配線2と第1の幅広部22とを接続するコンタクト部3が配置されたコンタクト形成部26とを備えている。コンタクト形成部26は、第1の幅広部22の配線幅方向に平行な方向の長さL1が第1の幅広部22の配線長方向に平行な方向の長さL2よりも長い平面形状を有する。

(もっと読む)

半導体装置

【課題】高価な露光装置や高価なマスクを用いることなく、配線等のピッチを狭くすることができる半導体装置を提供する。

【解決手段】第1の導電パターン42と、第1の導電パターンに隣接して形成された第2の導電パターン42と、第1の導電パターンの所定領域下に形成された第1の導体プラグと、第1の導電パターンの所定領域上に形成された第2の導体プラグ62nと、第2の導電パターンのうちの、第1の導電パターンの所定領域に隣接する所定領域下に形成された第3の導体プラグと、第2の導電パターンの所定領域上に形成された第4の導体プラグ62n+1と、第1の導電パターン42の上方に形成され、第2の導体プラグに接続された第3の導電パターン62と、第2の導電パターンの上方に形成され、第4の導体プラグに接続された第4の導電パターン64とを有し、第4の導体プラグは、第2の導体プラグに対して、ずれた位置に配されている。

(もっと読む)

C4ボール内の均一な電流密度のための金属配線構造体

【課題】 C4ボール内の均一な電流密度のための金属配線構造体を提供する。

【解決手段】 1つの実施形態において、金属構造体のサブパッド・アセンブリが、金属パッドの直下に配置される。サブパッド・アセンブリは、金属パッドに当接する上位レベル金属ライン構造体と、上位レベル金属ライン構造体とその下方に配置された下位レベル金属ライン構造体との間の電気的接続をもたらす一組の金属ビアとを含む。別の実施形態において、C4ボールの信頼性は、C4ボール内部の均一な電流密度分布を助長するように分割及び分布させた一組の統合された金属ビアを有する金属パッド構造体を用いることによって高められる。複数の金属ビアの断面積の面密度は、金属パッドの中央部分において金属パッドの平担部分の周縁部分よりも高い。

(もっと読む)

61 - 80 / 269

[ Back to top ]