Fターム[5F033NN33]の内容

半導体集積回路装置の内部配線 (234,551) | 層間構造の特徴点 (9,232) | コンタクトホールの形状 (1,366) | コンタクトホールの平面形状 (560)

Fターム[5F033NN33]の下位に属するFターム

コンタクトホールの大きさ、数 (291)

Fターム[5F033NN33]に分類される特許

21 - 40 / 269

半導体チップ

【課題】金属原子の拡散に起因する素子特性の劣化を抑制する。

【解決手段】半導体チップは、半導体基板10と、半導体基板10を貫通する貫通電極20と、半導体基板10を貫通する金属柱40と、アライメントマーク47と、絶縁性を有する筒状の絶縁膜50とを有する。アライメントマーク40は、半導体基板10の外部に露出した金属柱40の端部によって形成されている。筒状の絶縁膜50は、半導体基板10に形成されており、金属柱40を取り囲んでいる。

(もっと読む)

半導体装置

【課題】伝送線路を接続するビア層の周囲のグラウンドを強化することができると共に、ビア部の特性インピーダンスを調整することが可能な半導体装置を提供する。

【解決手段】絶縁層14を介して積層された第1の半導体基体11及び第2の半導体基体21と、第1の半導体基体11に形成され、信号線12とグラウンド13とを含む第1の伝送線路と、第2の半導体基体21に形成され、信号線22とグラウンド23とを含む第2の伝送線路と、第1の伝送線路の信号線12及び第2の伝送線路の信号線22に接続された信号線用のビア層と、第1の伝送線路のグラウンド13及び第2の伝送線路のグラウンドに接続された、グラウンド用の第1のビア層と、第2の伝送線路のグラウンド23に接続され、かつ、信号線用のビア層に対向して形成された帯状のビア層を含む、グラウンド用の第2のビア層16を有する半導体装置を構成する。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体基板を貫通する貫通電極の周囲に形成される環状の絶縁分離部において、絶縁分離部を構成する酸化膜の応力により絶縁分離部周囲の半導体基板が変形する。

【解決手段】絶縁分離部の基板側に深さ方向に圧縮応力を与える第1の膜4を形成し、第1の膜4上に深さ方向に引張応力を与える第2の膜6膜を形成し、その際、第1及び第2の膜の膜厚を圧縮応力と引張応力とがほぼ釣り合うように調整する。

(もっと読む)

半導体装置及びその作製方法

【課題】多層配線を形成する際における配線の加工に要する工程を簡便にすることを課題

とする。また、開口径の比較的大きいコンタクトホールに液滴吐出技術やナノインプリン

ト技術を用いた場合、開口の形状に沿った配線となり、開口の部分は他の箇所より凹む形

状となりやすかった。

【解決手段】高強度、且つ、繰り返し周波数の高いパルスのレーザ光を透光性を有する絶

縁膜に照射して貫通した開口を形成する。大きな接触面積を有する1つの開口を形成する

のではなく、微小な接触面積を有する開口を複数設け、部分的な凹みを低減して配線の太

さを均一にし、且つ、接触抵抗も確保する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】デュアルダマシン法を用いて層間絶縁膜内にCu配線を形成する際、硬度が低い層間絶縁膜および硬度が高い層間絶縁膜のそれぞれに形成されたビアホール内に配線材料を良好に埋め込むことができるようにする。

【解決手段】第2層間絶縁膜17には、配線溝30aとビアホール28aとが形成されている。また、ビアホール28aの開口部には、第2層間絶縁膜17を斜め下方に後退(リセス)させることによって、テーパ状の断面形状を有するリセス部31が形成されている。これにより、ビアホール28aの開口部の直径は、開口部よりも下方の領域の直径に比べて大きくなり、ビアホール28aの直径が微細な場合であっても、ビアホール28aの内部に配線材料を良好に埋め込むことができる。

(もっと読む)

表示装置及びマスク

【課題】マスクの枚数を増やすことなく、ストレージキャパシタの電極間から半導体パターンを除去して高画質化を実現させる表示装置及びその製造方法を提供する。

【解決手段】本発明によるTFTパネルの製造では、半導体パターンとTFTのドレイン電極とを、同じマスクを利用したエッチングで同時にパターニングする。一方、画素電極の直下に形成される絶縁膜のパターニングには別のマスクを利用する。ドレイン電極を覆う絶縁膜の領域では、中央部の全体を感光させ、周辺部を半分の厚みまで感光させる。ストレージ電極の上方を覆う絶縁膜の領域は薄い一部を残して感光させる。ドレイン電極を覆う誘電膜をエッチングしてドレイン電極を露出させるとき、絶縁膜のその薄い一部がその下地の誘電膜を保護する。その後、絶縁膜のその薄い一部を画素電極の一部に置換し、保護された誘電膜を隔ててストレージ電極と対向させる。

(もっと読む)

半導体装置およびその製造方法

【課題】 はんだからなるバンプの形成工程中やフリップチップ実装時に、スズのようなはんだ成分がバンプ電極のアンダーバリアメタルを透過してその下のパッド電極と反応し、バンプとパッド電極間の接合信頼性が低下することを防止する。

【解決手段】 半導体基板1上に形成されたパッド電極3とはんだからなるバンプ8間にアンダーバリアメタル6が形成される。アンダーバリアメタル6は保護絶縁膜4に形成された開口5に露出するパッド電極3上から開口5周囲の保護絶縁膜4上までを被覆する。しかしバンプ8の底面はアンダーバリアメタル6より小さく、望ましくは開口5より小さく、且つ開口5内部領域の垂直上方に形成される。

(もっと読む)

半導体装置、電子デバイス及び電子デバイスの製造方法

【課題】対向するバンプ、パッド等を良好に接続し、接続部分の水平強度を高めるための半導体装置を提供する。

【解決手段】半導体基板2の上方に形成される第1絶縁膜15と、第1絶縁膜15内に形成される導電パターン19と、第1絶縁膜15上に形成される第2絶縁膜21と、第2絶縁膜21内に形成され、導電パターン19に接続されるビアプラグ24と、記ビアプラグ24の上に接続され、開口部25aを有する電極パッド25と、第2絶縁膜21内でビアプラグ24の周辺に形成される内部空間21aとを有し、電極パッド25上面及び開口部25a内には外部の突起状電極58が接続される。

(もっと読む)

半導体装置及びその製造方法

【課題】コンタクトホール内にめっき層から成るコンタクト層を埋め込んで上下層の電気的接続を行うときの、コンタクト層の埋め込み性を良好にする構造の半導体装置を提供する。

【解決手段】配線層12,16と、少なくとも底部において、三角形の平面形状であるコンタクトホール14と、めっき層から成り、コンタクトホール14の内部を埋めて形成され、配線層12,16に接続されたコンタクト層15とを含む、半導体装置を構成する。

(もっと読む)

半導体記憶装置

【課題】コンタクトプラグ同士のショートや、コンタクトプラグ間の耐圧の低下を抑制する。

【解決手段】半導体記憶装置は、基板と、前記基板内において、前記基板の主面に平行な第1方向に延びるように区画された複数の素子領域と、前記第1方向に垂直な第2方向に延びるように形成された複数の選択ゲートSGと、前記基板上において前記選択ゲート間に設けられており、個々の前記素子領域上に形成された複数のコンタクトプラグCWを含むコンタクト領域とを備え、前記コンタクト領域は、N個(Nは2以上の整数)の前記コンタクトプラグが、連続するN本の前記素子領域上に、前記第1及び第2方向に非平行な直線上に並ぶように形成された部分領域を複数有し、前記Nの値は、前記部分領域ごとに異なる値に設定され、前記コンタクトプラグの各々は、楕円形又は長方形の平面形状を有し、前記第1方向に対し、長辺が傾けられて配置されている。

(もっと読む)

半導体装置およびその製造方法

【課題】埋め込み絶縁層により活性層と支持基板とが電気的に絶縁された半導体基板において、支持基板の電位を活性層の表面から取り出すための基板コンタクトの低抵抗化を図ることができる半導体装置およびその製造方法を提供すること。

【解決手段】活性層16に素子領域4およびコンタクト領域5が形成された厚膜SOI基板2において、CMOSトランジスタ7のB/L層29およびL/I層37、npnバイポーラトランジスタ8のコレクタ層49と同一層に、n型基板コンタクト12の貫通コンタクト58を取り囲むn型コンタクト埋め込み層57を形成する。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】実施形態によれば、ホールの深さのばらつきを防ぐ半導体装置の製造方法及び半導体装置を提供する。

【解決手段】実施形態によれば、半導体装置の製造方法は、複数の第1の開口と第1の開口よりも密に並んだ複数の第2の開口とを有するマスクを用いて層間絶縁層61をドライエッチングし、第1の開口の下で下地層10に達する第1のホールと、第2の開口の下で下地層10に達する第2のホール41とを同時に形成する工程を備えている。第1のホールは他の第1のホールとは接することなく下地層10に達する。ドライエッチングの開始後、複数の第2の開口のそれぞれの下に複数のホールhが形成され、ドライエッチングの進行に伴って、複数のホールhは少なくとも開口端を含む上部42で互いにつながる。

(もっと読む)

電子デバイス及びその製造方法

【課題】バンプを排除した積層構造を備える電子デバイス、及びその製造方法を提供する。

【解決手段】本発明に係る電子デバイス1は、積層された複数枚の基板11〜13を含む。複数枚の基板は、それぞれ、板面を重ね合わせて積層され、1以上の貫通電極2を含んでいる。また、1以上の貫通電極2は、複数枚の基板11〜13のうち、2枚以上の基板11〜13にわたって延在する連続導体である。本発明に係る電子デバイス1は、このように、各基板の板面同士が重ね合わせられ、2枚以上の基板11〜13にわたって延在する連続導体である貫通電極2を備えている。したがって、本発明に係る電子デバイスは、複数枚の基板11〜13が、バンプを用いることなく、積層された構造を有している。

(もっと読む)

半導体装置

【課題】半導体装置の特性を向上させる。

【解決手段】LDMOSと、LDMOSのソース領域と電気的に接続されるソースプラグP1Sと、ソースプラグP1S上に配置されるソース配線M1Sと、LDMOSのドレイン領域と電気的に接続されるドレインプラグP1Dと、ドレインプラグP1D上に配置されるドレイン配線M1Dと、を有する半導体装置のソースプラグP1Sの構成を工夫する。ドレインプラグP1Dは、Y方向に延在するライン状に配置され、ソースプラグP1Sは、Y方向に所定の間隔を置いて配置された複数の分割ソースプラグP1Sを有するように半導体装置を構成する。このように、ソースプラグP1Sを分割することにより、ソースプラグP1SとドレインプラグP1D等との対向面積が低減し、寄生容量の低減を図ることができる。

(もっと読む)

半導体装置

【課題】短いチップリング幅で、優れたクラックストップ機能や水分浸入防止機能を発揮することが可能な半導体装置を提供する。

【解決手段】基板と、基板上に形成された基板の外周に沿って環状に形成された第1のダミー環状配線3Aを含む第1の配線層3と、第1の配線層上に形成された基板の外周に沿って環状に形成された第2のダミー環状配線5Aを含む第2の配線層5と、第1の配線層と前記第2の配線層との間に形成された複数のビアプラグ4とを備え、複数のビアプラグ4は、第1のダミー環状配線3Aと第2のダミー環状配線5Aとの間に形成され、それぞれが環状の平面形状を有し、基板の外周に沿う方向に延びるよう、互いに接続された複数の環状ビアプラグ4Aと、環状ビアプラグ4Aの外部において、環状ビアプラグ同士が接続された部分付近に存在する環状ビアプラグの窪み付近に、窪みに面するように配置された外部ビアプラグ4Cを含む。

(もっと読む)

集積回路装置およびその調製方法

【課題】 非常に複雑で費用がかかるバンプ・パッドを形成せずに、集積回路装置を製造する。

【解決手段】 集積回路装置100は、第1の環状誘電体ブロック21Aを有する底部ウェハー10Aと、底部ウェハー10A上に配置される、第2の環状誘電体21Bを有する少なくとも1つの積層ウェハー10Bと、実質的に直線状に底部ウェハー10A中へと積層ウェハー10Bを貫通する導電性ビア49とを備える。底部ウェハー10Aと積層ウェハー10Bはその間の接着層41により接合されている。底部ウェハー10Aと積層ウェハー10Bとの間にはバンプ・パッドは配置されない。導電性ビア49は、第1の環状誘電体ブロック21Aおよび第2の環状誘電体ブロック21Bの内部に位置している。

(もっと読む)

半導体装置

【課題】機械的強度が比較的弱い材料を層間絶縁膜の材料として用いる場合であっても、集積度が高く、信頼性の高い半導体装置を提供する。

【解決手段】支持基板10と、支持基板上に形成され、絶縁層26,28,38,44,50,56,62,68を介して複数の配線36,42,48,54,60,66を積層して成る多層配線構造と、多層配線構造上に形成された電極パッド78と、多層配線構造を貫いて支持基板に達し、電極パッドを支持する構造物76であって、断面が十字形又はY字形である構造物とを有している。この構造物により電極パッドが支持されているため、ボンディングを行った際に電極パッドの下方に存在する構成要素に大きなストレスが加わるのを防止することができ、多層配線構造の一部に、機械的強度が比較的弱い層間絶縁膜を用いた場合であっても、微細な配線パターンの変形や断線等、トランジスタの破壊等を防止することができる。

(もっと読む)

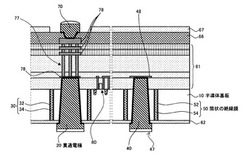

三次元積層構造を持つ半導体装置の製造方法

【課題】 三次元積層構造を持つ半導体装置において、積層された半導体回路層間の積層方向の電気的接続を、埋込配線を使用して容易に実現する半導体装置の製造方法を提供する。

【解決手段】 第1半導体回路層1aの半導体基板11の表面に、絶縁膜14で内壁面が覆われたトレンチ13を形成し、トレンチ13の内部に導電性材料を充填して導電性プラグ15を形成する。次に、トレンチ13とは重ならないように所望の半導体素子を基板11の表面または内部に形成し、その上に層間絶縁膜19を介して多層配線構造30を形成してから、多層配線構造30の表面にプラグ15に電気的に接続されたバンプ電極37を形成する。そして、電極37を用いて基板11を支持基板40に固定してから基板11をその裏面側から選択的に除去し、絶縁膜14を基板11の裏面側に露出させる。基板11の裏面側に露出せしめられた絶縁膜14を選択的に除去してプラグ15を露出させ、その端に電極42を形成する。

(もっと読む)

固定用構造および嵌合構造

【課題】チップの縁領域は、膨張係数が異なることによって、温度サイクル中に、TC応力とも称される特定の負荷を受けることが多い。これらの縁領域は特にTC応力を受け易いため、同領域内において様々な不良が生じる可能性がある。これによって、実際のデバイスにおける信頼性のリスクが増大する可能性がある。

【解決手段】半導体デバイスの金属構造210のための固定用構造200は、オーバーハング形状の側壁230を少なくとも1つ含んだ固定用凹部構造220を含んでいる。上記金属構造210は、少なくとも部分的に上記固定用凹部構造220内に配置されている。

(もっと読む)

半導体装置

【課題】放熱効率が高く低コストでの実装が可能な半導体装置を提供する。

【解決手段】第1の方向に延在するゲート電極を有する複数のトランジスタを有し、複数のトランジスタが第1の方向と交差する第2の方向に配置されたトランジスタアレイ54と、トランジスタアレイの第1の方向に配置され、複数のトランジスタのソース領域に電気的に接続されたパッド電極50とを有する。

(もっと読む)

21 - 40 / 269

[ Back to top ]