Fターム[5F033PP28]の内容

半導体集積回路装置の内部配線 (234,551) | 導電膜の成膜方法 (14,896) | 塗布又は液体からの成膜 (5,037) | 無電解メッキ (1,413)

Fターム[5F033PP28]に分類される特許

161 - 180 / 1,413

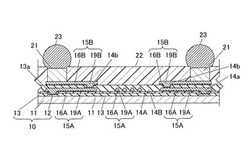

半導体装置及び半導体装置の製造方法

【課題】配線の検査効率を向上させる。

【解決手段】複数の接続パッド12が設けられた半導体デバイスウエハ10と、半導体デバイスウエハ10の接続パッド12が設けられた面を被覆するとともに、接続パッド12を露出させる開口14aが設けられた絶縁膜14Aと、開口14aから露出された接続パッド12及び絶縁膜14Aの上部に設けられた配線15Aと、を備える半導体装置である。配線15Aは、無電解めっき用シード層16Aと、無電解めっき用シード層16Aを核とする無電解めっきにより形成される配線層19Aと、を含む。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】再配線間のリークを抑制しつつ、再配線のピッチを微細化するとともに、再配線上のビア開口時のマージンを上げる。

【解決手段】緩衝層4上には再配線7bが形成され、再配線7b上には表面層8bが形成されている。表面層8bは、再配線7bから幅方向にはみ出すようにして再配線7bに沿うように配置され、再配線7bよりもエッチング耐性が高い。

(もっと読む)

半導体装置の製造方法

【課題】異方性エッチングを利用して、1つの銅膜に配線パターンとビアパターンとを同時に形成することが可能な半導体装置の製造方法を提供すること。

【解決手段】バリア膜100上に、銅膜101を形成する工程と、銅膜101上に、第1のマスク材を形成する工程と、第1のマスク材をマスクに用いて、銅膜101をバリア膜100が露出するまで異方的にエッチングする工程と、第1のマスク材を除去した後、異方的にエッチングされた銅膜101上に、第2のマスク材を形成する工程と、第2のマスク材をマスクに用いて、銅膜101をその途中まで異方的にエッチングする工程と、前記第2のマスク材を除去した後、異方的にエッチングされた銅膜101上に、絶縁物を堆積させ、異方的にエッチングされた銅膜101周囲に、層間絶縁膜106を形成する工程と、を具備する。

(もっと読む)

エッチング方法及びエッチングシステム

【課題】スループット良く、銅を、異方的にエッチングすることが可能なエッチング方法を提供すること。

【解決手段】 表面にマスク材102が形成された銅膜101に、マスク材102をマスクに用いて酸素イオン6を照射し、銅膜101内に、銅膜101の厚さ方向の全てに対して異方的に酸化された酸化銅103を形成する工程と、異方的に酸化された酸化銅103をエッチングする工程と、を具備する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】プローブ跡を除去でき、かつ、製造コストが増加することを抑制できる半導体装置及び半導体装置の製造方法を提供する。

【解決手段】この半導体装置は、回路が形成された基板100と、この基板100上に形成され、表面に保護絶縁膜300が形成された多層配線層と、この多層配線層の最上層の配線層に位置し、上記回路に接続し、かつ、表面が保護絶縁膜と略同一面となっている電極パッド200と、を備える。また、このような半導体装置の製造方法は、回路が形成された基板100上に、この回路に接続し、かつ、保護絶縁膜300から突出した突出部201を有する電極パッド200を形成する工程と、プローブ端子500を電極パッド200に接触させることにより、回路の動作テストを行う工程と、突出部201の少なくとも表面を研磨する工程と、有する。

(もっと読む)

半導体装置の製造方法

【課題】スループット良く、銅を異方的にエッチングすることを可能とするとともに、銅を用いたバンプ電極を短時間で形成することが可能な半導体装置の製造方法を提供すること。

【解決手段】内部配線153上に絶縁膜156を形成する工程と、絶縁膜156に内部配線153に通じる開口157を形成する工程と、開口157が形成された絶縁膜156上に、銅膜101を形成する工程と、銅膜101上に、バンプ電極形成パターンに対応したマスク材102を形成する工程と、マスク材102をマスクに用いて、銅膜101を異方的にエッチングし、バンプ電極を形成する工程と、とを具備する。

(もっと読む)

半導体装置の製造方法

【課題】異方的にエッチングされた銅膜に、簡単で実用的にCuバリア膜を形成できる半導体装置の製造方法を提供すること。

【解決手段】Cuバリア膜100上に、銅膜101を形成する工程と、銅膜101上に、マスク材102を形成する工程と、マスク材102をマスクに用いて、銅膜101をCuバリア膜100が露出するまで異方的にエッチングする工程と、マスク材102を除去した後、異方的にエッチングされた銅膜101上に、銅膜101に対して触媒作用があり、Cuバリア膜100には触媒作用がない選択析出現象を利用した無電解めっき法を用いて、銅の拡散を抑制する物質を含むめっき膜104を形成する工程と、を具備する。

(もっと読む)

電子素子の製造方法および電子素子

【課題】有機絶縁層を有する電子素子の配線短絡を簡素な工程により絶縁することが可能な電子素子の製造方法および電子素子を提供する。

【解決手段】配線層21,22の上に有機絶縁層12を形成したのち、配線層21,22の短絡部23に、有機絶縁層12に対して透過性を持つ波長のレーザ光LBを有機絶縁層12を介して照射、または基板11に対して透過性を持つ波長のレーザ光LBを基板11を介して照射する。レーザ照射領域24では短絡部23が消失して、配線層21と配線層22との間の絶縁が回復する。短絡部23の上下に接する有機絶縁層12または基板11は残されている一方、レーザ照射領域24(短絡部23が消失した部分)には空洞25が生じる。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】MRAMにおいては、書き込み電流の低減やディスターブ回避を目的に、書き込みに使用する配線を強磁性体膜で覆うクラッド配線構造がよく用いられている。また、高信頼性製品の信頼性確保のためCu配線中に微量のAlを添加するCuAl配線が広く使用されている。MRAMも高信頼性製品に搭載される可能性が高く、信頼性は重要である。しかし、クラッド配線は、もともと配線抵抗が高いCuAl配線の配線抵抗を更に上昇させるというデメリットがあるため、両方の技術を同時に使用すると配線抵抗のスペックを満たさなくなる可能性が高い。

【解決手段】本願発明は、多層銅埋め込み配線を有する半導体装置において、MRAMメモリセルマトリクス領域を構成する複数の銅埋め込みクラッド配線の銅配線膜を比較的純粋な銅で構成し、これらの配線層よりも下層の銅埋め込み非クラッド配線の銅配線膜を、Alを添加したCuAl配線膜とするものである。

(もっと読む)

半導体デバイス

【課題】応力による半導体回路の特性劣化を抑制した半導体デバイスを提供する。

【解決手段】縦導体は、半導体基板の厚み方向に設けられた微細孔を満たし、第1結晶組織301と第2結晶組織302とを含むナノコンポジット結晶構造を有する。ナノコンポジット結晶構造において、第1結晶組織301及び第2結晶組織302の少なくとも一方は、ナノサイズである。

(もっと読む)

半導体装置

【課題】信号線の上面に微小な凹凸が形成されても、伝送線路の伝送特性が劣化することを抑制できるようにする。

【解決手段】信号線522は、多層配線層400及び再配線層500の第a層(a≧2)に形成されている。プレーン配線444は多層配線層400及び再配線層500の第b層(b<a)に形成されており、平面視で信号線522と重なっている。2つのコプレーナ配線524は多層配線層400及び再配線層500の第c層(b≦c≦a)に形成されており、平面視で信号線522と平行に延伸しており、かつ信号線522を挟んでいる。信号線522からプレーン配線444までの距離hは、信号線522からコプレーナ配線524までの距離wより短い。信号線522の上方のうち、信号線522からwと同じ高さの範囲内には、電源線、グランド線、及び他の信号線が位置していない。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】ビアに位置ずれが生じても、ビアがエアギャップにつながることを抑制できるようにする。

【解決手段】複数の配線240は例えばCu配線であり、互いに平行に延伸している。側壁絶縁膜212は、複数の配線240それぞれの側壁に形成されている。エアギャップは、複数の配線240それぞれの相互間に形成され、複数の側壁絶縁膜212の間に位置している。絶縁膜302は、複数の配線240上、複数の側壁絶縁膜212上、およびエアギャップ214上に形成されている。ビア344は絶縁膜302を貫通しており、いずれかの配線240に接続している。そして側壁絶縁膜212は、絶縁膜302がエッチングされる条件では絶縁膜302よりエッチングレートが低い材料により形成されている。

(もっと読む)

半導体装置及びその製造方法

【課題】絶縁膜の接続孔側壁の寸法制御を高精度に且つ低コストで行うことができる半導体装置を提供する。

【解決手段】半導体装置1は、基材10の主面を被覆し、下部電極11の上面に達する接続孔12hを有する絶縁膜12を備える。絶縁膜12の膜密度は、基材10の主面から絶縁膜12の厚み方向に離れるに従って低減する。接続孔12hの内径は、絶縁膜12の膜密度の低減に伴って拡大する。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】半導体装置の信頼性を向上させる。

【解決手段】複数のゲート電極3bを覆うように窒化シリコン膜(第1絶縁膜)5を形成した後、オゾンTEOS膜(第1酸化シリコン膜)6、プラズマTEOS膜(第2酸化シリコン膜)を順次積層する。ここで、オゾンTEOS膜6を積層後、プラズマTEOS膜を積層する前に、窒化シリコン膜5をCMPストッパ膜として、CMP法により研磨する。これにより、プラズマTEOS膜の膜厚を均一化させることができるので、半導体装置の信頼性を向上させることができる。

(もっと読む)

半導体装置の製造方法

【課題】金属マスクを形成する工程を含む半導体装置の製造方法において、金属片が支持基板に付着することを防止する。

【解決手段】この製造方法は、支持基板10の表面10aに貼付された半導体ウェハ12上にネガレジストを塗布し、該ネガレジストを露光することにより所定のパターンを有するレジスト18を形成するレジスト形成工程と、半導体ウェハ12上にメッキ処理を施すことにより金属マスク20を形成したのちレジスト18を除去する金属マスク形成工程と、金属マスク20を介して半導体ウェハ12にエッチングを施すことにより、貫通孔12dを形成するエッチング工程と、金属マスク20を除去したのち、貫通孔12dの内面及び半導体ウェハ12の裏面12bに金属膜26を形成する金属膜形成工程と、半導体ウェハ12を支持基板10から取り外す取外し工程とを含む。

(もっと読む)

半導体装置の製造方法

【課題】CMP法による研磨のばらつきを抑制できる半導体装置の製造方法を提供する。

【解決手段】ウェハ1の周辺領域2の第3層間絶縁膜に、ダミーパターン41を形成する。ダミーパターン41は、ウェハ1の接線及び法線に交差する斜パターン42と、斜パターン42に連結され、ウェハ1の周方向に延びる分離パターン43とを有する。配線溝に導電性材料を埋め込んだ後に、CMP法により余分な導電性材料を除去するときは、ダミーパターン41に形成された溝を通って研磨剤が分散されるので、導電性材料や第3層間絶縁膜の研磨量が均一になる。

(もっと読む)

半導体装置及び製造方法

【課題】 ビアホール上にオーミック電極が形成された半導体装置において、装置の小型化を図ること。

【解決手段】 本半導体装置は、基板10と、基板10上に形成された半導体層12と、半導体層上12に形成されたソースまたはドレイン電極を構成するオーミック電極20と、を備え、基板10及び半導体層12には、基板10及び半導体層12を貫通するビアホール30が形成され、ビアホール30は、少なくとも半導体層を貫通する第1ビアホール32と、第1ビアホール32下の基板10に形成された、第1ビアホール32より開口断面積が大きい第2ビアホール34と、を含み、オーミック電極20は、第1ビアホール32の上に設けられている。

(もっと読む)

半導体装置及びその製造方法

【課題】パッシベーション膜にクラックを生じさせるか否かを容易に判定できる構造を有する半導体装置を提供する。

【解決手段】半導体装置1は、下部電極23の上面に達する接続孔30hを持つパッシベーション膜30を備える。パッシベーション膜30は、接続孔30hを除いて下部電極23の周縁部を含む領域を被覆する。下部バリアメタル膜31は、下部電極23とパッシベーション膜30の凸状部分30bとを被覆するように形成されている。バンプ電極35から離れた領域でパッシベーション膜30に形成されている段差部分を被覆するように金属膜パターン31Tが形成されている。

(もっと読む)

半導体装置及びその製造方法

【課題】配線間の実効的な容量の増加を抑制する。

【解決手段】半導体装置100は、6員環構造の環状シロキサンを原料とする絶縁膜11と、絶縁膜11に形成された配線溝12と、配線溝12に金属膜(配線メタル)15が埋め込まれて構成される配線10と、を有する。半導体装置100では、配線溝12の底面において、絶縁膜11の内部よりも単位体積あたりの炭素原子数、又は/及び、窒素原子数が多い改質層13が形成されている。

(もっと読む)

半導体装置の製造方法

【課題】ビアを形成するとともに配線を形成する半導体装置の製造方法を提供する。

【解決手段】実施の形態の半導体装置の製造方法は、まず、第1のパターンを導電体上に形成された被加工材に転写することにより、第1のパターンを有する第1の溝を被加工材の上部に形成する工程を行い。次に、第1のパターンと一部が重なる第2のパターンを被加工材に転写することにより、第1および第2のパターンの和集合からなるパターンを有する第2の溝を被加工材の上部に形成し、第1および第2のパターンの積集合からなるパターンを有し、底部に導電体が露出する孔を被加工材の第2の溝の下に形成する工程を行い。孔内にビアを形成し、第2の溝内に配線を形成する工程を行う、ことを含む。

(もっと読む)

161 - 180 / 1,413

[ Back to top ]