Fターム[5F033PP33]の内容

半導体集積回路装置の内部配線 (234,551) | 導電膜の成膜方法 (14,896) | 同一膜を2段階以上で成長させるもの (600)

Fターム[5F033PP33]に分類される特許

161 - 180 / 600

半導体装置およびその製造方法

【解決手段】 本発明による半導体装置は、メタル抵抗素子の下面に形成された下面酸化防止絶縁膜と、上面に形成された上面酸化防止絶縁膜と、下面酸化防止絶縁膜及び上面酸化防止絶縁膜とは別工程で、ウェハ全面に堆積した後に異方性エッチングを施しメタル抵抗素子の側面近傍にのみ形成された側面酸化防止絶縁膜とを有する。

【効果】 本発明によれば、メタル抵抗素子が酸化されて抵抗値が上昇するのを防止することができると同時に、加工プロセスを複雑にすることなく金属配線層間の寄生容量の増大を防止することができる。

(もっと読む)

半導体装置の製造方法

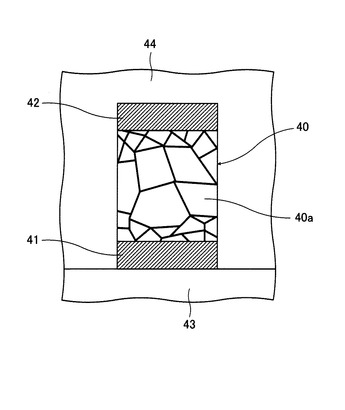

【課題】配線のエレクトロマイグレーション耐性を向上させる。

【解決手段】Al配線40を形成する際、バリアメタル41上に、Al粒子40aが第1の平均粒径となるように第1の条件で第1のAl膜を形成し、次いで、第1の平均粒径より小さい第2の平均粒径となるように第2の条件で第2のAl膜を形成する。その後、第2のAl膜上にバリアメタル42を形成し、形成後、バリアメタル41,42および第1,第2のAl膜を配線パターンに加工する。

【選択図】図9  (もっと読む)

(もっと読む)

半導体装置

【課題】細幅配線間のTDDB寿命の低下、および細幅配線間のショートによる歩留まり低下を抑制する半導体装置を提供する。

【解決手段】半導体装置10は、ダマシン配線からなる配線層を有し、0.5μm以上の幅を有する第1の配線12と、前記第1の配線12に隣接し前記第1の配線12から0.5μm未満の間隔で配置された第2の配線14と、前記第2の配線14に隣接し前記第1の配線12から0.5μm以下の間隔で配置された第3の配線16と、を備え、前記第2および第3の配線は同電位を有するよう構成されている。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】貫通電極構造を有する半導体装置において、半導体基板と裏面配線との間に形成される絶縁膜の信頼性を向上させることにより、高品質の半導体装置を提供する。

【解決手段】

その表面に表面電極が形成された半導体基板の裏面にシリコン酸化膜とシリコン窒化膜とからなる積層絶縁膜を形成する。半導体基板の裏面側から積層絶縁膜および半導体基板をエッチングして表面電極に達する貫通孔を形成する。貫通孔の側壁および底面と積層絶縁膜を覆う絶縁膜を形成した後、この絶縁膜を部分的にエッチングして貫通孔の底面において表面電極を露出させるとともに貫通孔側壁の絶縁膜を残す。その後、貫通孔の内部を充たし且つ積層絶縁膜を覆う導電膜を形成して貫通孔内部に表面電極に接続された貫通電極を形成するとともに、積層絶縁膜上に裏面配線を形成する。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】Low−k膜の機械的強度を向上させることができる半導体装置の製造方法、およびそれにより得られる半導体装置を提供する。

【解決手段】半導体基板SB上に、SiOCを含有する骨格構造部と、炭化水素化合物を含有する空孔形成材料部とを有するSiOC膜である層間絶縁膜3が形成される。層間絶縁膜3に200nm以上260nm以下の波長を有する光が照射される。

(もっと読む)

半導体装置

【課題】ボンディングする際に、電極パッドの下方に加わるストレスに対しての耐性が強く、且つ配線の配置が容易な半導体装置を提供する。

【解決手段】半導体基板1上に形成された多層配線層2を貫通し半導体基板1に達する支柱5a,5bにより、多層配線層2上に形成される電極パッド4の4隅のうち、少なくとも隣接する2隅を下方から支え、支柱5a,5b間に複数の梁6a,6b,6cを接続し、梁6a,6b間に部材7a,7b,7c,7dを接続する。

(もっと読む)

半導体装置およびその製造方法

【課題】配線抵抗およびビア抵抗のばらつきを配線層全体として抑制できる半導体装置およびその製造方法を提供する。

【解決手段】ビア深さBDEの深い第1のビアホールVH内の導電層(配線層IL2)と配線層IL1との接触部の抵抗は、ビア深さBDEの浅い第2のビアホールVH内の導電層(配線層IL2)と配線層IL1との接触部の抵抗よりも小さくなっている。

(もっと読む)

半導体装置及びその製造方法

【課題】貫通電極と導電パターンの間で接続不良が生じることを抑制できる半導体装置を提供する。

【解決手段】この半導体装置は、基板100、層間絶縁膜260、導電パターンの一例である配線342、貫通電極440、及び接続端子の一例であるバンプ900を備える。層間絶縁膜260は、基板100の表面より上に位置している。配線342は、第1の層間絶縁膜260の表面に位置している。貫通電極440は、基板100の裏面から層間絶縁膜260の表面まで貫通しており、一端が配線342に接続している。バンプ900は基板100の裏面側に設けられ、貫通電極440の他端に接続している。

(もっと読む)

半導体装置及び半導体装置の製造方法

【目的】Cu配線上に形成されるCuとSiとを含有する化合物膜の余剰SiがCu配線中へと拡散することを防止した半導体装置を提供することを目的とする。

【構成】本発明の一態様の半導体装置は、SiとOとが他より多く含まれる領域を有するCu配線となるCu膜260,262と、Cu膜260,262上に選択的に形成された、CuとSiとを含有する選択キャップ膜280と、Cu膜260,262の側面側に形成された層間絶縁膜220と、を備えたことを特徴とする。

(もっと読む)

半導体装置及びその製造方法

【課題】Cuを含む配線について、配線抵抗を低く維持しつつ、しかも、ストレスマイグレーション耐性の劣化を伴うことなく、エレクトロマイグレーション耐性を向上し得る半導体装置及びその製造方法を提供する。

【解決手段】半導体基板10の上方に形成された層間絶縁膜36と、層間絶縁膜36内に形成されたCuより成る配線50と、層間絶縁膜36と配線50の間に形成され、Ti膜42とTa膜44との積層膜より成るバリアメタル膜46とを有し、配線50表面に、TiとSiとを含む界面層54が形成されている。

(もっと読む)

半導体装置の製造方法

【課題】配線用上部金属層の接続パッド部上面に柱状電極を電解メッキにより形成するためのドライフィルムレジストをラミネートするとき、配線用上部金属層間への気泡の発生を防止した半導体装置の製造方法を提供する。

【解決手段】半導体ウエハ21上の全面に形成された下地金属層8の上面周辺部にリング状のレジスト高さ位置規制部27が形成され、下地金属層の上面には配線用上部金属層9が形成されている。そして、ウエハステージ31の凹部32内に半導体ウエハを上部金属層およびレジスト高さ位置規制部の上面がウエハステージの凹部の周囲における上面と面一となるように配置する。次に、ウエハステージ、上部金属層およびレジスト高さ位置規制部の上面にドライフィルムレジスト33をラミネートする。この状態で、ドライフィルムレジストと下地金属層との間に空間35が形成されており、配線用上部金属層間の気泡の発生を防止することができる。

(もっと読む)

半導体装置の製造方法

【課題】絶縁膜に形成された孔に対するタングステン膜の埋め込み性を向上させ、タングステン膜の結晶粒を大きくすることができ、かつ生産性を向上させることができる半導体装置の製造方法を提供する。

【解決手段】絶縁膜に孔を成膜する(S10)。次いで、半導体基板を330℃以上400℃以下に加熱して(S20)、B2H6ガス及びSiH4ガスの少なくとも一方、並びにタングステン含有ガスを反応室内に導入することにより、第1のタングステン膜を成膜する(S30)。次いで、反応室内にH2ガス及び不活性ガスの少なくとも一方を導入し、かつ30秒以上の時間をかけて半導体基板を370℃以上410℃以下に昇温して(S40)、タングステン含有ガスを反応室内に導入することにより、第1のタングステン膜上に第2のタングステン膜を成膜する(S50)。

(もっと読む)

銅表面上への選択的コバルト堆積

本発明の実施形態は、露出誘電表面を覆う銅表面上にコバルト層を選択的に形成するプロセスを提供する。一実施形態では、前処理プロセスの間に金属銅表面を形成している間は処理チャンバー内の基板の汚染された銅表面を還元剤にさらすステップと、気相堆積プロセスの間に基板上の誘電表面を露出したままにしながら金属銅表面を覆ってまたは上にコバルトキャッピング層を選択的に形成するために基板をコバルト前駆体ガスにさらすステップと、コバルトキャッピング層および誘電表面を覆ってまたは上に誘電障壁層を堆積させるステップとを包含する、基板上の銅表面をキャッピングするための方法が、提供される。別の実施形態では、堆積−処理サイクルは、気相堆積プロセスを実行した後に後処理プロセスを実行するステップを包含し、その堆積−処理サイクルは、複数のコバルトキャッピング層を形成するために繰り返されてもよい。  (もっと読む)

(もっと読む)

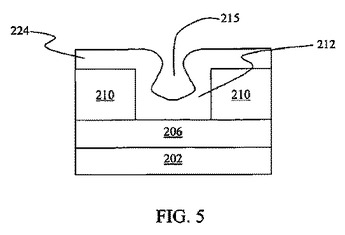

相変化メモリデバイスに電極を形成する気相法

サブリソグラフィック寸法又は高アスペクト比を含む小寸法を有する開口内に均一で均質に電極材料を形成する方法を提供する。この方法は、内側に形成された開口を有する絶縁層を提供し、開口上及び開口内に均質な導電又は準抵抗材料を形成するステップを含んでいる。この方法は、金属窒化物、金属アルミニウム窒化物及び金属ケイ素窒化物電極組成を形成するCLD又はALDプロセスである。この方法は、アルキル、アリル、アルケン、アルキン、アシル、アミド、アミン、イミン、イミド、アジド、ヒドラジン、シリル、アルキルシリル、シリルアミン、キレーティング、ヒドリド、サイクリック、カルボサイクリック、シクロペンタジエニル、ホスフィン、カルボニル又はハライドから選択された1以上のリガンドを含む金属前駆体を利用する。公的な前駆体は、一般式MRnを有し、Mは金属、Rは上述のリガンド、nは主要な金属原子に結合したリガンドの数に対応している。Mは、Ti、Ta、W、Nb、Mo、Pr、Cr、Co、Ni又は他の遷移金属である。  (もっと読む)

(もっと読む)

金属膜パターンの製造方法

【課題】金属微粒子分散体の基板への塗布と加熱処理による焼結とにより基板上に形成される金属膜からなる金属膜パターンの焼結性を向上させ、さらに金属膜パターンと基板との密着性を向上させることができる金属膜パターンの製造方法を提供する。

【解決手段】基板表面上に金属微粒子分散体を塗布する工程と、前記金属微粒子分散体を乾燥して金属膜前駆体を形成する工程と、前記金属膜前駆体にエネルギー線を照射して金属膜化領域を形成する工程と、誘導加熱法による加熱により前記金属膜化領域の近傍の前記金属膜前駆体をさらに金属膜化する工程と前記金属膜前駆体を除去する工程とからなる。

(もっと読む)

半導体装置及びその製造方法

【課題】 銅元素の半導体基板方向への拡散及び隣接した配線層間のリーク電流を抑制した半導体装置及びその製造方法を提供する。

【解決手段】 第一の絶縁膜と、第一の絶縁膜中に形成されたコンタクトプラグと、第一の絶縁膜上に形成されたリーク電流抑制層と、リーク電流抑制層上にリーク電流抑制層と積層構造をなすように形成された拡散抑制層と、拡散抑制層上に形成された第二の絶縁膜と、コンタクトプラグ上に形成される銅配線層と、を備えることを特徴とする半導体装置。

(もっと読む)

半導体装置及び半導体装置の製造方法

【目的】コンタクトプラグ材料の基板への拡散を抑制する半導体装置及び半導体装置の製造方法を提供することを目的とする。

【構成】本発明の一態様の半導体装置は、半導体基板200と導通するコンタクトプラグとなるCu膜260と、Cu膜260の少なくとも底面側に、半導体基板200と接触して配置された柱状結晶構造をもつTiN膜242と、Cu膜260の少なくとも底面側に、TiN膜242と接触して配置された、TiNのアモルファス膜244と、Cu膜260の底面側と側面側に、少なくとも一部がアモルファス膜244とCu膜260とに接触して配置された、TiN膜242材と同じ材料で柱状結晶構造をもつTiN膜246と、Cu膜260の側面側に配置されたSiO2膜220と、を備えたことを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の異なる回路領域にそれぞれの要求特性を満足する配線を形成する。

【解決手段】所定基板上に配線の主要部を構成する第1の金属膜を形成し(ステップS1)、その上にエレクトロマイグレーション耐性向上に寄与するTi,Zr等の不純物元素を含む第2の金属膜を形成する(ステップS2)。次いで、不純物元素を添加すべき配線の形成領域にある第2の金属膜は残し、不純物元素の添加が不要な配線の形成領域にある第2の金属膜を部分的に除去する(ステップS3)。その後、熱処理により、残る第2の金属膜の不純物元素を下の第1の金属膜に拡散させる(ステップS4)。これにより、不純物元素濃度の異なる第1の金属膜を基板上に形成できる。これを用いて配線を形成することにより、異なる領域にそれぞれに適した配線を形成することが可能になる。

(もっと読む)

密着性に優れた銅合金複合膜の成膜方法およびこの成膜方法で使用するCa含有銅合金ターゲット

【課題】密着性に優れた銅合金複合膜の成膜方法を提供する。

【解決手段】Ca:0.06〜14モル%を含有し、残部がCuおよび不可避不純物からなる成分組成を有するCa含有銅合金ターゲットを用い、酸素:1〜20体積%を含む不活性ガス雰囲気中でスパッタすることによりCa:0.01〜2モル%、酸素:1〜20モル%を含有し、残部がCuおよび不可避不純物からなる成分組成を有する酸素−Ca含有銅合金下地膜を成膜し、引き続いて酸素の供給を停止してスパッタ雰囲気を不活性ガス雰囲気とし、この不活性ガス雰囲気中でスパッタすることによりCa:0.01〜2モル%を含有し、残部がCuおよび不可避不純物からなる成分組成を有するCa含有銅合金導電膜を成膜することを特徴とする。

(もっと読む)

半導体装置およびその製造方法

【課題】 渦巻き形状の薄膜誘導素子を備えたCSPと呼ばれる半導体装置において、シリコン基板に発生する渦電流に起因する薄膜誘導素子の渦電流損を低減する。

【解決手段】 シリコン基板1と薄膜誘導素子9との間には低誘電率膜5が設けられている。これにより、シリコン基板1に発生する渦電流に起因する薄膜誘導素子9の渦電流損を低減することができる。

(もっと読む)

161 - 180 / 600

[ Back to top ]