Fターム[5F033PP33]の内容

半導体集積回路装置の内部配線 (234,551) | 導電膜の成膜方法 (14,896) | 同一膜を2段階以上で成長させるもの (600)

Fターム[5F033PP33]に分類される特許

121 - 140 / 600

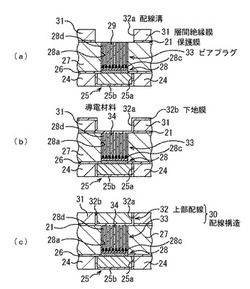

配線構造及びその形成方法、並びに半導体装置

【課題】炭素元素からなる線状構造体を有する接続部の更なる低抵抗化を実現して、更なる接続部の微細化を可能とする。

【解決手段】ビア孔28a内を充填し、配線溝32aの内壁面を覆うように、例えば超臨界CVD法により、ビア孔28a内におけるCNT28d間の空隙及びCNT28dの中空内を導電材料34で埋め込み、ビアプラグ33と、ビアプラグ33上で配線溝32aの内壁面を覆う下地膜32bとを同時形成する。

(もっと読む)

半導体装置の製造方法

【課題】デュアルダマシン法による解像限界以下の溝(トレンチ)及び凹部(孔又はビア)のパターンをCD値を高精度に形成することができる半導体装置の製造方法を提供する。

【解決手段】被エッチング層上に、第1のハードマスク膜と、第2のハードマスク膜とを成膜する成膜工程S11と、第1のピッチを有し、第2のハードマスク膜よりなるパターンであって、溝のパターンを形成する際のエッチングマスクとなる溝形成用マスクパターンを形成するための第1の溝形成用マスクパターン形成工程S12〜S14と、第4のピッチで設けられた開口部を有する第2のレジスト膜と、第2のレジスト膜の開口部と連通し、第2のレジスト膜の開口部の寸法より小さい寸法の開口部を有する第1の有機膜とよりなる第2レジストパターンを用いて、第1のハードマスク膜をエッチングする第1の凹部形成用マスクパターン形成工程S15〜S18とを有することを特徴とする。

(もっと読む)

薄膜多層配線基板およびその製造方法

【課題】 剥離の発生の少ない薄膜多層配線基板とその製造方法を提案する。

【解決手段】 少なくとも一つの前記配線層が、下層の配線層上に形成された第一のSiO2薄膜と、前記第一のSiO2薄膜上に形成されたSiON薄膜と、前記SiON薄膜上に形成された第二のSiO2薄膜と、前記第二のSiO2薄膜に埋め込まれて形成された配線導体と、前記配線導体と接続しかつ前記第一のSiO2薄膜、前記SiON薄膜および前記第二のSiO2薄膜を貫通して前記下層の配線層の配線導体と電気的に接続するビア導体と、前記第二のSiO2薄膜上に形成されたSiN薄膜と、で構成されている。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】パッケージサイズの拡大や製造プロセスを変更せずにSOI基板のシリコン基板層の電位固定を行うことができる半導体装置および半導体装置の製造方法を提供する。

【解決手段】半導体基板層11の表面からSOI基板10をエッチングし、電極パッド16に達する第1のトレンチおよび半導体基板層11内部で終端している第2のトレンチを形成する工程と、半導体基板層の表面および各トレンチを覆うように絶縁膜19を形成する工程と、各トレンチ底面の絶縁膜19を除去して電極パッド16および半導体基板層11を露出させる工程と、半導体基板層11の表面上と各トレンチの側壁および底面に導電膜31〜33を形成して貫通電極30を形成するとともに、コンタクト部50を形成する工程と、半導体基板層11上の導電膜にパターニングを施して外部電極43およびコンタクト部50に電気的に接続された電位固定用の外部電極43aを形成する工程と、を含む。

(もっと読む)

窒化チタン障壁層の形成方法及び窒化チタン障壁層を含む半導体デバイス

【課題】追従性が高く良好なステップ・カバレージ及び低い抵抗率を有する窒化チタン障壁層を形成する方法を提供する。

【解決手段】部分的に製作された電子デバイスに窒化チタン障壁層を形成する方法であって、前記部分的に製作された電子デバイスの上に第1の温度で、第1の抵抗率を有する第1の窒化チタンサブレーヤ40を堆積させる工程と、前記第1の窒化チタンサブレーヤの上に第2の温度で、第2の抵抗率を有する第2の窒化チタンサブレーヤ42を堆積させる工程とを備えており、前記第2の温度は前記第1の温度よりも高く、第2の抵抗率は第1の抵抗率よりも低いことを特徴とする窒化チタン障壁層の形成方法。

(もっと読む)

貫通電極基板及びその製造方法、並びに貫通電極基板を用いた半導体装置

【課題】基板の表裏を導通する導通部における電流損失を低減した貫通電極基板及びそれを用いた半導体装置を提供すること。

【解決手段】本発明の貫通電極基板100は、表裏を貫通する貫通孔104を有する基板102と、貫通孔104内に充填される金属材料を含む導通部106と、を備え、導通部106の金属材料は、結晶粒径が29μm以上の結晶粒を含む。また、導通部106の金属材料は、面積重み付けした平均結晶粒径が13μm以上である。

(もっと読む)

スパッタ成膜方法及びプラズマ処理装置

【課題】ホールやトレンチなどの凹部を被覆する膜のカバレッジ性を向上し、かつ、平坦な表面をもつ膜を成膜することが可能なスパッタ成膜方法を提供する。

【解決手段】チャンバ201内で、金属ターゲットに高周波電力及び直流電圧を印加して、プラズマを発生させるとともにターゲット粒子をイオン化させて金属イオンを発生させる。チャンバ201内のステージホルダ302上に載置された、表面に凹部を有する基板306へ、金属イオンを照射して薄膜を形成する。この際、まず初めに、5乃至15Paの圧力下でスパッタ成膜を行うことにより第1の層を形成し、次いで、0.5乃至5Paの圧力下でスパッタ成膜を行うことにより第1の層上に第2の層を形成する。

(もっと読む)

半導体装置

【課題】配線層を薄くした場合にも電極パッド形成領域で配線層がなくなることを確実に防止できるようにし、配線層と電極パッドとを安定して電気的に接続させる。

【解決手段】半導体基板1上の第4層間絶縁膜10中に複数のコンタクト用配線11Bが形成されている。各コンタクト用配線11Bの上及び第4層間絶縁膜10の上に第1保護絶縁膜12が形成されており、第1保護絶縁膜12には、各コンタクト用配線11Bを露出させる第1開口部12aが形成されている。第1開口部12aの内部にはバリアメタル膜13を介して、コンタクト用配線11Bと電気的に接続する電極パッド14が形成されている。第1開口部12aの下側には、コンタクト用配線11Bが配置されていない領域が存在している。

(もっと読む)

パターン形成方法、デバイスおよび電子機器

【課題】幅が細く、かつ厚さが均一な断面形状を有するパターン形成方法、デバイスおよび電子機器を提供する。

【解決手段】本発明のパターン形成方法は、基板を所定の温度に加熱する第1の工程と、基板を所定の温度に保持しつつ、パターン形成材料を分散または溶解させた液体材料を基板上に滴下し、乾燥させる第2の工程と、液体材料を所定の温度の基板に滴下させたときの蒸発速度よりも蒸発速度を遅くさせる第3の工程と、液体材料が乾燥してなる乾燥体上に、液体材料を滴下する第4の工程とを有する。

(もっと読む)

半導体装置の製造方法

【課題】Cu配線中のMnの残留量を減らすことができる、半導体装置の製造方法を提供する。

【解決手段】Cu層20の形成後、Cu層20上に、高純度Cuからなる犠牲層31が積層される。そして、犠牲層31の形成後、熱処理により、Cu層20と第2絶縁層6との間に、MnSiOからなる第2バリア膜13が形成される。このとき、第2バリア膜13の形成に寄与しない余剰のMnは、Cu層20中に拡散する。Cu層20上に高純度Cuからなる犠牲層31が積層されているので、Cu層20に拡散したMnの一部は、Cu層20中を犠牲層31に引き寄せられるように移動し、犠牲層31に拡散する。この犠牲層31へのMnの拡散により、Cu層20に含まれるMnの量が減少する。よって、Cu層20からなる第2Cu配線中のMnの残留量を減らすことができる。

(もっと読む)

ダメージフリー被覆刻設堆積法

【課題】周辺表面を汚染もしくは乱さずに、スパッタリングした銅シード層を堆積させて、所望の形状に刻設する方法を提供する。

【解決手段】底部516と、側壁514と、上側開口526とを有する複数の凹状のデバイス特徴を含む基板上に銅シード層を堆積させる方法であって、a)基板表面からのスパッタリングを引き起こす態様において前記凹状のデバイス特徴の基板表面に衝突することなく前記銅シード層の第1の部分を前記基板上にスパッタ堆積するステップと、b)前記銅シード層の第2の部分を前記基板上にスパッタ堆積すると同時に、銅シード層の前記第1の部分の少なくとも一部を、前記複数の凹状のデバイス特徴のそれぞれの底部から対応する側壁へと再配分するステップと、を備える。

(もっと読む)

半導体装置の製造方法

【課題】凹部の側壁部側からのめっきの成長を抑制して、ボイドの発生を低減することができる半導体装置の製造方法を提供する。

【解決手段】本発明の一の態様によれば、表面に凹部1aを有するウェハWの少なくとも凹部1aの底部1bおよび側壁部1cに、シード膜3を形成する工程と、シード膜3上に、少なくとも凹部1aの底部1bに位置するシード膜3の部分3aが露出しかつ凹部1aの側壁部1cに位置するシード膜3の部分3bを覆うようにめっき抑制膜4を形成する工程と、シード膜3に電流を供給して、めっき抑制膜4の形成された凹部1aに埋め込まれるように電解めっき法によりめっき膜5を形成する工程と、めっき膜5に熱処理を施す工程とを備え、めっき抑制膜4が、シード膜3の構成材料より抵抗率が高くかつめっき膜5の構成材料と異なる材料から構成されることを特徴とする、半導体装置の製造方法が提供される。

(もっと読む)

半導体装置およびその製造方法

【課題】信頼性の高い微細化された配線構造を有する半導体装置、およびその製造方法を提供する。

【解決手段】本発明の実施の形態による半導体装置は、半導体基板上に形成された被接続部と、前記被接続部の上層に形成された所定の開口パターンを有する絶縁膜と、前記絶縁膜上に形成された所定の配線パターンを有する配線と、前記所定の開口パターンと前記所定の配線パターンとの論理積からなるパターンに含まれるパターンを有し、前記被接続部と前記配線とを接続するビアと、を含む。

(もっと読む)

集積回路装置

【課題】能動素子用の基板と受動素子用の基板とを接続した集積回路装置において、重ね合わせ精度の要求緩和、素子形成領域の有効活用等を可能とする。

【解決手段】集積回路装置100は、第1基板51と第2基板31とを備える。第1基板51は半導体基板からなり、第1基板51における一方の面に能動素子部52が形成されると共に、能動素子部52に電気的に接続され且つ第1基板51を貫通する第1貫通電極57が形成されている。第2基板31における一方の面にスパイラルインダクタ33等の受動素子が形成されると共に、スパイラルインダクタ33等の受動素子に電気的に接続され且つ第2基板31を貫通する第2貫通電極37が形成されている。第1基板51における他方の面と、第2基板31における他方の面とが対向するように配置され、第1貫通電極57と、第2貫通電極37とが電気的に接続されている。

(もっと読む)

半導体装置およびその製造方法

【課題】 CSPと呼ばれる半導体装置において、配線相互間で銅イオンマイグレーションによるショートが発生しにくいようにし、且つ、配線用の下地金属層を良好に形成する。

【解決手段】 配線7の銅からなる上部金属層9の表面にはポリイミド系樹脂等からなる第2の保護膜10が設けられている。これにより、配線7相互間で銅イオンマイグレーションによるショートが発生しにくいようにすることができる。また、第1の保護膜5の平坦な上面に下地金属層8を形成しているので、配線7用の下地金属層8を良好に形成することができる。

(もっと読む)

半導体装置とその製造方法

【課題】半導体装置とその製造方法において、強誘電体膜を備えたキャパシタの劣化を防止すること。

【解決手段】シリコン基板30の上方に、下部電極61、強誘電体膜よりなるキャパシタ誘電体膜62と、上部電極63とを有するキャパシタQを形成する工程と、キャパシタQ上に層間絶縁膜71を形成する工程と、層間絶縁膜71に、上部電極63に達するホール59aを形成する工程と、ホール59aの内面、及びホール59aから露出する上部電極63の表面に第1のバリア膜67を形成する工程と、第1のバリア膜67上に、第1のバリア膜67よりも酸素濃度が高い第2のバリア膜68を形成する工程と、第2のバリア膜68の上方に導電膜74を形成して、ホール59aを埋め込む工程とを含む半導体装置の製造方法による。

(もっと読む)

半導体装置の製造方法

【課題】 CSPと呼ばれる半導体装置において、封止膜が配線の表面および柱状電極の外周面から剥離しにくいようにし、且つ、配線間でショートが発生しにくいようにする。

【解決手段】 銅からなる配線7の表面および銅からなる柱状電極10の外周面には針状構造の酸化銅膜11が設けられている。これにより、酸化銅膜11が無い場合と比較して、エポキシ系樹脂等からなる封止膜12が配線7の表面および柱状電極10の外周面から剥離しにくいようにすることができる。また、酸化銅膜11を形成する前に、配線7下以外の領域における導電性を有する変質層Cを完全に除去することにより、変質層Cに起因する配線7間でのショートの発生を確実に防止することができる。

(もっと読む)

半導体装置の製造方法

【課題】溝の側面に対する合金膜の付着性(サイドカバレッジ)を向上させることができる、半導体装置の製造方法を提供する。

【解決手段】合金膜18は、バイアススパッタ法により形成される。そして、そのバイアススパッタ法による合金膜18の形成時には、第2溝11およびビアホール12の内面に向けて飛散するスパッタ粒子のエネルギーにより、第2溝11およびビアホール12の底面に付着しているスパッタ粒子が弾き飛ばされ、その弾き飛ばされたスパッタ粒子が第2溝11およびビアホール12の側面に再付着(リスパッタ)するように、スパッタ粒子を加速するためのRFバイアスが設定される。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】W−CSPの製造工程の前段階として行われる半導体基板の電気検査において電極パッド表面に比較的大きなプローブ痕が形成された場合でも高い信頼性を確保することができる半導体装置および半導体装置の製造方法を提供する。

【解決手段】半導体装置は、表面に少なくとも1つの電極パッドが形成された半導体基板と、電極パッドに接続された再配線層と、半導体基板を封止する封止部とを含む。電極パッドは再配線層との接続部を有する第1領域と、半導体基板の検査工程で検査プローブが当接される第2領域とからなる。半導体装置は、半導体基板上に電極パッドを覆う絶縁膜を形成する工程と、絶縁膜に開口部を形成し、開口部において電極パッドの第1領域を露出させる工程と、絶縁膜の開口部において露出した電極パッドに接続され、且つ電極パッドの第2領域の上方を覆う再配線層を絶縁膜上に形成する工程と、樹脂を用いて絶縁膜および再配線層を覆うように樹脂封止部を形成する工程と、を経て製造される。

(もっと読む)

半導体装置の製造方法

【課題】溝を埋め尽くすように形成されるCu層中のMnの残留量の増加を生じることなく、溝の側面上における合金膜の膜剥がれの発生を防止することができる、半導体装置の製造方法を提供する。

【解決手段】SiおよびOを含む絶縁材料からなる第2絶縁層6に、第2溝11が形成される。次に、スパッタ法により、第2溝11の内面に、CuMn合金からなる合金膜18が被着される。この合金膜18は、第2溝11の内面に接する部分のMn濃度が相対的に高く、その表層部分のMn濃度が相対的に低くなるように形成される。次いで、合金膜18上に、Cuからなる第2配線14が形成される。第2配線14の形成後、熱処理により、第2配線と第2絶縁層6との間に、MnSiOからなる第2バリア膜13が形成される。

(もっと読む)

121 - 140 / 600

[ Back to top ]