Fターム[5F033PP33]の内容

半導体集積回路装置の内部配線 (234,551) | 導電膜の成膜方法 (14,896) | 同一膜を2段階以上で成長させるもの (600)

Fターム[5F033PP33]に分類される特許

61 - 80 / 600

半導体装置及びその製造方法

【課題】下層の金属配線のダメージがなく上層の金属配線が形成され、かつ、配線間の寄生容量が低減された半導体装置及びその製造方法を提供する。

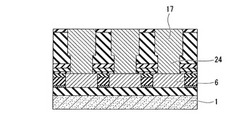

【解決手段】本発明に係る半導体装置は、半導体基板上に設けられた第1の金属配線層と、

前記第1の金属配線層上に設けられ、該第1の金属配線層の金属の拡散を防止する拡散防止膜と、前記拡散防止膜上に設けられた第1の絶縁膜と、前記第1の絶縁膜上に設けられた、前記拡散防止膜と同じ材料からなる第2の絶縁膜と、前記第2の絶縁膜上に設けられた第3の絶縁膜と、前記拡散防止膜、前記第1の絶縁膜、前記第2の絶縁膜及び前記第3の絶縁膜に形成された接続孔に充填され、前記第1の金属配線層に電気的に接続された第2の金属配線層と、を備えたことを特徴とする。

(もっと読む)

半導体装置およびその製造方法ならびに半導体ウエハ

【課題】ダイシングブレードの寿命を延ばすことができるとともに、半導体装置のエッジ部へのダメージを低減できる半導体装置を提供する。

【解決手段】機能素子領域2においては、第3層間絶縁膜27表面とパッシベーション膜33との間には、下配線25に接続される上配線29およびキャップメタル層32が形成されている。下配線25はCu以外の配線材料からなり、上配線29はCuからなる。このキャップメタル層32におけるパッシベーション膜33のパッド開口34から露出した部分が第1パッド6である。一方、スクライブ領域3においては、第3層間絶縁膜27表面とパッシベーション膜33との間には、下配線25に接続されるキャップメタル層32が形成されている。このキャップメタル層32におけるパッシベーション膜33のパッド開口44から露出した部分が第2パッド10である。

(もっと読む)

アモルファスシリコン膜の成膜方法および成膜装置

【課題】 表面ラフネスの精度をさらに改善でき、進展するコンタクトホールやラインなどの微細化に対応可能なアモルファスシリコンの成膜方法を提供すること。

【解決手段】 下地2を加熱し、加熱した下地2にアミノシラン系ガスを流し、下地2の表面にシード層3を形成する工程と、下地2を加熱し、加熱した下地2の表面のシード層3にアミノ基を含まないシラン系ガスを供給し、アミノ基を含まないシラン系ガスを熱分解させることで、シード層3上にアモルファスシリコン膜を形成する工程と、を備える。

(もっと読む)

半導体装置の製造方法及び半導体装置の製造装置

【課題】バリアメタル層を有する半導体装置を製造するに際し、パーティクルの発生を抑制可能な製造方法、及びこの製造方法を用いる半導体装置の製造装置を提供する。

【解決手段】

2つの金属層の間に金属化合物層が挟まれてなるバリアメタル層を有する半導体装置を製造するに際し、チタン及びタンタルのいずれか一方の金属元素から構成されるターゲットを希ガスの雰囲気でスパッタして、複数の金属層を下地配線上に積層する過程において最下層となる第1金属層に酸化処理を施す。次いで、最下層となる第1金属層の表面に第1金属酸化物層を形成した後に、層間において構成元素が異なるように、一つ以上の金属層を含む下地の表面に対して酸化処理、窒化処理、及び酸窒化処理のいずれかの処理を施す。こうした処理より第2金属化合物層を形成する。上記金属化合物層は、金属酸化物層の他、金属窒化物層や金属酸窒化物層であってもよい。

(もっと読む)

半導体装置

【課題】半導体装置の性能を向上させる。また、半導体装置の信頼性を確保する。また、半導体装置のチップサイズの縮小を図る。特に、SOI基板上に形成されたMOSFETを有する半導体装置の信頼性を損なわずにゲート電極の下部のウエルの電位を制御し、寄生容量の発生を防ぐ。また、MOSFETにおける欠陥の発生を防ぐ。

【解決手段】ゲート電極配線3に形成された孔部27内を通るウエルコンタクトプラグ8により、ゲート電極2の下部のウエルの電位を制御することで寄生容量の発生を防ぐ。また、ゲート電極2に沿って素子分離領域4を延在させることで、ゲッタリング効果によりゲート絶縁膜における欠陥の発生を防ぐ。

(もっと読む)

半導体装置の製造方法及び成膜装置

【課題】バリアメタル膜の酸化を十分に抑制することができる半導体装置の製造方法及び成膜装置を提供する。

【解決手段】基板1の上方に導電膜5を形成し、導電膜5を覆う絶縁膜7を形成し、絶縁膜7のエッチングを行って、絶縁膜7に導電膜5の少なくとも一部を露出する開口部51を形成する。また、還元ガス雰囲気中で開口部51に紫外線を照射し、開口部51内に絶縁膜7及び導電膜5に接するバリアメタル膜9を形成し、バリアメタル膜9上に導電膜10を形成する。

(もっと読む)

ミクロスケール構造中でのシード層堆積

半導体装置の製造方法

【課題】本発明は、スパッタ装置の処理能力を損なうことなく、スパッタに異常がないときは金属薄膜の反射率を面内で均一にすることができる半導体装置を提供することを目的とする。

【解決手段】本願の発明にかかる半導体装置の製造方法は、シリコン基板にスパッタ成長により金属膜を形成する第1スパッタ工程と、該第1スパッタ工程の後に該第1スパッタ工程よりも高いDCパワーでさらに金属膜をスパッタ成長させる第2スパッタ工程と、該第1スパッタ工程と該第2スパッタ工程の後に、該第1スパッタ工程および該第2スパッタ工程で形成された金属膜の反射率の均一性を測定する検査工程とを備えたことを特徴とする。

(もっと読む)

半導体装置及びその製造方法

【課題】 半導体装置及びその製造方法に関し、バリアメタルの絶縁膜及びCuに対する密着性と、Cu拡散防止とを両立する。

【解決手段】 第1絶縁膜に設けた凹部の側壁に第2絶縁膜を形成し、第2絶縁膜の内側に順に第2絶縁膜との密着性が優れている第1の導電性バリア層、炭素を含有する第2の導電性バリア層、及び、Cu系埋込電極との密着性が優れている第3の導電性バリア層の3層構造のバリア層を介してCu系埋込電極を設けるとともに、前記第1の導電性バリア層と前記第2の導電性バリア層との界面と、前記第2の導電性バリア層と前記第3の導電性バリア層との界面に炭素混合領域を設ける。

(もっと読む)

半導体装置の製造方法

【課題】貫通孔となるべきアスペクト比が20以上の深孔を埋め込む貫通電極金属としては、埋め込み特性が良好なタングステンが使用されることが多いが、通常のドライエッチングによる深孔は、ボッシュプロセスによるものに比べて寸法の大きなものとなる。この比較的大きな深孔を埋め込むためには、必然的にウエハの表面に成膜すべきタングステン膜の膜厚も厚くなり、その結果、ウエハの反りが、プロセスを正常に実行できる限界を超える程度にまで増加する。また、このような問題が許容できる限度内である場合にも、タングステン膜を堆積する際に、ウエハの周辺で下地膜の剥がれが発生する等の問題がある。

【解決手段】本願発明は、貫通ビアを形成するための非貫通孔をタングステン部材で埋め込むに当たり、ウエハの周辺部において、下地のバリアメタル膜の外延部より内側に、タングステン部材の外延部を位置させるように成膜を実行するものである。

(もっと読む)

半導体装置及びその製造方法

【課題】配線の表皮効果の抑制と低抵抗化を図る。

【解決手段】第1配線部41と、その第1配線部41の周りを被覆する、高融点金属窒化物を含む第2配線部42とを含む配線40aを形成する。このような配線40aにおける第2配線部42は、第1配線部41側から外周に向かって窒素含有率が高くなる部分を有するように形成する。これにより、配線40aにおける表皮効果が抑制されると共に、配線40aの低抵抗化が図られるようになる。

(もっと読む)

半導体装置およびその製造方法

【課題】簡便に半導体集積回路を小領域に電気的に分離する。

【解決手段】厚さが150〜600μm程度のInP基板、GaAs基板等の化合物半導体基板1の表面に半導体集積回路2を形成し、化合物半導体基板1の裏面(半導体集積回路2が形成された表面とは反対側の面)に、直角に交わっている複数の切込溝3を設け、半導体集積回路2の表面から切込溝3の底面までの距離を50〜150μmとし、切込溝3内にAu等の金属4を埋め込み、金属4を化合物半導体基板1の裏面全面にも設ける。

(もっと読む)

プラズマ化学気相堆積による、有機官能基と共にシリコンを含有するハイブリッド前駆体を使用する超低誘電材料

低誘電率層を基板上に堆積するための方法が提供される。一実施形態では、本方法は、1種または複数のオルガノシリコン化合物をチャンバに導入するステップであって、1種または複数のオルガノシリコン化合物がシリコン原子およびこのシリコン原子に結合されたポロゲン成分を含むステップと、1種または複数のオルガノシリコン化合物を、RF電力の存在下で反応させることにより、低誘電率層をチャンバ内の基板上に堆積させるステップと、低誘電率層からポロゲン成分が実質的に除去されるようにこの低誘電率層を後処理するステップとを含む。任意選択で、不活性キャリアガス、酸化ガス、またはその両方を、1種または複数のオルガノシリコン化合物と共に処理チャンバ内に導入してもよい。後処理プロセスは、堆積した材料の紫外線硬化とすることができる。UV硬化プロセスは、熱または電子ビーム硬化プロセスと同時にまたは連続して使用してもよい。低誘電率層は、良好な機械的性質および望ましい誘電率を有する。  (もっと読む)

(もっと読む)

成膜方法、半導体装置の製造方法及び半導体装置

【課題】表面の平坦性の優れたシリコン膜を形成する成膜方法、半導体装置の製造方法及び半導体装置を提供する。

【解決手段】基体上にジシラン及びトリシランの少なくともいずれかを用いて第1温度で第1膜を形成する第1膜形成工程と、前記基体及び前記第1膜を、水素を含む雰囲気中において、前記第1温度から、前記第1温度よりも高い第2温度に向けて昇温する昇温工程と、前記昇温の後に、前記第1膜の上に、シランを用いて前記第2温度で第2膜を形成する第2膜形成工程と、を備えたことを特徴とする成膜方法が提供される。

(もっと読む)

半導体装置の製造方法

【課題】絶縁膜のストレスに耐え、絶縁膜からの酸素や水分の影響を抑制しつつ、エレクトロマイグレーションの耐性や配線間の耐圧も改善することが可能な半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法では、(a)凹部102が形成された絶縁膜101上に、TaN膜103を成膜する工程と、(b)TaN膜103上に、Taよりも熱膨張係数が大きいTiを主成分とするTi膜104を成膜する工程と、(c)Ti膜104上に、Tiよりも熱膨張係数が大きいCuを主成分とするCu膜105を成膜する工程と、(d)Cuを、電解めっきにより、凹部102内に埋め込む工程とを含む。

(もっと読む)

半導体装置

【課題】電極パッドからの水分の拡散を防止できると共に、絶縁膜の薄膜化及び低誘電率化に対応できるようにする。

【解決手段】半導体装置は、半導体基板11の上方に形成され、外部との電気的な接続を取る接続部25である電極パッドと、半導体基板と接続部との間に積層された絶縁膜14等にそれぞれ形成され、上層の配線34が接続部と接続された複数の第1配線層及び該第1配線層同士を接続するビア31よりなる積層構造体27と、複数の絶縁膜に積層構造体の周囲を隙間なく囲むように形成され、複数の第2配線層40等及び該第2配線層同士を線状に接続するラインビア41よりなるリング構造体28と、接続部と内部回路とを電気的に接続する引き出し配線32Aとを有している。積層構造体とリング構造体とは複数の第1配線層の少なくとも1つによって互いに接続されており、引き出し配線はリング構造体と接続されている。

(もっと読む)

パッケージおよびその製造方法

【課題】工程時間を短縮し、平坦度(又は、ボンディングの均一性)を高め、絶縁層(絶縁基板)とチップとの間の接着力が向上したパッケージおよびその製造方法を提供することを目的とする。

【解決手段】本発明のパッケージは、パターニング層上に形成された第1導電層と、前記パターニング層上に前記第1導電層を埋め込むように形成された絶縁層と、前記絶縁層の外面に形成された第2導電層と、前記第1導電層と第2導電層とを電気的に接続するように前記絶縁層の内部に形成された第3導電層とを含むことを特徴とする。

(もっと読む)

半導体集積回路装置の製造方法

【課題】信頼性の高い半導体集積回路装置の製造プロセスを提供する。

【解決手段】銅ダマシン配線プロセスのバリアメタル膜のタンタル系積層膜に関し、スパッタリング成膜チャンバ内のシールド内面に、比較的薄い窒化タンタル膜およびタンタル膜が交互に成膜されるが、この連続成膜プロセスを断続的に繰り返すと、膜の内部応力により剥がれて、異物やパーティクルの原因となる。この異物やパーティクルの防止のため、繰り返し、成膜するに際して、所定の間隔を置いて、厚い膜厚を有する異物防止用タンタル膜をチャンバの実質的な内壁に成膜する工程を設ける。

(もっと読む)

半導体装置及びその製造方法

【課題】貫通電極の基板からの抜け落ちを防止する。

【解決手段】半導体装置は、基板80と、基板80に設けられた1又は複数のビアホール91と、1又は複数のビアホール91内にそれぞれ設けられた貫通電極TSVとをそれぞれ有する複数のコアチップと、貫通電極TSVを通じて各コアチップと電気的に接続するインターフェースチップとを備え、ビアホール91は、両端部の径r1,r3に比べて中央部r2の径が大きいボーイング形状部分91aを有する。

(もっと読む)

半導体装置及びその製造方法

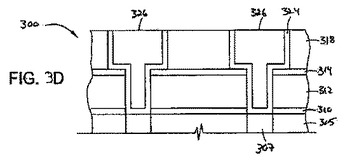

【課題】 高信頼性を有するデュアルダマシン構造を用いた半導体装置及びその製造方法を提供することができる。

【解決手段】 半導体基板上に形成された第一の絶縁膜と、前記第一の絶縁膜に形成されたコンタクトと、前記第一の絶縁膜上に形成され、前記第一の絶縁膜よりも誘電率の低い第二の絶縁膜と、前記第二の絶縁膜に形成され、前記コンタクトと電気的に接続される配線とを備え、前記コンタクト底面及び、前記配線の側面に第一のバリアメタルが形成され、前記コンタクト側面及び前記第一のバリアメタル上に第二のバリアメタルが形成されている。

(もっと読む)

61 - 80 / 600

[ Back to top ]