Fターム[5F033QQ10]の内容

半導体集積回路装置の内部配線 (234,551) | パターン形成方法,基板,導電膜,絶縁膜の処理方法 (47,095) | エッチング (29,543) | エッチングの対象 (10,331) | 積層膜 (1,279)

Fターム[5F033QQ10]に分類される特許

41 - 60 / 1,279

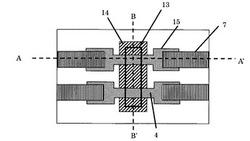

半導体装置

【課題】ヒューズ開口部からの水分侵入による電特異常及び配線腐食を防止する半導体装置を提供する。

【解決手段】ヒューズ配線4の下方には凸領域となるTEOS膜14の下敷きがあり、ヒューズ配線4はTEOS膜14を跨ぐように設けられ、ヒューズ配線4の上方にはTEOS膜14よりも小さい領域のヒューズ開口部13が設けられる。さらに、TEOS膜14の無い領域にてヒューズ配線14の両端に設けられたヒューズ端子15には第1金属配線7が電気的に接続されている。

(もっと読む)

半導体装置及びその製造方法

【課題】柱状半導体層の幅を広く維持することができる半導体装置を提供すること。

【解決手段】半導体装置は、一つの直線上に順に形成された、第1、第2及び第3の柱状半導体層と、第2及び第3の柱状半導体層の間の空間であって第2及び第3の柱状半導体層の側面に夫々設けられた第1及び第2のゲート電極と、第1及び第2の柱状半導体層の間の空間及び第2及び第3の柱状半導体層の空間に埋め込まれた層間絶縁膜とを有する。層間絶縁膜は、第1及び第2の柱状半導体層の間の空間内であってゲート電極を介することなく第1及び第2の柱状半導体層の側面に形成され、第2及び第3の柱状半導体層の間の空間内であって第1及び第2のゲート電極を介して第2及び第3の柱状半導体層の側面に形成されている。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】メモリセル積層構造間に空隙を有する不揮発性半導体記憶装置において、隣接するメモリセル積層構造間、及び、メモリセル積層構造−選択ゲート積層構造間のショートを防ぐことができる不揮発性半導体記憶装置およびその製造方法を提供する。

【解決手段】実施形態に係る不揮発性半導体記憶装置は、シリコン基板上にゲート絶縁膜、浮遊ゲート電極、電極間絶縁膜および制御ゲート電極が順に積層されたメモリセル積層構造が複数隣接して配置され、隣接する前記メモリセル積層構造間に空隙を有する不揮発性半導体記憶装置であって、前記メモリセル積層構造間のシリコン基板上に、前記メモリセル積層構造の側壁に形成されたシリコン酸化膜より厚いシリコン酸化膜が形成されている。

(もっと読む)

半導体装置

【課題】残渣による配線間のショートの発生を防ぐ。

【解決手段】本発明の半導体装置は、高誘電率材料を含む第1のゲート絶縁膜4と第1のゲート絶縁膜4上に形成された第1のメタルゲート電極5とを備える第1のトランジスタが形成される半導体基板上の第1の領域と、高誘電率材料を含む第2のゲート絶縁膜4と第2のゲート絶縁膜上に形成された第2のメタルゲート電極12とを備え、第1のトランジスタとは閾値電圧の異なる第2のトランジスタが形成される半導体基板上の第1の領域に並ぶ第2の領域と、電位の異なる第1および第2の配線と、を有し、第1の領域と第2の領域との境界が、第1および第2の配線の少なくとも一方としか重ならない。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】ワード線抵抗を低減し、かつ、周辺回路のトランジスタの特性変化を抑制することができる半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、半導体基板と、複数のメモリセルと、周辺回路とを備える。メモリセルは、半導体基板の上方に設けられたフローティングゲートと、フローティングゲート上に設けられたゲート間絶縁膜と、ゲート間絶縁膜上に設けられたコントロールゲートとを含む。周辺回路は、互いに電気的に接続されたフローティングゲートおよびコントロールゲートと、少なくともフローティングゲートとコントロールゲートとの間の電気的接触部分に設けられ該フローティングゲートと該コントロールゲートとの間の電気的接続を妨げない絶縁薄膜とを含むトランジスタを含む。複数のメモリセルは、コントロールゲート内に絶縁薄膜を含まない。メモリセルおよび周辺回路において、コントロールゲートの少なくとも上部はシリサイド化されている。

(もっと読む)

不揮発性半導体記憶装置

【課題】隣接する配線の間におけるリークを抑制することができる不揮発性半導体記憶装置を提供する。

【解決手段】不揮発性半導体記憶装置1は、シリコンを含む基板11と、基板11の上に設けられた複数のメモリセルと、複数のメモリセルの上方に設けられた配線7と、配線7の上に設けられたリーク抑制層8と、前記リーク抑制層8の上方に設けられた層間絶縁膜10と、を備えている。そして、隣接するメモリセルの間、および、隣接する配線7の間には空隙12が形成され、リーク抑制層8の幅寸法は、配線7の幅寸法よりも短いこと、および、隣接するリーク抑制層8の間の寸法は、隣接する配線7の間の寸法よりも長いこと、の少なくともいずれかである。

(もっと読む)

半導体装置の製造方法

【課題】アライメント光によるアライメントマークの検出感度を向上させて、低コストで貫通孔の位置合わせを行う。アライメントマークの誤検出を防ぐ。また、アライメントマーク検出時のアライメント光の露光マージンを大きくして、微細化に対応可能な半導体装置の製造方法を提供する。

【解決手段】半導体基板の非有効ショット領域において、半導体基板の主面又は主面よりも上方にアライメントマークを形成する。半導体基板の裏面の方から、アライメントマークが形成された位置に対応する開口を形成する。半導体基板内に形成されている半導体装置の構成パターンと露光用マスクパターンとの位置合わせをして、有効ショット領域の半導体基板内に貫通孔を形成する。

(もっと読む)

エッチング液

【課題】 銅及びモリブデン積層膜を一液でエッチングでき、しかも工業的に好ましい形状にエッチングできるエッチング液を提供する。

【解決手段】 過酸化水素、グリシン、燐酸及び水を含むエッチング液を、銅及びモリブデン積層膜のエッチングに用いる。

(もっと読む)

不揮発性記憶素子及び不揮発性記憶装置並びにそれらの製造方法

【課題】良好な電気的特性が得られる不揮発性記憶素子及びその製造方法を提供する。

【解決手段】第1の配線103と、第1の配線103上に形成され、第1の配線103に接続される第1のプラグ107及び第2のプラグ108と、第1電極109、第2電極113、及び抵抗変化層112を有し、第1のプラグ107上に形成され、第1電極109が第1のプラグ107と電気的に接続されている抵抗変化素子114と、抵抗変化素子114上に形成され、第2電極113と電気的に接続されている第2の配線119と、第2のプラグ108上に形成され、第2のプラグ108と電気的に接続されている第3の配線121とを備え、第1のプラグ107の上面と第2のプラグ108の上面とが略同一平面内に形成され、かつ第2の配線119の上面と第3の配線121の上面とが略同一平面内に形成されている。

(もっと読む)

銅および銅合金のエッチング液

【課題】

本発明の課題は、銅層と銅酸化物層および/または銅合金層とを含む金属積層膜パターンを精度良くエッチング加工し、優れた断面形状を形成し、かつ実用性に優れた安定で液寿命の長いエッチング液組成物、およびかかるエッチング液組成物を用いたエッチング方法を提供することにある。

【解決手段】

本発明は銅層と銅酸化物層および/または銅合金層とを有する金属積層膜を、過硫酸塩および/または過硫酸溶液0.1〜80重量%と、りん酸0.1〜80重量%と、硝酸および/または硫酸0.1〜50重量%とを含有するエッチング液組成物であり、さらに塩化物イオンやアンモニウムイオンを加えることで、エッチングレートや断面形状を容易に制御することが可能となるエッチング液組成物またはエッチング方法に関する。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体装置の素子形成領域へのクラックなどの伝播を確実に防止する。

【解決手段】ウェハ1上の素子形成領域を覆うガード領域4の外側に、n型拡散層15を形成する。n型拡散層15の上には、導電性リング33,48,58を形成する。最上層の導電性リング48の上に、導電層65を形成する。導電層65の端面65Sは、導電性リング58の端面58Sから距離L1だけ内側に形成し、導電性リング58の上面の一部を露出させる。この後、半導体基板をアミン系薬液に浸すと、n型拡散層15と導電層65の間の導電性プラグ33,48,48の導電性材料を溶出し、スリットが形成される。

(もっと読む)

配線膜およびそれを用いたアクティブマトリクス基板、並びに配線膜の製造方法

【課題】テーパー形状のAl配線膜を容易かつ安定的に得る。

【解決手段】Al配線膜101は、AlもしくはAl合金から成る第1のAl合金層101aと、その上に配設され、Ni、PdおよびPtのいずれか1以上の元素を含み第1のAl合金層101aとは異なる組成のAl合金から成る第2のAl合金層101bとから成る二層構造を有する。フォトレジスト102の現像処理に用いるアルカリ性薬液により、第2のAl合金層101bはエッチングされ、その端部はフォトレジスト102の端部よりも後退する。その後、フォトレジスト102をマスクとするウェットエッチングを行うことにより、Al配線膜101の断面はテーパー形状となる。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】メモリセルの制御性を向上した不揮発性半導体記憶装置及びその製造方法を提供する。

【解決手段】実施形態に係る不揮発性半導体記憶装置は、構造体と、複数の半導体層と、メモリ膜と、接続部材と、導電部材と、を備える。前記構造体は、メモリ領域と非メモリ領域とを有する基板の前記メモリ領域の上に設けられる。前記構造体は、前記基板の主面に対して垂直な第1軸に沿って積層され複数の電極膜を含む。前記半導体層は、前記構造体を前記第1軸に沿って貫通する。前記メモリ膜は、前記複数の電極膜と前記半導体層との間に設けられる。前記接続部材は、前記基板と前記半導体層との間に設けられる。前記接続部材は、隣り合う2つの前記半導体層のそれぞれの端部と接続される。前記導電部材は、前記基板と前記接続部材との間で、前記メモリ領域から前記非メモリ領域に延在して設けられる。前記導電部材は、前記非メモリ領域の上に設けられた凹部を有する。前記凹部内には、第1シリサイド部が設けられる。

(もっと読む)

半導体装置

【課題】層間絶縁膜のエッチングの際に半導体層がエッチングされることによるコンタク

ト抵抗の増大を防ぎ、書き込み特性及び電荷保持特性に優れた不揮発性半導体記憶装置及

びその作製方法を提供する。

【解決手段】ソース領域又はドレイン領域とソース配線又はドレイン配線との間に導電層

を設ける。また、該導電層は、制御ゲート電極を形成する導電層と同じ導電層からなる。

また、該導電層を覆うように絶縁膜が設けられており、該絶縁膜は該導電層の一部が露出

するコンタクトホールを有する。また、該ソース配線又はドレイン配線は、該コンタクト

ホールを埋めるように形成されている。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、小型化を図ることが可能になると共に、絶縁リングで囲まれた貫通電極を狭ピッチで配置することの可能な半導体装置及びその製造方法を提供することを課題とする。

【解決手段】回路素子層5が形成される表面1a、及び裏面1bを有する半導体基板1と、半導体基板1を貫通し、かつ半導体基板1の表面1a側から半導体基板1の裏面1b側に向かうにつれて幅が広くなる貫通電極7と、貫通電極7を囲むように半導体基板を貫通し、かつ半導体基板1の表面1a側から半導体基板1の裏面1b側に向かうにつれて幅が狭くなる第1の絶縁リング3と、を有し、半導体基板1の厚さ方向Aにおいて、第1の絶縁リング3の少なくとも一部と対向するように貫通電極7を配置する。

(もっと読む)

ヒューズ、半導体装置、半導体装置の製造方法

【課題】高電圧が不要で安定した状態を得ること。

【解決手段】半導体装置10に形成されたヒューズ素子11は、概略的に、拡散領域22と、拡散領域22と一部重なるように拡散領域22より上方に形成された導電体25を含む。半導体装置10の半導体基板21には、拡散領域22が形成されている。半導体基板21には素子分離領域23が形成されている。拡散領域22を含む半導体基板21上には絶縁膜24が形成されている。絶縁膜24上には、導電体25が形成されている。導電体25上には、カバー膜26が形成されている。カバー膜26は、導電体25の上面及び側面を覆うように形成されている。カバー膜26は、絶縁膜24より高い引っ張り応力を持つ。

(もっと読む)

電極構造、半導体素子、半導体装置、サーマルヘッドおよびサーマルプリンタ

【課題】シェア強度の向上した電極構造を提供する。

【解決手段】電極構造C1は、基体2と、基体2上に設けられた電極4と、電極4上に設けられためっき層14とを備え、めっき層14は、第1部位14aと、第1部位14a上に位置する第2部位14bとを有しており、平面視して、第1部位14aの面積が第2部位14bの面積よりも大きいことから、電極構造C1のシェア強度を向上させることができ、シェア強度の向上した電極構造を提供することができる。

(もっと読む)

成膜方法、これを含む半導体装置の製造方法、成膜装置、及び半導体装置

【課題】柱状形状を有し密に配列される電極の倒壊を防ぐことが可能な半導体装置を提供する。

【解決手段】電界効果トランジスタと、柱状形状を有するキャパシタとを有する半導体装置であって、前記電界トランジスタの不純物拡散領域と電気的に接続し、柱状形状を有する第1の電極と、前記第1の電極の少なくとも側面に形成される誘電体膜と、前記誘電体膜上に形成される第2の電極と、前記柱状形状を有する前記第1の電極の長手方向と交差する方向に延び、前記第2の電極の少なくとも一部を貫通して前記第1の電極を連結するホウ素添加窒化シリコン膜により形成される支持膜とを備える半導体装置により、上記の課題が達成される。

(もっと読む)

半導体ウェハ及び半導体装置の製造方法

【課題】第1の溝への絶縁膜の埋設性が向上させて、埋設不良を軽減する。アライメントマークにおける埋設不良個所での応力集中がもたらす基板へのクラックを軽減する。

【解決手段】基板の第1の主面に、第1の溝、および前記第1の主面に対向して見た形状が環状となりかつ前記第1の溝よりも深い第2の溝を形成する工程と、第1の溝と第2の溝とを埋め込むように絶縁膜を形成する工程と、絶縁膜を形成する工程の後、基板の第1の主面にフォトレジスト膜を形成する工程と、絶縁膜で埋め込まれた第1の溝の基板上での位置を基準として位置合わせした第1のパターンをフォトレジスト膜に転写する工程と、絶縁膜で埋め込まれた環状の第2の溝の内側に位置する基板に、基板を厚さ方向に貫通する貫通電極を形成する工程と、を有することを特徴とする半導体装置の製造方法。

(もっと読む)

窒化物半導体装置

【課題】ドレイン電極配線によって形成されるフィールドプレートに起因する電流コラプス現象への影響が抑制された窒化物半導体装置を提供する。

【解決手段】窒化物半導体からなる機能層20と、機能層20上に離間して配置されたソース電極3及びドレイン電極4と、ソース電極3とドレイン電極4間で機能層20上に配置されたゲート電極5と、機能層20上に配置された層間絶縁膜7と、層間絶縁膜7上に配置され、ドレイン電極4と電気的に接続されたドレイン電極配線41とを備える窒化物半導体装置であって、ゲート電極5とドレイン電極4間において、層間絶縁膜7を介してドレイン電極配線41が機能層20と対向する領域を有さない。

(もっと読む)

41 - 60 / 1,279

[ Back to top ]