Fターム[5F033QQ10]の内容

半導体集積回路装置の内部配線 (234,551) | パターン形成方法,基板,導電膜,絶縁膜の処理方法 (47,095) | エッチング (29,543) | エッチングの対象 (10,331) | 積層膜 (1,279)

Fターム[5F033QQ10]に分類される特許

101 - 120 / 1,279

半導体装置

【課題】小型化、薄型化、軽量化を実現した半導体装置の提供を課題とする。また、作製時間を短縮し、歩留まりを向上することができる半導体装置の作製方法の提供を課題とする。

【解決手段】トランジスタと、トランジスタ上に設けられた絶縁層と、絶縁層に設けられた開口部を介して、トランジスタのソース領域又はドレイン領域に電気的に接続された第1の導電層(ソース配線又はドレイン配線に相当)と、絶縁層及び第1の導電層上に設けられた第1の樹脂層と、第1の樹脂層に設けられた開口部を介して、第1の導電層に電気的に接続された導電性粒子を含む層と、第2の樹脂層及びアンテナとして機能する第2の導電層が設けられた基板とを有する。上記構成の半導体装置において、第2の導電層は、導電性粒子を含む層を介して、第1の導電層に電気的に接続されている。また、第2の樹脂層は、第1の樹脂層上に設けられている。

(もっと読む)

Ti合金バリアメタルを用いた配線膜および電極、並びにTi合金スパッタリングターゲット

【課題】ウエットエッチングによる加工性に優れた特性を有する新規な配線用膜を提供する。

【解決手段】表示装置またはタッチパネルセンサーの配線用膜であって、合金成分としてX群元素(Xは、希土類元素、Ge、Si、Sn、Hf、Zr、Mg、Ca、Sr、Al、Zn、Mn、Co、Fe、及びNiよりなる群から選択される少なくとも一種の元素)を3〜50原子%、および/または酸素を0.2〜3.0質量%含有し、残部Tiおよび不可避不純物からなるTi合金層と、純CuまたはCu合金からなる層とを含む2層以上の積層構造を有することに要旨を有する配線用膜。

(もっと読む)

半導体装置及びその製造方法

【課題】コンタクトホール内にめっき層から成るコンタクト層を埋め込んで上下層の電気的接続を行うときの、コンタクト層の埋め込み性を良好にする構造の半導体装置を提供する。

【解決手段】配線層12,16と、少なくとも底部において、三角形の平面形状であるコンタクトホール14と、めっき層から成り、コンタクトホール14の内部を埋めて形成され、配線層12,16に接続されたコンタクト層15とを含む、半導体装置を構成する。

(もっと読む)

Ti合金バリアメタルを用いた配線膜および電極、並びにTi合金スパッタリングターゲット

【課題】ウエットエッチングによる加工性に優れた特性を有する新規な金属配線用膜を提供すること。

【解決手段】表示装置またはタッチパネルセンサーの配線用膜であって、合金成分としてX群元素(Xは、希土類元素、Ge、Si、Sn、Hf、Zr、Mg、Ca、Sr、Al、Zn、Mn、Co、Fe、及びNiよりなる群から選択される少なくとも一種の元素)を3〜50原子%、および/または酸素を0.2〜3.0質量%含有し、残部Tiおよび不可避不純物からなるTi合金層(第1層)と、Al系膜からなる第2層とを含む積層構造を有することに要旨を有する配線用膜。

(もっと読む)

積層した接続レベルを有する集積回路装置用マスク数の低減法

【課題】3D積層メモリ装置は、各接続レベル毎に別個のマスクが使用されるので必要なマスク数は多くなるが、パターンを工夫して必要マスク数を減らす。

【解決手段】3次元積層集積回路装置は配線領域に接続レベルの積層部を有する。接続レベルの積層部で2のN乗個のレベルまで含む配線接続領域を形成するためのN個のエッチングマスクの組だけが必要とされる。幾つかの例によれば、2のX−1乗(2X−1)個の接続レベルは、連続番号Xのエッチングマスクでエッチングされ、1つのマスクがX=1であり、他の1つのマスクがX=2であり、X=Nまで付与される。当該方法は接続レベルでの形成領域に整合した配線接続領域を形成する。

(もっと読む)

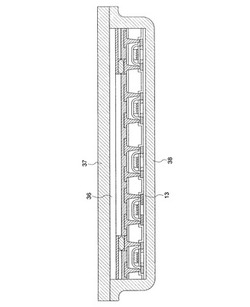

半導体装置の作製方法

【課題】本発明は、薄膜トランジスタのソース領域やドレイン領域へのコンタクトを確実

にした半導体装置を提供するものである。

【解決手段】本発明における半導体装置において、半導体層上の絶縁膜およびゲイト電極

上に形成された第1の層間絶縁膜と、前記第1の層間絶縁膜の上に形成された第2の層間

絶縁膜と、前記第2の層間絶縁膜、前記第1の層間絶縁膜、および前記絶縁膜に設けられ

たコンタクトホールとを有する。前記第1の絶縁層の膜厚は、前記積層の絶縁膜の合計膜

厚の1/3以下に形成する。

(もっと読む)

表示装置及び電子機器

【課題】可撓性を有する基板上に有機化合物を含む層を有する素子が設けられた半導体装置を歩留まり高く作製することを課題とする。

【解決手段】基板上に剥離層を形成し、剥離層上に、無機化合物層、第1の導電層、及び有機化合物を含む層を形成し、有機化合物を含む層及び無機化合物層に接する第2の導電層を形成して素子形成層を形成し、第2の導電層上に第1の可撓性を有する基板を貼りあわせた後、剥離層と素子形成層とを剥す半導体装置の作製方法である。

(もっと読む)

半導体装置の製造方法及び記憶媒体

【課題】被エッチング膜の上に積層された、有機膜と、その有機膜の上に積層されたレジストパターンが開口したレジスト膜とを備える、被エッチング膜のエッチングマスクとなる複数層レジストの前記有機膜に、高い垂直性を有するマスクパターンを形成すること。

【解決手段】前記複数層レジストの前記有機膜を、二酸化炭素と水素とを含む処理ガスをプラズマ化して得たプラズマにより前記レジストパターンに沿ってエッチングして、前記被エッチング膜をエッチングするためのマスクパターンを形成する。実験により複数層レジストを構成する有機膜に垂直性が高いマスクパターンを得ることができることが示されている。

(もっと読む)

半導体装置の製造方法

【課題】所望の微細化パターンを高精度かつ効率良く形成することができ、生産効率を向上させることのできる半導体装置の製造方法を提供する。

【解決手段】トリミングされたフォトレジスト層104のラインパターンの上に第1の膜105を成膜する工程と、前記ラインパターンの側壁部以外にある第1の膜105およびフォトレジスト層104を除去する工程と、該除去後に残った部分の第1の膜105をマスクとして反射防止膜103とコア層102をエッチングし、コア層102をラインパターンとする工程と、ラインパターン化コア層102の上に第2の膜106を成膜する工程と、ラインパターン化コア層102の側壁部以外にある第2の膜106およびラインパターン化コア層102を除去する工程と、該除去後に残った部分の第2の膜106をマスクとして被エッチング層101をエッチングし、ラインパターンとする工程とを備えた製造方法とする。

(もっと読む)

半導体装置

【課題】nチャネル型電界効果トランジスタとpチャネル型電界効果トランジスタを有する半導体装置において、nチャネル型電界効果トランジスタ、pチャネル型電界効果トランジスタ共にドレイン電流特性に優れた半導体装置を実現する。

【解決手段】nチャネル型電界効果トランジスタ10と、pチャネル型電界効果トランジスタ30とを有する半導体装置において、nチャネル型電界効果トランジスタ10のゲート電極15を覆う応力制御膜19には、膜応力が引張応力側の膜を用いる。pチャネル型電界効果トランジスタ30のゲート電極35を覆う応力制御膜39には、膜応力が、nチャネル型トランジスタ10の応力制御膜19より、圧縮応力側の膜を用いることにより、nチャネル型、pチャネル型トランジスタの両方のドレイン電流の向上が期待できる。このため、全体としての特性を向上させることができる。

(もっと読む)

半導体装置

【課題】高い耐電圧特性、および耐リーク特性を有する配線構造を備える半導体装置、およびその製造方法を提供する。

【解決手段】本発明の実施の形態による半導体装置は、半導体素子が設けられた半導体基板と、前記半導体基板上に形成された、上下層の導電部材を電気的に接続する接続部材と、前記接続部材と同じ層に形成された第1の絶縁膜と、前記接続部材の上面の一部と接する第1の領域、および前記第1の領域上に位置し、前記第1の領域よりも幅の広い第2の領域を含む配線と、前記第1の絶縁膜上に、前記配線の前記第1の領域の側面の上側から少なくとも一部、および前記第2の領域の底面に接して形成された第2の絶縁膜と、を有する。

(もっと読む)

半導体素子及びその形成方法

【課題】半導体素子及びその形成方法に関し、工程マージンを向上させる。

【解決手段】半導体素子は、半導体基板10に備えられるメインゲート20及び素子分離構造、前記素子分離構造の上部に備えられる分離パターン40及び前記分離パターンの両端に備えられるコンタクトプラグ54を含む。格納電極コンタクトと活性領域との間のフルオーバーラップを提供し、食刻工程でのオーバーレイ問題を解消し、格納電極の食刻線幅を増加させる。

(もっと読む)

半導体装置

【課題】プロセス数を増大させることなく、応力を緩和できる構造を有する半導体装置を提供する。

【解決手段】一方の面に埋め込み酸化層と半導体層がこの順で積層される半導体基板10を加工して作製され、前記一方の面側で他の基板に接合される半導体装置であって、前記埋め込み酸化層及び前記半導体層を加工して形成される半導体素子20と、前記埋め込み酸化層及び前記半導体層を加工して形成され、前記半導体素子に接続される配線部と、前記配線部の端部に連続する前記半導体層によって構成され、当該半導体層の下側の埋め込み酸化層が除去されて前記半導体基板との間に空隙が形成されるパッド部40と、前記パッド部と前記他の基板を接合する接合部とを含む。

(もっと読む)

半導体素子及びその製造方法

【課題】絶縁膜を貫通するコンタクトプラグの抵抗を改善させられる半導体素子及びその製造方法を提供する。

【解決手段】半導体基板上に形成された第1層間絶縁膜と、前記第1層間絶縁膜を貫通して形成されたコンタクトホールと、前記コンタクトホールの内部に形成されたコンタクトプラグと、前記コンタクトホール内で前記コンタクトプラグの上部側壁を部分的に覆うスペーサと、を含む。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の製造方法において、異なる膜特性を有する絶縁膜に形成されるコンタクト形状の制御性を向上させる。

【解決手段】半導体基板に素子領域を形成し、半導体基板の第1の領域上に、第1の絶縁膜を形成し、半導体基板の第2の領域上に、膜応力及びコンタクトの形成の際のエッチング加工時のエッチングレートが、第1の絶縁膜と異なる第2の絶縁膜を形成し、少なくとも第2の絶縁膜において、コンタクトが形成されるコンタクト領域に選択的にUV光を照射し、UV光を照射した後、第1の絶縁膜及び前記第2の絶縁膜をエッチングして前記コンタクトを形成する。

(もっと読む)

半導体装置の製造方法、及び固体撮像装置の製造方法

【課題】 精度よく開口を形成することが可能な半導体装置の製造方法を提供する。

【解決手段】 第1の絶縁膜となる部材と、第1の絶縁膜となる部材と異なる材料からなる第2の絶縁膜となる部材と、第3の絶縁膜となる部材と、第3の絶縁膜となる部材と異なる材料の第4の絶縁膜となる部材とがこの順に積層された半導体基板の上に、複数の絶縁膜の開口を形成するための開口を有するマスクを形成する工程と、第3の絶縁膜となる部材のマスクの開口に対応する部分と第4の絶縁膜となる部材のマスクの開口に対応する部分を連続して除去する第1の工程と、第1の工程を行った後に、第2の絶縁膜となる部材のマスクの開口と対応する部分を除去する第2の工程と、を有する。

(もっと読む)

半導体装置

【課題】半導体装置の小型化、特に、狭ピッチ化に対する技術を提供する。

【解決手段】半導体チップ1C上に設けられたパッド2と、プローブ領域10Aおよび接続領域10Bのパッド2上に開口部11を有し、半導体チップ1C上に設けられたパッシベーション膜3と、接続領域10Bのパッド2上に開口部12を有し、パッド2上およびパッシベーション膜3上に設けられたパッシベーション膜5と、パッド2と電気的に接続され、接続領域10B上およびパッシベーション膜5上に設けられた再配線7とを備える。接続領域10Bより半導体チップ1Cの外周部側に設けられたプローブ領域10Aのパッド2にプローブ痕100が存在し、接続領域10Bから半導体チップ1Cの中央部側に延びて再配線7が存在している。

(もっと読む)

金属膜

【課題】配線金属膜の酸化を防止し、さらに、酸化防止を行うことで新たに発生した電解腐食も防止する。

【解決手段】基材としてのフィルム2上に、ITO膜3が形成され、その上に金属膜4が形成される。金属膜は、NiCu合金膜からなる第2保護膜41、Alよりも抵抗値が低く配線パターンとなる金属配線膜(Al−Nd合金)42、および、NiCu合金膜からなる第1保護膜43の順に積層されて構成される。

(もっと読む)

半導体装置の製造方法

【課題】配線中に残留した不純物金属の濃度が少ない半導体装置の製造方法を提供する。

【解決手段】半導体基板上に絶縁膜を形成し、絶縁膜に凹部を形成し、凹部の形成された絶縁膜の表面に所定の金属元素を含む前駆体膜を形成し、前駆体膜上に配線形成膜を堆積させ、酸化雰囲気下で熱処理を施すことにより、前駆体膜と絶縁膜を反応させ、その境界面に所定の金属元素と絶縁膜の構成元素を含む化合物を主成分とする自己形成バリア膜を形成し、未反応の所定の金属元素を配線形成膜内に拡散移動させて配線形成膜表面で雰囲気中の酸素と反応させ、未反応金属酸化膜として析出させ、未反応金属酸化膜を除去し、未反応金属酸化膜を除去する工程の後、配線形成膜上に、配線形成膜と同一の材料を堆積させて、配線形成膜を積み増した後、凹部外の絶縁膜が露出するまで配線形成膜を平坦化して配線構造を形成する。

(もっと読む)

半導体装置の製造方法

【課題】デュアルダマシン法による銅配線接続において、コンタクト抵抗の上昇を抑制する半導体装置の製造方法を提供する。

【解決手段】第1の配線25上に積層された第1の拡散防止膜27及び層間絶縁膜のうち、第1の層間絶縁膜28をエッチングすることで第1のホールを形成する。第1の拡散防止膜がエッチングされにくい条件で、第1のホールの下方に位置する第1の層間絶縁膜をエッチングして第2のホールを形成する。第2のホールを埋め込むように、第1の層間絶縁膜よりもエッチング速度の速い第2の層間絶縁膜を形成する。第1の層間絶縁膜の上面が露出するまで第2の層間絶縁膜をエッチングすることで、第2のホールと一体とされた配線形成用溝を形成する。第2のホール内に残存する第2の層間絶縁膜を選択的に除去し、第2のホールの下方に位置する第1の拡散防止膜を選択的に除去する。

(もっと読む)

101 - 120 / 1,279

[ Back to top ]