Fターム[5F033QQ11]の内容

半導体集積回路装置の内部配線 (234,551) | パターン形成方法,基板,導電膜,絶縁膜の処理方法 (47,095) | エッチング (29,543) | ドライエッチング (6,179)

Fターム[5F033QQ11]の下位に属するFターム

プラズマエッチング (898)

反応性イオンエッチング(RIE) (1,268)

イオンミリング、スパッタエッチング (405)

エッチングガス (483)

異方性エッチング (964)

等方性エッチング (193)

Fターム[5F033QQ11]に分類される特許

201 - 220 / 1,968

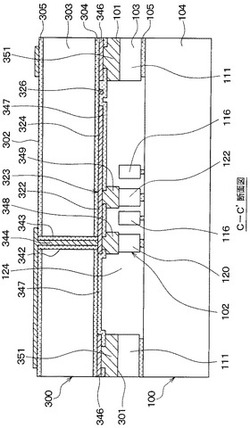

半導体装置およびその製造方法

【課題】センシング部を複数の基板で封止した半導体装置において、基板の平面方向に配線を設けたとしても、配線のレイアウトを簡略化することができる構造、およびその製造方法を提供する。

【解決手段】キャップ部300は、センサ部100に設けられた第1固定部と第2固定部とを電気的に接続したクロス配線部323を備え、クロス配線部323はキャップ部300の一面301に配置されたクロス配線322を備えている。また、キャップ部300は、キャップ部300を貫通し、一端がクロス配線322に電気的に接続され、他端がキャップ部300の他面302に配置された貫通電極344を備えている。これにより、貫通電極344を介してクロス配線322の電位、すなわち、センサ部100の第1固定部および第2固定部の電位をキャップ部300の他面302に取り出すことができる。

(もっと読む)

半導体装置及びその製造方法、並びにデータ処理システム

【課題】メモリセル領域に埋め込みゲート電極を有し、周辺回路領域にプレーナ型ゲート電極と貫通電極を有する半導体装置の製造方法を提供する。

【解決手段】本発明の半導体装置の製造方法は、半導体基板50のメモリセル領域の溝部内に第一のゲート絶縁膜を介して、ワード線を埋め込み形成する工程と、周辺回路領域の前記半導体基板50上に、第二のゲート絶縁膜を介して周辺ゲート電極を形成する工程と、前記半導体基板50の主面上に層間絶縁膜と金属膜とを形成したのちに、前記金属膜をパターニングして、前記メモリセル領域の容量コンタクトパッドと前記周辺回路領域の局所配線127とを同時に形成する工程と、前記局所配線127の下面127a側を露出する開口151を形成したのちに導電体を充填することにより貫通プラグを形成する工程と、を採用する。

(もっと読む)

半導体装置及びその作製方法

【課題】マスク枚数を増加させることなく、積層構造の導電層の下層が露出した構造を有する半導体装置の作製方法を提供する。

【解決手段】ソース電極及びドレイン電極層を形成する導電膜を2層の積層構造で形成し、該導電膜上にエッチングマスクを形成し、該エッチングマスクを用いて該導電膜をエッチングし、該エッチングマスクを残した状態で該導電膜の上層をサイドエッチングして該導電膜の下層の一部を露出させてソース電極及びドレイン電極層とする。このように形成したソース電極及びドレイン電極層と画素電極層は、露出された下層の部分において接続される。ソース電極及びドレイン電極層を形成する導電膜は、例えば、下層をTi層とし、上層をAl層とすればよい。エッチングマスクに開口部が複数設けられていてもよい。

(もっと読む)

パターン形成方法及び回路基板の製造方法

【課題】印刷法にて、容易にヴィアホール等のパターンを形成する方法を提供する事。

【解決手段】基板上に設けられた第一高分子材料からなる第一薄膜をパターニングする際に、第一高分子材料を溶解する第一溶媒に第二高分子材料を溶解させた高分子溶液を準備し、これを第一薄膜に滴下する高分子溶液滴下工程と、第一溶媒が乾燥した後に第一薄膜を第二溶媒に触れさせる第二溶媒接触工程と、を含み、第二溶媒は第一高分子材料を溶解せず、第二高分子材料を溶解する溶媒とする。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の配線間の容量低減を実現するとともに、ミスアライメント・ビアを対策する。

【解決手段】配線上及び配線間のスペース領域に絶縁膜74を形成し、隣接配線間隔が狭い配線の上面を露出するスルーホールの周辺領域の絶縁膜74をリザーバーとして残して、周辺領域以外の絶縁膜74を除去し、絶縁膜74が除去された配線間のスペース領域に空隙を残しつつ、配線上に絶縁膜77を形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体基板に設けられた穴に、絶縁体を介して2つの導電体を充填してなる電極部を有する半導体装置において、2つの導電体間の容量を大きくするのに適した構成を提供する。

【解決手段】半導体基板10の第1の領域1には、表面11に開口する複数個の有底穴20が設けられ、第2の領域2には貫通穴30が設けられ、有底穴20は貫通穴30よりも小さい穴幅を有する。絶縁体50を両導電体40、60で挟んでなる積層構造体が、有底穴20および貫通穴30に充填され、さらに、第1の領域1において複数個の有底穴20間にて連続して形成されており、第1の領域1は、当該積層構造体による容量形成部として構成される。有底穴60における各導電体40、60は、それぞれ貫通穴30における各導電体40、60に電気的に接続されて、半導体基板10の表裏両面11、12に取りだされている。

(もっと読む)

配線形成方法

【課題】下層配線層と配線シード層との密着性を低下させないで高く維持することが可能な配線形成方法を提供する。

【解決手段】下層配線層4と絶縁性バリヤ層6と層間絶縁膜8と上層配線層が順次積層された被処理体に対して上層配線層と、連通配線層16とを形成する配線形成方法において、絶縁性バリヤ層を残した状態で連通ホール9Bを形成し、連通ホール内に犠牲膜を埋め込み、トレンチ9Aを形成するパターンマスク62を形成する前処理工程と、トレンチを形成するトレンチ形成工程と、犠牲膜60とパターンマスクとをアッシングするアッシング工程と、トレンチ内と連通ホール内に熱処理によりバリヤ層10を形成するバリヤ層形成工程と、異方性エッチングにより連通ホールの底部のバリヤ層と絶縁性バリヤ層とを除去する異方性エッチング工程と、配線シード層12を形成する配線シード層形成工程とを有する。

(もっと読む)

配線基板の製造方法、発光装置及び電子機器

【課題】多層配線構造を有する配線基板において、上層配線の断線等による歩留まりの低下を抑制し、信頼性を向上させることのできる配線基板の製造方法、発光装置及び電子機器を提供する。

【解決手段】配線基板の製造方法は、基板100上に形成されたAl−Ni合金膜102上に保護膜としてMo合金膜104を形成する工程と、Mo合金膜104上にレジスト105を形成する工程と、Al−Ni合金膜102をエッチングして、基板100側の幅がその反対側の幅よりも大きい順テーパ形状を有する信号線Ldを形成する工程と、を備える。

(もっと読む)

配線パターンの形成方法

【課題】触媒層の凝集を抑制し、また炭素の拡散性を制御して、欠陥の無いグラファイト膜を形成することができるグラフェン構造を含むグラファイト膜による配線パターンの形成方法の提供。

【解決手段】触媒層の凝集を抑制し、また炭素の拡散速度を適切に速度に調節することができる合金層又は積層体からなる触媒層を利用して、グラフェン構造を有するグラファイト膜で構成された配線パターンの形成方法を提供する。

(もっと読む)

半導体装置

【課題】抵抗値の温度依存性の小さい抵抗素子を有する半導体装置を提供する。

【解決手段】半導体装置は、金属抵抗素子層Rm1,Rm2を有する。金属抵抗素子層Rm1は、金属抵抗膜層Rm11を含む。金属抵抗素子層Rm2は、金属抵抗膜層Rm12を含む。金属抵抗膜層Rm11は、窒化チタン抵抗および窒化タンタル抵抗のうちの一方であり、金属抵抗膜層Rm12は、窒化チタン抵抗および窒化タンタル抵抗のうちの他方である。窒化チタン抵抗の抵抗値は正の温度係数を有する一方、窒化タンタル抵抗の抵抗値は負の温度係数を有する。コンタクトプラグCP2によって、金属抵抗膜層Rm11と金属抵抗膜層Rm12とが電気的に接続されるので、窒化チタン抵抗の温度係数と窒化タンタル抵抗との温度係数が相殺される。これにより温度係数を小さくすることができる。

(もっと読む)

薄膜トランジスタ基板の製造方法

【課題】透明導電膜にピンホール等の欠陥が生じたとしても金属導電膜の腐食を抑制し、透明導電膜と金属導電膜との間の導通を確実にとることが可能な薄膜トランジスタ基板の製造方法を提供すること。

【解決手段】金属導電膜としてのゲート端子121、ドレイン端子122上にOC−SiN膜109を形成し、ゲート端子121及びドレイン端子122が露出するようにコンタクトホールを形成し、コンタクトホールを介してゲート端子121及びドレイン端子122に接触するようにITO膜を成膜してパターニングし、ITO膜に対して酸化膜形成処理を行う。これにより、ITO膜にピンホール等の欠陥が発生していた場合には、欠陥を介してITO膜下のゲート端子121ドレイン端子122の一部が酸化されて酸化膜が形成される。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体装置の金属配線の平坦化を行う場合、金属配線を下地層に形成した溝に埋め込むと、金属配線の配置をするとき、その変更工程が困難になるという問題があった。また、金属配線に寄生容量がついてしまい、電気信号の遅延などが発生してしまうという問題があった。

【解決手段】本発明の半導体装置の構造は、金属配線下の下地層である絶縁膜を加工して突起部を設ける。この突起部と所定の距離だけ離間して金属配線を設ける。この突起部により、平坦化のための研磨工程でも、不測の余剰研磨が発生しない。また、突起部と金属配線とが離間することにより、金属配線の配置の変更を容易に行うことができると共に、金属配線の寄生容量を低減できる。

(もっと読む)

半導体装置の製造方法

【課題】フォトリソグラフィ工程を行う際に、光が乱反射することを抑制することができる半導体装置の製造方法を提供する。

【解決手段】基板1上に下層配線構成膜2aを形成し、当該下層配線構成膜2aをパターニングして下層配線2を形成する工程と、基板1に下層配線2を覆う層間絶縁膜4を形成し、層間絶縁膜4にビアホールを形成する工程と、スパッタ法により層間絶縁膜4上に第1上層配線構成膜7aを形成する工程と、第1上層配線構成膜7aを形成する工程の温度より高い温度で、第1上層配線構成膜7aをリフローする工程と、リフローする工程より低い温度のスパッタ法により第1上層配線構成膜7a上に第2上層配線構成膜8aを形成する工程と、第2上層配線構成膜8a上に反射防止膜9を成膜する工程と、反射防止膜9上にレジストを形成する工程と、を含む工程を行う。

(もっと読む)

半導体装置の製造方法

【課題】容量コンタクトパッドと容量コンタクトプラグが一体となった構造を形成する。これにより、従来は2回、必要だったフォトリソグラフィ工程を1回に削減して、製造コストを低減する。

【解決手段】半導体装置の製造方法では、層間絶縁膜上に、開口を有するマスクパターンを形成する。このマスクパターンを用いて、層間絶縁膜をエッチングすることにより、開口の下の層間絶縁膜内に容量コンタクトホールを形成する。湿式エッチングにより、マスクパターン内の開口を大きくした後、開口内に導電材料を埋め込むことにより、それぞれ容量コンタクトプラグ及び容量コンタクトパッドを形成する。この後、容量コンタクトパッド上にキャパシタを形成する。

(もっと読む)

半導体装置の作製方法

【課題】簡単な工程で絶縁膜、半導体膜、導電膜等の膜パターンを有する基板を作製する方法、さらには、低コストで、スループットや歩留まりの高い半導体装置の作製方法を提供することを目的とする。

【解決手段】基板上に形成された絶縁膜、半導体膜又は導電膜上に接して第1の膜を形成する工程と、第1の膜上に第1のマスク材料を含有する溶液を吐出して第1の膜上に第1のマスクを形成する工程と、第1のマスクを用いて第1の膜をパターニングして絶縁膜、半導体膜又は導電膜表面上に塗れ性の低い領域と塗れ性の高い領域を形成する工程と、第1のマスクを除去する工程と、塗れ性の低い領域に挟まれた塗れ性の高い領域に、第2のマスク材料を含有する溶液を吐出して第2のマスクを形成する工程と、第2のマスクを用いて、パターニングされた第1の膜をエッチングするとともに絶縁膜、半導体膜又は導電膜をエッチングする。

(もっと読む)

回路基板の製造方法

【課題】印刷法にて、回路基板に容易にヴィアホールを開口できる回路基板の製造方法を提供する事。

【解決手段】基板上に第一導電体を形成する第一導電体形成工程を行い、次に第一導電体を被覆する様に第一絶縁膜を成膜する第一絶縁膜成膜工程を行い、次に第一導電体上の第一絶縁膜に貫通孔32を開口して、第一導電体の表面を露出させる貫通孔形成工程を行い、次に第一導電体の表面を撥液化させる撥液化工程を行い、次に貫通孔32以外の領域に前駆体樹脂を印刷し、印刷後に前駆体樹脂を硬化して第二絶縁膜を形成する第二絶縁膜形成工程を行う。

(もっと読む)

半導体装置の製造方法

【課題】隣接する活性領域の間で横方向に成長するシリコン膜が連結されることを防ぎつつ、活性領域上に十分な厚みのシリコン膜を形成可能とした半導体装置の製造方法を提供する。

【解決手段】ゲート電極6aを挟んだ両側の活性領域5上に第1のシリコン膜12aを選択的にエピタキシャル成長させる工程と、複数のワード配線層WLの各間に第1のシリコン膜12aを覆うのに十分な厚みでマスク絶縁膜を埋め込んだ後、このマスク絶縁膜を第1のシリコン膜12aの表面が露出するまでエッチングにより除去する工程と、第1のシリコン膜12a上に第2のシリコン膜12bを選択的にエピタキシャル成長させる工程とを含む。

(もっと読む)

パターン形成方法及びデバイス製造方法

【課題】露光装置の解像限界よりも微細な非周期的な部分を含むパターンを、露光装置を用いて形成する。

【解決手段】パターン形成方法は、ウエハW上に第1L&Sパターン71を形成し、第1L&Sパターン71を覆うように第1保護層48、周期方向が直交する第2L&Sパターン78、及びフォトレジスト層60を形成し、第2L&Sパターン78の一部と重なるように、フォトレジスト層60に第1開口部60A,60Bを有する第3パターンを形成し、第1開口部60A,60Bを介して第1保護層48に第2開口部48A,48Bを形成し、第2開口部48A,48Bを介して第1L&Sパターン71の一部を除去する。

(もっと読む)

半導体装置の製造方法

【課題】深さが深く幅が狭い溝の深さを把握できる半導体装置の製造方法を提供する。

【解決手段】半導体基板1に平面視環状の複数の環状溝2を形成する環状溝形成工程と、環状溝2の下端よりも下層に配置された半導体基板1を介して、複数の環状溝2から選ばれた第1環状溝2aの平面視内側表面と、第1環状溝2aとは別の環状溝2である第2環状溝2bの平面視内側表面との間の抵抗を測定し、実測抵抗値を得る抵抗測定工程と、実測抵抗値を用いて環状溝2の深さを算出する算出工程とを備える半導体装置の製造方法とする。

(もっと読む)

半導体基板の処理方法及び半導体装置の製造方法

【課題】半導体基板の裏面研削後にスパッタリング法を含む方法で導電膜を形成する際に、研削時に半導体基板を支持体に固定する接着剤の基板外周部のはみ出した部分から放電現象の発生を防止する。

【解決手段】半導体基板1の裏面研削後、導電膜の成膜を実施する前に、基板端部E1と接着剤との隙間d1を所定値以上にするために、基板端部又は接着剤の少なくとも一方を除去する。

(もっと読む)

201 - 220 / 1,968

[ Back to top ]