Fターム[5F033QQ18]の内容

半導体集積回路装置の内部配線 (234,551) | パターン形成方法,基板,導電膜,絶縁膜の処理方法 (47,095) | エッチング (29,543) | ドライエッチング (6,179) | 等方性エッチング (193)

Fターム[5F033QQ18]に分類される特許

1 - 20 / 193

半導体装置およびその製造方法

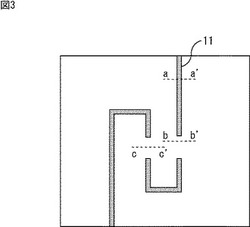

【課題】同一レイヤに成膜された後、複数回のエッチングにより形成された導電性被加工物を、下地層に段差を作ることなく、異なる電位に固定する。

【解決手段】同一レイヤに成膜された後、複数回のエッチングにより線状に形成された導電性被加工物を備え、導電性被加工物は、自身を電気的に分断する2以上の分断部分を有し、分断部分における導電性被加工物は、その一部が平行になるように形成されており、平行に形成された部分の少なくとも一方は分断されている。複数回のエッチングに用いられるレジストパターンのうちの、所定回数目のエッチングに用いられる第1のレジストパターンと、他の回数目のエッチングに用いられる第2のレジストパターンとが重なる領域の、平行に形成された部分に対応する箇所の幅は、エッチングによる導電性被加工物の後退量より小さい。本技術は、半導体装置に適用することができる。

(もっと読む)

半導体装置およびその製造方法

【課題】リーク不良の発生を抑制でき、かつ薄型基板を用いることができる半導体装置およびその製造方法を提供する。

【解決手段】半導体チップ30を、半導体基板35の表層部に形成された第1導電型層34と、第1導電型層34の表面に形成されたゲート絶縁膜37と、ゲート絶縁膜37上に形成されたゲート電極38と、半導体基板35の主表面35a上に配置され、主表面35aの一部を露出させるコンタクトホール42が形成された層間絶縁膜41と、層間絶縁膜41上に配置され、コンタクトホール42を介して半導体基板35と接続されるアルミニウムを有する材料で構成される上部電極43と、上部電極43上に形成されたニッケルを有する材料で構成されるメッキ膜44と、半導体基板35の裏面35bに形成された下部電極46とを有する構成とする。そして、上部電極43のうちコンタクトホール42に形成されている部分の膜厚tを2μm以上にする。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】メモリセルアレイと周辺回路との間のアレイ端パターンにおける耐圧を向上させる。

【解決手段】浮遊ゲートは半導体基板上の第1の絶縁膜上に設けられる。ゲート間絶縁膜は浮遊ゲート上に、制御ゲートはゲート間絶縁膜上に設けられる。メモリセルは、第1の絶縁膜、浮遊ゲート、ゲート間絶縁膜および制御ゲートを含む。周辺回路はメモリセルアレイの周辺に設けられる。第1のダミーセルは、第1の絶縁膜、浮遊ゲート、ゲート間絶縁膜および制御ゲートを含み、メモリセルアレイの端に設けられる。第2のダミーセルは、第1の絶縁膜よりも厚い第2の絶縁膜を含み、第1のダミーセルと周辺回路との間に設けられる。第1のダミーセルにおいて、ゲート間絶縁膜および制御ゲートは浮遊ゲートの上面および2つの側面に設けられる。

(もっと読む)

半導体装置、及びその製造方法

【課題】絶縁破壊が発生しにくい半導体装置及びその製造方法を提供する。

【解決手段】集積回路13と電気的に接続する電極14が位置する半導体基板10を用意する。半導体基板の前記第1の面11とは反対側の第2の面12において等方性エッチングを行い、第1内壁面を有する第1凹部を形成する。第1凹部内から前記半導体基板を貫通して電極に至り、第2内壁面22aを有する第2凹部を形成する。第2の面と第1内壁面によって形成された第1の角部、及び第1内壁面と第2内壁面によって形成された第2の角部を除去するエッチバック処理を行い、第2の面と第2内壁面とを連続する第1内壁面を形成する。角部を除去した後、少なくとも第1内壁面、及び第2内壁面を覆うように、電極とオーバーラップする位置に開口部65を有する絶縁層30を形成する。絶縁層を介して第2凹部内に充填され、電極と接続し、かつ第2の面から突出する導電部40を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、小型化を図ることが可能になると共に、絶縁リングで囲まれた貫通電極を狭ピッチで配置することの可能な半導体装置及びその製造方法を提供することを課題とする。

【解決手段】回路素子層5が形成される表面1a、及び裏面1bを有する半導体基板1と、半導体基板1を貫通し、かつ半導体基板1の表面1a側から半導体基板1の裏面1b側に向かうにつれて幅が広くなる貫通電極7と、貫通電極7を囲むように半導体基板を貫通し、かつ半導体基板1の表面1a側から半導体基板1の裏面1b側に向かうにつれて幅が狭くなる第1の絶縁リング3と、を有し、半導体基板1の厚さ方向Aにおいて、第1の絶縁リング3の少なくとも一部と対向するように貫通電極7を配置する。

(もっと読む)

半導体装置の製造方法

【課題】本願発明者らが、プラズマ処理等による半導体ウエハのチャージアップの影響を検討したところによると、半導体ウエハ等にドライエッチング等を施すと、通常、その結果として、半導体ウエハは、主に電気的に正側に偏った不均一な帯電状態となることが明らかとなった。これは、ドライエッチング等によって、正の可動イオン等がウエハの表面やその近傍に残存し、不均一に分布していることを示すものであり、個々の半導体チップとされた後も残存して、動作に悪影響を及ぼす恐れがある。

【解決手段】本願発明は、通常、ポリマー除去液等を使用する必要のないメタル膜加工工程に於いて、加工用レジスト膜の除去後、ポリマー除去液類似の導電性処理液との摩擦により、ウエハ全体を負に帯電させるものである。

(もっと読む)

半導体装置及びその製造方法

【課題】高アスペクト比の溝内にカバレッジ性良く絶縁膜を埋め込むと表面にスリット状の空孔が形成され、CMPで平坦化すると、CMPで用いた組成物や、研磨された除去物、その他の残渣が空孔内に残り易く、この残渣は後の工程での発塵の一原因となり得る。

【解決手段】基板1の第1の主面に、俯瞰形状が環状となる第1の溝部2Tを形成し、第1の主面全面に第1の絶縁膜2aを形成し、第1の絶縁膜2aの表面から前記第1の溝部の内部まで達する深さの空孔を残しつつ、前記第1の絶縁膜を第1の溝部に埋め込み、空孔内を埋め込むように第1の絶縁膜上に第2の絶縁膜を形成し、第1の溝部内に第1の絶縁膜および第2の絶縁膜を残しつつ、基板表面高さまで化学機械研磨法により平坦化する。

(もっと読む)

ドライエッチング方法

【課題】本発明は、ダミー材料の除去により形成される溝や孔に容易にトップラウンドを設けることができるドライエッチング方法を提供する。

【解決手段】本発明は、層間酸化膜に周囲を囲まれたダミー材料を除去することにより溝または孔を形成するドライエッチング方法において、前記ダミー材料を所定の深さまでエッチングし、前記エッチング後に等方性エッチングを行い、等方性エッチング後に前記ダミー材料の残りを除去することを特徴とするドライエッチング方法である。

(もっと読む)

不揮発性半導体記憶装置の製造方法

【課題】選択ゲートトランジスタのゲート電極間の間隔の縮小を実現する不揮発性半導体記憶装置の製造方法を提供する。

【解決手段】実施の形態の不揮発性半導体記憶装置の製造方法は、半導体基板に、複数の第1の素子領域と、素子分離領域と、第2の素子領域を形成する。第1の素子領域上に、メモリセルゲート電極、2本の選択ゲート電極を形成し、第2の素子領域に周辺ゲート電極を形成する。第1の絶縁膜を形成し、周辺ゲート電極の側壁部上が開口される第1のレジストパターンを形成し、第1のエッチング処理を行い、側壁絶縁膜を形成する。第2のレジストパターンを形成し、第2のエッチング処理を行い、選択ゲート電極側壁部の第1の絶縁膜を除去する。第2の絶縁膜を堆積し、第3の絶縁膜を堆積する。2本の選択ゲート電極間上が開口される第3のレジストパターンを形成し、第3のエッチングおよび第4のエッチング処理を行い、コンタクトホールを形成する。

(もっと読む)

半導体チップ及び半導体装置の製造方法

【課題】半導体チップの小型化を維持して半導体装置の組み立てのワイヤボンディング性を向上させる。

【解決手段】プローブピンを接触させるプローブ接触面6dとワイヤ5を接続するワイヤ接続面6eとが形成され、さらにプローブ接触面6dは主面6aに対して傾斜した面であり、かつワイヤ接続面6eはプローブ接触面6dと異なった角度の面である電極パッド6cを備えたメモリチップ6と、メモリチップ6が搭載されたタブ2cと、複数のインナリード2a及びアウタリード2bと、メモリチップ6の電極パッド6cのワイヤ接続面6eとインナリード2aとを接続する複数のワイヤ5とを有している。

(もっと読む)

半導体装置の製造方法と半導体装置

【課題】半導体基板の表面のAl層の表面が荒れることを抑制しつつ、リフトオフの後に溶解層が剥離せずに残ることを防止し得る半導体装置の製造方法を提供する。

【解決手段】半導体基板12の表面にAl層14を形成し、Al層14の表面にTiN層16を形成し、TiN層16の表面の一部に絶縁層20を形成し、TiN層16と絶縁層20の表面に溶解層を形成し、溶解層の表面にレジスト層を形成し、溶解層とレジスト層の一部を除去して溶解層開口部を形成してTiN層16の一部を露出させ、レジスト層の表面、及び、露出したTiN層16の一部の表面にTi層30及びNi層40を形成し、アルカリ溶液によって溶解層を溶解させることにより、溶解層とともに、レジスト層とその表面に形成されたTi層及びNi層を除去する。

(もっと読む)

導電性ビアの製造と充填のための方法、およびそのように形成された導電性ビア

【課題】ビアホール表面上の絶縁コーティングとビアホール内に挿入される導電材料との付着性を向上する。

【解決手段】導電性ビアを形成する方法は、一つ以上のビアホールを基板内に形成するステップを含む。ビアホールは、単一マスク、保護層、ボンドパッド、もしくは、エッチングプロセスの間にフォトマスクが除去される場合にハードマスクとして機能する、基板のその他のフィーチャで形成され得る。ビアホールは、その表面に低誘電率(低K)誘電材料を含む誘電体コーティングの付着を促進するように構成されてもよい。障壁層が各ビアホールの表面の上に形成されてもよい。種材料(seed material)を含み得るベース層は、その後のビアホールの表面上の導電材料の選択的堆積を促進するように形成されてもよい。

(もっと読む)

高密度配線構造及びその製造方法

【課題】従来の製造方法と比べて、少ない工程数で形成可能であり、また、高精度の位置合わせ技術を必要としない、配線構造とその製造方法を提供する。

【解決手段】基板10の主表面10a上に、スペーサ絶縁膜20を形成する。次に、スペーサ絶縁膜をパターニングして、下部配線形成領域42の基板の主表面を露出させる。次に、露出した基板の主表面上、及び、スペーサ絶縁膜22の上側表面22a上に配線材料を堆積させて、基板の主表面上に下部配線52を形成するとともに、スペーサ絶縁膜の上側表面上に上部配線50を形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】配線部を通じた信号伝搬速度を向上できるようにした半導体装置およびその製造方法を提供する。

【解決手段】半導体装置は、半導体基板上に形成された第1絶縁膜と、前記第1絶縁膜上に形成された、前記第1絶縁膜より比誘電率が高い第2絶縁膜と、前記第2絶縁膜と隣接する側面が順テーパ形状を有し、前記第1絶縁膜および前記第2絶縁膜を貫通して形成された複数の縦柱状プラグと、前記第2絶縁膜上に形成された、前記第2絶縁膜よりも比誘電率が低い第3絶縁膜と、前記複数の縦柱状プラグの上部に到達するように前記第3絶縁膜に形成された複数の溝と、前記複数の溝内にそれぞれ形成され、前記複数の縦柱状プラグの上部に一部がそれぞれ接触する金属からなる複数の配線部と、を備える。

(もっと読む)

半導体装置およびその製造方法

【課題】SOGで平坦化した半導体装置であっても水分による閾値変動を抑制した半導体装置を提供する。

【解決手段】SOG平坦化後にSOGを除去したMOSトランジスタ領域を単層配線とし、SOGを残した非MOSトランジスタ領域を多層配線とすることで、SOGを介したMOSトランジスタへの水分の影響が無くなり、MOSトランジスタの閾値変動を抑制できる。

(もっと読む)

半導体装置、電子デバイス及び電子デバイスの製造方法

【課題】対向するバンプ、パッド等を良好に接続し、接続部分の水平強度を高めるための半導体装置を提供する。

【解決手段】半導体基板2の上方に形成される第1絶縁膜15と、第1絶縁膜15内に形成される導電パターン19と、第1絶縁膜15上に形成される第2絶縁膜21と、第2絶縁膜21内に形成され、導電パターン19に接続されるビアプラグ24と、記ビアプラグ24の上に接続され、開口部25aを有する電極パッド25と、第2絶縁膜21内でビアプラグ24の周辺に形成される内部空間21aとを有し、電極パッド25上面及び開口部25a内には外部の突起状電極58が接続される。

(もっと読む)

半導体装置

【課題】配線及びビア間接続の信頼性を向上させた半導体装置を提供する。

【解決手段】実施形態に係る半導体装置は、半導体基板と、前記半導体基板上の異なる高さに配置され、配線が形成された複数の配線層と、前記配線層の積層方向に延びる柱状に形成され、異なる複数の前記配線層の配線間を電気的に接続するビアとを備える。前記配線の一部は、前記ビアの中間部において前記ビアに接触する中間配線であり、所定の前記配線層の中間配線は、前記ビアを前記積層方向に直交する方向で貫通し、且つ、上面、下面及び両側面において前記ビアと接触していることを特徴とする。

(もっと読む)

固定された導電性ビアおよびその製造方法

【課題】導電性ビアおよびそれを形成する方法に関する。

【解決手段】導電性ビアが、導電性接触構造と該導電性接触構造上に配置された誘電体層の突出部との間に配置された部分を含む。1つの実施形態において、突出部は、導電性接触構造上にアンダーカット層を形成し、次に、該導電性接触構造およびアンダーカット層上に誘電体層を形成することによって形成される。誘電体層に空洞を形成し、誘電体層の突出部を形成するようにアンダーカット層の材料が該空洞を通して除去される。導電性ビアの導電性材料は次に、突出部の下および空洞に形成される。

(もっと読む)

半導体装置及びその製造方法

【課題】ヒートシンクに生じる不具合を低減すること。

【解決手段】半導体装置は、第1面及び第2面を有し、第1面と第2面とを貫通するバイアホールを有する半導体基板と、第1面上に、バイアホールの開口と少なくとも部分的に重複するように形成された配線又は電極と、第2面上に形成され、バイアホールの開口と少なくとも部分的に重複する開口を有する応力緩衝層と、応力緩衝層上からバイアホールの内壁面に沿って延在し、配線又は電極と電気的に接続されたヒートシンクと、を備える。バイアホールの第2面における開口の大きさは、第1面における開口の大きさよりも大きい。応力緩衝層の熱膨張係数は、ヒートシンクの熱膨張係数未満である。

(もっと読む)

半導体装置の作製方法

【課題】コンタクトホールを微細化する。この時、微細化されたコンタクトホールであっても、半導体装置における電極のコンタクトを確実なものとする。

【解決手段】珪化膜と樹脂材料膜とからなる多層の層間絶縁膜を形成する。その後、コンタクトホールを形成する。このとき、珪化膜に設けられるコンタクトホールの大きさを樹脂材料膜に設けられるコンタクトホールの大きさよりも小さくする。このような構成は、パターンが複雑化してもコンタクトのとりやすいものとすることができる。

(もっと読む)

1 - 20 / 193

[ Back to top ]