Fターム[5F033RR04]の内容

半導体集積回路装置の内部配線 (234,551) | 絶縁膜の材料 (22,565) | 無機材料 (16,592) | 酸化物 (6,040) | SiO2 (5,243)

Fターム[5F033RR04]に分類される特許

141 - 160 / 5,243

貫通配線基板および貫通配線基板の製造方法

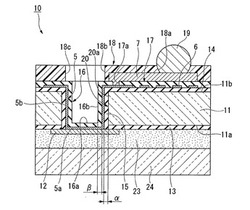

【課題】貫通孔内に形成された導電層に加わる応力を抑制できるとともに、導電層からの効果的な放熱も促すことができる貫通配線基板、及びこの貫通配線基板の製造方法を提供する。

【解決手段】半導体基板11(基板)の一方の面11aに配された電極層12と、電極層12の少なくとも一部が露呈するように半導体基板11内に開けられた貫通孔20と、貫通孔20の内側面20aを覆い、電極層12の少なくとも一部が露呈するように配された第一絶縁層15と、第一絶縁層15を介して、貫通孔20の内側面20a及び電極層12の露呈部を覆うように配され、電極層12と電気的に接続された導電層5と、導電層5を覆うように配された第二絶縁層16と、を少なくとも備えてなる貫通配線基板10であって、第二絶縁層16は、導電層5の表面形状に沿って形成されていることを特徴とする。

(もっと読む)

低抵抗及び低インダクタンスの裏面貫通ビア及びその製造方法

【課題】裏面コンタクト構造体及びその構造体を製造する方法を提供する。

【解決手段】表面及び対向する裏面を有する基板100の表面上に第1誘電体層105を形成することと、第1誘電体層を貫通して前記基板の表面にまで延びる導電性の第1スタッド・コンタクト140Bを第1誘電体層内に形成することと、基板の裏面から基板を薄くして基板の新しい裏面を形成することと、基板の新しい裏面から前記第1誘電体層まで延びるトレンチ165を基板内に形成して第1スタッド・コンタクトの底面をトレンチ内に露出させることと、基板の新しい裏面、トレンチの側壁、第1誘電体層の露出面、及び第1スタッド・コンタクトの露出面の上に、トレンチを完全に充填するのに十分には厚くない共形導電層170、175を形成することと、を含む前記方法。

(もっと読む)

銅膜作製方法

【課題】下地層との密着性に優れた銅膜を製造する方法の提供。

【解決手段】成膜対象物上に下地層としてチタン膜を形成した後、この下地層を水素ガス雰囲気中で100℃以上200℃未満の温度で熱処理し、次いでその上に銅膜を作製する。このように銅膜を作製した後、さらに水素ガス雰囲気中で100℃以上200℃未満の温度で熱処理を行う。

(もっと読む)

不揮発性半導体記憶装置およびその製造方法

【課題】シリサイド工程によるゲート絶縁膜の金属汚染や、メモリセルのショートチャネル効果を抑制する。

【解決手段】実施形態によれば、不揮発性半導体記憶装置は、半導体基板と、前記半導体基板上に順に形成された第1絶縁層、電荷蓄積層、第2絶縁層、および制御電極を有し、前記電荷蓄積層の側面が傾斜面を有する複数のメモリセルトランジスタとを備える。さらに、前記装置は、前記メモリセルトランジスタの側面と、前記メモリセルトランジスタ間の前記半導体基板の上面に形成された第1の絶縁膜部分と、前記メモリセルトランジスタ間のエアギャップ上と前記メモリセルトランジスタ上に連続して形成された第2の絶縁膜部分と、を有する1層以上の絶縁膜を備える。さらに、前記メモリセルトランジスタ間の前記半導体基板の上面から前記エアギャップの下端までの第1距離は、前記メモリセルトランジスタの側面に形成された前記絶縁膜の膜厚よりも大きい。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、小型化を図ることが可能になると共に、絶縁リングで囲まれた貫通電極を狭ピッチで配置することの可能な半導体装置及びその製造方法を提供することを課題とする。

【解決手段】回路素子層5が形成される表面1a、及び裏面1bを有する半導体基板1と、半導体基板1を貫通し、かつ半導体基板1の表面1a側から半導体基板1の裏面1b側に向かうにつれて幅が広くなる貫通電極7と、貫通電極7を囲むように半導体基板を貫通し、かつ半導体基板1の表面1a側から半導体基板1の裏面1b側に向かうにつれて幅が狭くなる第1の絶縁リング3と、を有し、半導体基板1の厚さ方向Aにおいて、第1の絶縁リング3の少なくとも一部と対向するように貫通電極7を配置する。

(もっと読む)

電極構造、半導体素子、半導体装置、サーマルヘッドおよびサーマルプリンタ

【課題】シェア強度の向上した電極構造を提供する。

【解決手段】電極構造C1は、基体2と、基体2上に設けられた電極4と、電極4上に設けられためっき層14とを備え、めっき層14は、第1部位14aと、第1部位14a上に位置する第2部位14bとを有しており、平面視して、第1部位14aの面積が第2部位14bの面積よりも大きいことから、電極構造C1のシェア強度を向上させることができ、シェア強度の向上した電極構造を提供することができる。

(もっと読む)

ヒューズ、半導体装置、半導体装置の製造方法

【課題】高電圧が不要で安定した状態を得ること。

【解決手段】半導体装置10に形成されたヒューズ素子11は、概略的に、拡散領域22と、拡散領域22と一部重なるように拡散領域22より上方に形成された導電体25を含む。半導体装置10の半導体基板21には、拡散領域22が形成されている。半導体基板21には素子分離領域23が形成されている。拡散領域22を含む半導体基板21上には絶縁膜24が形成されている。絶縁膜24上には、導電体25が形成されている。導電体25上には、カバー膜26が形成されている。カバー膜26は、導電体25の上面及び側面を覆うように形成されている。カバー膜26は、絶縁膜24より高い引っ張り応力を持つ。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】露光光源として真空紫外光を用いるホトリソ技術のパターン解像限界より微細な拡散抵抗を製造することはできないから、高抵抗の拡散抵抗は実現できなかった。

【解決手段】一組の薄膜構造体の対向する間隔に、サイドウォール形成用の絶縁膜を形成する際に生じる空隙を利用して露光光源として真空紫外光を用いるホトリソ技術のパターン解像限界より微細な拡散抵抗を形成する。薄膜構造体を配線抵抗として利用すれば、これらを接続して設けることにより温度特性に優れる抵抗素子を構成することもできる。

(もっと読む)

半導体ウェハ及びその製造方法

【課題】スクライブ線領域におけるダミーパターンが影響して配線形成の際に露光時のアライメント波形検出精度を低下させるおそれがあった。

【解決手段】複数の素子形成領域と、素子形成領域を相互に区画するスクライブ線領域と、素子形成領域において半導体基板上に配置された複数のパターンと、スクライブ線領域において半導体基板上に配置されるとともに、パターンと同様な構成の複数のダミーパターンと、パターン及びダミーパターンを含む半導体基板上に形成されるとともに、上面が平坦化された層間絶縁膜と、スクライブ線領域における層間絶縁膜に形成されるとともに、ダミーパターンと重ならない領域にて半導体基板に通じないように形成された穴状のアクセサリパターンと、を備える。

(もっと読む)

不揮発性半導体記憶装置の製造方法および不揮発性半導体記憶装置

【課題】メモリセルトランジスタのゲート電極間の空隙の形状を最適化し、高性能、高信頼性を実現する不揮発性半導体記憶装置の製造方法。

【解決手段】実施の形態の不揮発性半導体記憶装置の製造方法は、半導体基板上に、第1のゲート絶縁膜、第1のフローティングゲート電極、第1のゲート間絶縁膜、第1のコントロールゲート電極、第1のゲートマスク絶縁膜の積層構造を有する複数のメモリセルゲート電極を形成する。メモリセルゲート電極の側壁部に保護膜を形成し、その一部を第1のコントロールゲート電極の側壁部の一部が露出するよう除去する。金属膜を形成し、熱処理により、金属膜と第1のコントロールゲート電極を反応させ第1の金属半導体化合物層を形成する。メモリセルゲート電極間を埋め込み、内部に空隙を有する層間絶縁膜であって、第1のコントロールゲート電極の上面よりも半導体基板から離れた位置に空隙の上端が位置する層間絶縁膜を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体基板における抵抗やコンタクト抵抗を低減させた半導体装置及びその製造方法を提供すること。

【解決手段】半導体装置は、シリコン層と、シリコン層に形成され、第1不純物を含有する金属シリサイド層と、を備える。シリコン層は、金属シリサイド層が形成されていない領域において、第1不純物に起因するエンド・オブ・レンジ欠陥を有していない。

(もっと読む)

半導体装置の製造方法

【課題】本願発明者らが、プラズマ処理等による半導体ウエハのチャージアップの影響を検討したところによると、半導体ウエハ等にドライエッチング等を施すと、通常、その結果として、半導体ウエハは、主に電気的に正側に偏った不均一な帯電状態となることが明らかとなった。これは、ドライエッチング等によって、正の可動イオン等がウエハの表面やその近傍に残存し、不均一に分布していることを示すものであり、個々の半導体チップとされた後も残存して、動作に悪影響を及ぼす恐れがある。

【解決手段】本願発明は、通常、ポリマー除去液等を使用する必要のないメタル膜加工工程に於いて、加工用レジスト膜の除去後、ポリマー除去液類似の導電性処理液との摩擦により、ウエハ全体を負に帯電させるものである。

(もっと読む)

集積回路装置の作製方法

【課題】薄膜回路の下方に外部と接続するための電極を容易に形成できる薄膜回路部品の

構造及び薄膜回路部品の作製方法を提供することを課題とする。

【解決手段】第1の絶縁膜と、第1の絶縁膜の一方の面上に形成された薄膜回路と、薄膜

回路上に形成された第2の絶縁膜と、第2の絶縁膜上に形成された電極と、電極上に形成

された樹脂膜とを有する積層物を形成し、積層物の第1の絶縁膜の他方の面側に、電極と

重なるように導電膜を形成し、導電膜にレーザーを照射する。

(もっと読む)

半導体装置およびその製造方法

【課題】同一平面上に形成された2つの配線が互いにショートするのを回避すること。

【解決手段】第1の方向(X)に複数本並べて配置された活性領域(50)の各々は、第1の方向(X)と直交する第2の方向(Y)に離間して配置された2つの縦型トランジスタ(51)と、この2つの縦型トランジスタ(51)の間に位置する縦型のゲート電極用ダミーピラー(1a)と、から成る。半導体装置(100)は、複数本の活性領域(50)の中央に位置するゲート電極用ダミーピラー(1a)へ給電するために第1の方向(X)へ延在して配置されたゲート給電配線(23)と、2つの縦型トランジスタ(51)間を接続するために、第2の方向(Y)に延在し、かつゲート給電配線(23)を迂回するように構成されたトランジスタ間接続配線(21、10A、16)と、を備える。

(もっと読む)

半導体装置及びその製造方法

【課題】高品質な配線を有する半導体装置を提供する。

【解決手段】第1の領域100及び第2の領域200に設けられた第1の絶縁層10と、第1の領域に設けられた第1の絶縁層上に形成された第2の絶縁層11aと、第2の領域200に設けられた第1の絶縁層上に形成され、第2の絶縁層と略同一の高さを有する第3の絶縁層11cと、第1の領域に設けられた第1の絶縁層上及び第2の絶縁層の両方の側壁に形成された第1の配線層13aと、第2の領域に設けられた第1の絶縁層上、及び第3の絶縁層の上面及び側壁上に形成された第2の配線層13bと、第1の絶縁層、第2の絶縁層、第1の配線層、及び第2の配線層を覆う第4の絶縁層15と、第1の領域に設けられた第4の絶縁層内に形成され、第1の配線層に接続された第1のコンタクトプラグ17aと、第2の領域に設けられた第4の絶縁層内に形成され、第2の配線層に接続された第2のコンタクトプラグ17bと、を備える。

(もっと読む)

成膜方法、これを含む半導体装置の製造方法、成膜装置、及び半導体装置

【課題】柱状形状を有し密に配列される電極の倒壊を防ぐことが可能な半導体装置を提供する。

【解決手段】電界効果トランジスタと、柱状形状を有するキャパシタとを有する半導体装置であって、前記電界トランジスタの不純物拡散領域と電気的に接続し、柱状形状を有する第1の電極と、前記第1の電極の少なくとも側面に形成される誘電体膜と、前記誘電体膜上に形成される第2の電極と、前記柱状形状を有する前記第1の電極の長手方向と交差する方向に延び、前記第2の電極の少なくとも一部を貫通して前記第1の電極を連結するホウ素添加窒化シリコン膜により形成される支持膜とを備える半導体装置により、上記の課題が達成される。

(もっと読む)

半導体装置およびその製造方法

【課題】トランジスタ間接続配線が吊りワード線と短絡してしまうのを回避すること。

【解決手段】第1の方向(X)に複数本並べて配置された活性領域(50)の各々は、第1の方向(X)と直交する第2の方向(Y)に離間して配置された2つの縦型トランジスタ(51)と、この2つの縦型トランジスタ(51)の間に位置するピラー(1a)と、から成る。半導体装置(100)は、複数本の活性領域(50)の中央の位置で、第1の方向(X)へ延在して配置された吊りワード線(23)と、2つの縦型トランジスタ(51)間を接続するために、第2の方向(Y)に延在し、かつ吊りワード線(23)を迂回するように構成されたトランジスタ間接続配線(21、10A、16)と、を備える。

(もっと読む)

貫通配線付き接合基板

【課題】貫通孔内に配した樹脂が熱膨張することによって電極を破損することを防止した貫通配線付き接合基板の提供。

【解決手段】

一面1aに電極層2が形成された第一基板1、及び電極層2と接合樹脂層3を介して、第一基板1と接合された第二基板4とを備えた貫通配線付き接合基板10Aであって、第一基板1の他面1b側から電極層2が露出するまで第一基板1を貫通する貫通孔5と、貫通孔5の内部において、貫通孔5の内側面5c及び電極層2を覆う貫通配線層6と、貫通配線層6を覆い貫通孔5の内部に充填された充填樹脂部7とを有し、充填樹脂部7を構成する樹脂のヤング率は、接合樹脂層3を構成する樹脂のヤング率よりも小さいことを特徴とする貫通配線付き接合基板10A。

(もっと読む)

半導体装置、半導体装置の製造方法、及び、電子機器

【課題】基板を貼り合わせて電極接合を行う半導体素子において、電極の腐食を防ぐ半導体装置の製造方法を提供する。

【解決手段】第1接合部40と第2接合部60とが電極形成面を対向させて接合された半導体装置において、第1接合部40の絶縁層51と、絶縁層51の表面に形成された接合電極41と、絶縁層51表面に形成され、絶縁層51を介して接合電極41の周囲を囲む保護層44とを備える。さらに第2接合部60の絶縁層71と、絶縁層71の表面に形成された接合電極61と、絶縁層71表面に形成され、絶縁層71を介して接合電極61の周囲を囲む保護層64とを備える。

(もっと読む)

集積回路構造及び裏面照射型イメージセンサデバイス

【課題】裏面照射(BSI)型イメージセンサチップのパッド構造を提供する。

【解決手段】前面及び背面を含む半導体基板、前記半導体基板の前記前面に配置される低k誘電体層、前記低k誘電体層に配置される非低k誘電体層、前記非低k誘電体層に配置される金属パッド、前記半導体基板の背面から延伸し、前記半導体基板、前記低k誘電体層、及び低k誘電体層を貫通し、前記金属パッドの表面を露出する開口、及び前記開口の側壁及び底部上に形成され、前記開口の底部は、前記金属パッドの前記露出された表面を部分的に覆う保護層を含む集積回路構造。

(もっと読む)

141 - 160 / 5,243

[ Back to top ]