Fターム[5F033RR29]の内容

半導体集積回路装置の内部配線 (234,551) | 絶縁膜の材料 (22,565) | 気孔、空洞等、一部空気を混入させたもの (1,009)

Fターム[5F033RR29]に分類される特許

61 - 80 / 1,009

多相超低誘電膜の形成方法

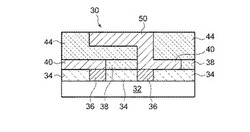

【課題】誘電率が2.7以下であり、弾性計数および硬度の改善等、機械的特性を向上させた超低誘電率(k)膜、および膜の製造方法を提供する。

【解決手段】多相超低k誘電膜44は、Si、C、O、およびHの原子を含み、誘電率が約2.4以下であり、ナノサイズの孔または空隙を有し、弾性係数が約5以上であり、硬度が約0.7以上である。好適な多相超低k誘電膜44は、Si、C、O、およびHの原子を含み、誘電率が約2.2以下であり、ナノサイズの孔または空隙を有し、弾性係数が約3以上であり、硬度が約0.3以上である。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、ゲート電極の幅を十分に確保して、ゲート電極の抵抗値を小さくすることが可能で、かつゲート電極間の容量を小さくすることの可能な半導体装置及びその製造方法を提供することを課題とする。

【解決手段】半導体基板に設けられ、Y方向に延在する第1の溝15と、半導体基板に設けられ、第1の溝15と交差するXの方向に延在する第2の溝25と、第1及び第2の溝15,25に囲まれ、第2の溝25に露出された対向する第1及び第2の側面26a,26bを有するピラー26と、ゲート絶縁膜28を介して、ピラー26の第2の側面26bに接触するように、第2の溝25の下部に設けられた1つのゲート電極29と、ゲート電極29の側面とピラーの第1の側面26aとの間に配置された空隙と、を有する。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】周辺回路における回路動作の遅延を低減できる不揮発性半導体記憶装置を提供する。

【解決手段】半導体基板11上に所定間隔を空けて形成され、ゲート絶縁膜1、浮遊ゲート電極2、ゲート間絶縁膜3、及び制御ゲート電極4をそれぞれ有する複数のメモリセルMCと、メモリセルMCの浮遊ゲート電極2の側面、ゲート間絶縁膜3の側面、及び制御ゲート電極4の側面に形成され、空隙を有する側壁絶縁膜18Bと、基板11上に形成され、ゲート絶縁膜1、第1ゲート電極2、ゲート間絶縁膜3、及び制御ゲート電極4を有する周辺トランジスタPTと、周辺トランジスタPTの第1ゲート電極2の側面、ゲート間絶縁膜3の側面、及び制御ゲート電極4の側面に形成され、空隙19Aを有する側壁絶縁膜18Aとを備える。基板11上の最も低い位置にある空隙19Aの上端は、ゲート間絶縁膜3より基板11上の低い位置にある。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】 デュアルダマシン法を用いる配線形成方法で、特に最上層の配線を含む上層配線を形成する場合、接続孔の周囲に生ずるクラウンフェンスを容易に除去して信頼性の高い半導体装置を提供する。

【解決手段】 接続孔19a、19b上に形成された開口を有するマスク層21をマスクとして、第3絶縁膜17および第3絶縁膜17より密度の小さい、あるいは比誘電率が小さい第2絶縁膜16をエッチングして配線溝22を形成すると、接続孔19bに埋め込まれた有機性材料20の突出部と同時に、第2絶縁膜16の構成材料を主成分とするクラウンフェンス23が生ずる。これに対しマスク層21の除去工程を兼ねるなどの処理において、少なくとも配線溝22の内部にプラズマ処理を施した後、第2絶縁膜16を溶解可能な処理液で処理し上記のプラズマ処理で変質したクラウンフェンス25を選択的に除去する。

(もっと読む)

半導体装置の製造方法

【課題】 半導体装置の多層配線において配線間隔を低減させても所定の低比誘電率を維持できるとともに、電気的特性の劣化などを抑制できる多孔性の層間絶縁膜の形成方法を提供する。

【解決手段】 半導体基板1上に形成される配線構造を構成し、空孔を有する多孔性絶縁膜13を得るための母体となる母体絶縁膜を気相成長法を用いて堆積する。この際、多孔性絶縁膜13の比誘電率、配線20間の間隔や絶縁耐圧のような、配線構造を決める因子に要求される設計値に応じて、多孔性絶縁膜13の分子骨格形成材料の流量に対する多孔性絶縁膜13の空孔形成材料の流量の比の、少なくとも範囲をまず決定する。この後、決定した流量比の範囲で母体絶縁膜を堆積し、この母体絶縁膜に熱や紫外線などのエネルギーを与えて空孔を有する多孔性絶縁膜13にする。

(もっと読む)

グラフェン配線およびその製造方法

【課題】配線構造における電気特性の向上を図る。

【解決手段】グラフェン配線の製造方法は、絶縁膜13内に、配線溝30を形成し、前記配線溝内の全面に、触媒膜14を形成し、前記配線溝内の前記触媒膜上に、前記配線溝の底面に対して垂直方向に積層された複数のグラフェンシート16a〜16eで構成されるグラフェン層16を形成することを具備する。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の配線間の容量低減を実現するとともに、ミスアライメント・ビアを対策する。

【解決手段】配線上及び配線間のスペース領域に絶縁膜74を形成し、隣接配線間隔が狭い配線の上面を露出するスルーホールの周辺領域の絶縁膜74をリザーバーとして残して、周辺領域以外の絶縁膜74を除去し、絶縁膜74が除去された配線間のスペース領域に空隙を残しつつ、配線上に絶縁膜77を形成する。

(もっと読む)

グラフェン配線およびその製造方法

【課題】配線構造における電気特性の向上を図る。

【解決手段】グラフェン配線は、配線溝を有する絶縁膜13と、前記配線溝内の両側面の前記絶縁膜上に形成された第1触媒膜15と、前記配線溝内の両側面の前記第1触媒膜上に形成され、両側面に対して垂直方向に積層された複数のグラフェンシートで構成された第1グラフェン層16と、を具備する。

(もっと読む)

配線形成方法

【課題】下層配線層と配線シード層との密着性を低下させないで高く維持することが可能な配線形成方法を提供する。

【解決手段】下層配線層4と絶縁性バリヤ層6と層間絶縁膜8と上層配線層が順次積層された被処理体に対して上層配線層と、連通配線層16とを形成する配線形成方法において、絶縁性バリヤ層を残した状態で連通ホール9Bを形成し、連通ホール内に犠牲膜を埋め込み、トレンチ9Aを形成するパターンマスク62を形成する前処理工程と、トレンチを形成するトレンチ形成工程と、犠牲膜60とパターンマスクとをアッシングするアッシング工程と、トレンチ内と連通ホール内に熱処理によりバリヤ層10を形成するバリヤ層形成工程と、異方性エッチングにより連通ホールの底部のバリヤ層と絶縁性バリヤ層とを除去する異方性エッチング工程と、配線シード層12を形成する配線シード層形成工程とを有する。

(もっと読む)

不揮発性記憶装置およびその製造方法

【課題】より低抵抗な配線層を有する不揮発性記憶装置を提供する。

【解決手段】実施形態の不揮発性記憶装置は、書き替え可能な複数の不揮発性メモリセルと、前記複数のメモリセルのそれぞれに電気的に接続可能な配線層と、を備えた不揮発性半導体記憶装置である。前記配線層は、絶縁層に設けられたトレンチ内に設けられ、前記配線層は、第1導電層と、前記第1導電層の上に設けられた第2導電層と、を有し、前記配線層が充填されていない前記トレンチに対する前記第1導電層の埋め込み性は、前記配線層が充填されていない前記トレンチに対する前記第2導電層の埋め込み性よりも高く、前記第2導電層の比抵抗は、前記第1導電層の比抵抗よりも低い。

(もっと読む)

半導体ウエハ装置およびその製造方法

【課題】 所望の配線構造を形成することができ、かつウエハ有効領域の欠陥率の増加を防止することのできる半導体ウエハ装置の製造方法を提供する。

【解決手段】 半導体ウエハ装置の製造方法は、(a)回路領域に半導体素子を形成した半導体ウエハ上に半導体素子に接続された下層配線パターンを形成する工程と、(b)下層配線パターンを覆って半導体ウエハ上に層間絶縁膜を形成する工程と、(c)回路領域上で下層配線パターンに接続されたビア導電体とその上に配置された配線パターンとを、回路領域外の周辺領域上で配線パターンに対応する導電体パターンを、層間絶縁膜に埋め込んで形成する工程とを含む。導電体パターンは電気的に分離された状態で形成される。

(もっと読む)

パターン形成方法及びデバイス製造方法

【課題】露光装置の解像限界よりも微細な非周期的な部分を含むパターンを、露光装置を用いて形成する。

【解決手段】パターン形成方法は、ウエハW上に第1L&Sパターン71を形成し、第1L&Sパターン71を覆うように第1保護層48、周期方向が直交する第2L&Sパターン78、及びフォトレジスト層60を形成し、第2L&Sパターン78の一部と重なるように、フォトレジスト層60に第1開口部60A,60Bを有する第3パターンを形成し、第1開口部60A,60Bを介して第1保護層48に第2開口部48A,48Bを形成し、第2開口部48A,48Bを介して第1L&Sパターン71の一部を除去する。

(もっと読む)

半導体装置の製造方法

【課題】異方性エッチングを利用して、1つの銅膜に配線パターンとビアパターンとを同時に形成することが可能な半導体装置の製造方法を提供すること。

【解決手段】バリア膜100上に、銅膜101を形成する工程と、銅膜101上に、第1のマスク材を形成する工程と、第1のマスク材をマスクに用いて、銅膜101をバリア膜100が露出するまで異方的にエッチングする工程と、第1のマスク材を除去した後、異方的にエッチングされた銅膜101上に、第2のマスク材を形成する工程と、第2のマスク材をマスクに用いて、銅膜101をその途中まで異方的にエッチングする工程と、前記第2のマスク材を除去した後、異方的にエッチングされた銅膜101上に、絶縁物を堆積させ、異方的にエッチングされた銅膜101周囲に、層間絶縁膜106を形成する工程と、を具備する。

(もっと読む)

半導体装置の製造方法

【課題】異方的にエッチングされた銅膜に、簡単で実用的にCuバリア膜を形成できる半導体装置の製造方法を提供すること。

【解決手段】Cuバリア膜100上に、銅膜101を形成する工程と、銅膜101上に、マスク材102を形成する工程と、マスク材102をマスクに用いて、銅膜101をCuバリア膜100が露出するまで異方的にエッチングする工程と、マスク材102を除去した後、異方的にエッチングされた銅膜101上に、銅膜101に対して触媒作用があり、Cuバリア膜100には触媒作用がない選択析出現象を利用した無電解めっき法を用いて、銅の拡散を抑制する物質を含むめっき膜104を形成する工程と、を具備する。

(もっと読む)

半導体基板の製造方法

【課題】ビア配孔内に形成したカーボンナノチューブを埋め込む埋め込み膜が基板に均一に形成されないため基板の平坦化処理工程において層間絶縁膜が不均一に研磨されて、下層配線と上部電極がビア配線以外で電気的につながってしまう場合が発生する。

【解決手段】半導体基板における層間絶縁膜内のビアホール内にカーボンナノチューブを形成した後、基板全体をフッ化処理することにより、カーボンナノチューブが存在するビアホールにのみ埋め込み膜が形成され、その後に基板全体の平坦化処理のために基板を研磨する工程において、層間絶縁膜が局所的に研磨されることを防止する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】ビアに位置ずれが生じても、ビアがエアギャップにつながることを抑制できるようにする。

【解決手段】複数の配線240は例えばCu配線であり、互いに平行に延伸している。側壁絶縁膜212は、複数の配線240それぞれの側壁に形成されている。エアギャップは、複数の配線240それぞれの相互間に形成され、複数の側壁絶縁膜212の間に位置している。絶縁膜302は、複数の配線240上、複数の側壁絶縁膜212上、およびエアギャップ214上に形成されている。ビア344は絶縁膜302を貫通しており、いずれかの配線240に接続している。そして側壁絶縁膜212は、絶縁膜302がエッチングされる条件では絶縁膜302よりエッチングレートが低い材料により形成されている。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】機械的強度および密着力に優れた低誘電率の層間絶縁層を有する半導体装置を提供すること。

【解決手段】基板上に形成された、SiO2骨格を含む第1の多孔質層6と、第1の多孔質層6の直上に形成された、SiO2骨格を含む第2の多孔質層7と、第1の多孔質層6に埋め込まれたビア10と、第2の多孔質層7に埋め込まれた配線11と、を有し、第1の多孔質層6の孔密度x1は40%以下であり、第2の多孔質層7の孔密度x2は、(x1+5)%以上である半導体装置を提供する。

(もっと読む)

半導体装置及びその製造方法

【課題】配線間の実効的な容量の増加を抑制する。

【解決手段】半導体装置100は、6員環構造の環状シロキサンを原料とする絶縁膜11と、絶縁膜11に形成された配線溝12と、配線溝12に金属膜(配線メタル)15が埋め込まれて構成される配線10と、を有する。半導体装置100では、配線溝12の底面において、絶縁膜11の内部よりも単位体積あたりの炭素原子数、又は/及び、窒素原子数が多い改質層13が形成されている。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】生産性の低下を抑制しつつ、配線部分の抵抗の増大を抑制することができるとともに、電気的なリークの発生を抑制することのできる半導体装置の製造方法及び半導体装置を提供する。

【解決手段】層間絶縁膜としてポーラス状の低誘電率膜を有する半導体装置を基板上に形成する半導体装置の製造方法であって、前記基板に前記低誘電率膜を形成する低誘電率膜形成工程と、エッチングにより前記低誘電率膜にトレンチ又はホールを形成するエッチング工程と、前記トレンチ又はホール内に、ニトロ化合物のプラズマを作用させて前記低誘電率膜のエッチングにより露出された面を改質する改質工程と、前記トレンチ又はホール内に導体を充填する導体形成工程と、を具備している。

(もっと読む)

成膜方法及び処理システム

【課題】比誘電率の低い絶縁層の表面にMn等の金属を含む薄膜、例えばMnOxを効率的に形成することが可能な成膜方法を提供する。

【解決手段】絶縁層1が表面に形成された被処理体Wに対して成膜処理を施す成膜方法において、第1の金属よりなる第1の薄膜60を形成する第1の薄膜形成工程と、前記第1の薄膜を酸化して酸化膜60Aを形成する酸化工程と、前記酸化膜上に第2の金属を含む第2の薄膜62を形成する第2の薄膜形成工程とを有する。これにより、比誘電率の低い絶縁層の表面にMn等の金属を含む薄膜、例えばMnOxを効率的に形成する。

(もっと読む)

61 - 80 / 1,009

[ Back to top ]