Fターム[5F033RR30]の内容

半導体集積回路装置の内部配線 (234,551) | 絶縁膜の材料 (22,565) | 空気絶縁、エアブリッジ (208)

Fターム[5F033RR30]に分類される特許

21 - 40 / 208

半導体記憶装置およびその製造方法

【課題】耐圧確保に有利な構造を提供する。

【解決手段】実施形態の半導体記憶装置は、基板上で所定方向に平行に延伸した複数の素子分離領域と、隣接する素子分離領域に挟まれた素子領域上の第1絶縁膜と、素子領域上の所定方向に間隔を空けて形成され、第1絶縁膜の上に順に積層された電荷蓄積層、第2絶縁膜、及び制御ゲート電極をそれぞれ有する複数のワードラインと、その両側に1つずつ配置され所定方向の幅がワードラインより大きい選択トランジスタと、ワードライン及び選択トランジスタの上面を覆う層間絶縁膜と、ワードライン間に位置し上部を層間絶縁膜に覆われた第1空洞部と、選択トランジスタのワードラインとは反対側の側壁部に形成され上部が層間絶縁膜で覆われた第2空洞部を備える。実施形態の半導体記憶装置は、互いに隣接する選択トランジスタ間の基板表面に酸化膜が形成され、その下の所定方向に垂直方向の断面が凸型形状になっている。

(もっと読む)

半導体基板、その製造方法、および電子装置

【課題】カーボンナノチューブを用いた特性が良好な半導体基板、その製造方法、および電子装置を提供することにある。

【解決手段】

本発明の一態様による半導体基板は、一主面に下部電極を有する基板と、前記基板上の前記下部電極以外の部分に設けられた層間絶縁膜と、前記下部電極の上に設けられた触媒層と、前記触媒層上に設けられ、前記下部電極の一主面に垂直な方向に延伸する複数のカーボンナノチューブと、前記カーボンナノチューブ上に設けられ、前記下部電極と対向する上部電極と、前記触媒層および前記カーボンナノチューブの前記触媒層側の端部を覆う第1の埋め込み膜と、前記カーボンナノチューブの他端部の間に満たされ、前記第1の埋め込み膜よりも高密度のである第2の埋め込み膜と、を有する。

(もっと読む)

電子部品の製造方法

【課題】導電膜を含む層の加工によって密の配線と疎の配線とが混在して形成された配線層で、所望の配線間の領域にのみ空隙を形成することができる電子部品の製造方法を提供する。

【解決手段】実施形態によれば、電子部品の製造方法は、まず、密の配線と疎の配線とを含む配線パターンとなるように、基板1上の導電性材料膜を含む加工対象を加工する。ついで、密の配線の形成領域にのみ配線間を埋め込む犠牲膜111を形成した後、基板1上に絶縁膜112を形成する。絶縁膜112上にレジスト113を塗布し、密の配線の形成領域上の一部と疎の配線の形成領域とが露出するようにレジスト113のパターニングを行った後、レジスト113をマスクとして絶縁膜112をエッチングする。さらに、密の配線の形成領域上の一部を通して、犠牲膜111を除去する。そして、疎の配線の形成領域で隣接する配線間を埋め込むように基板1上に埋込絶縁膜114を形成する。

(もっと読む)

膜形成方法および半導体装置の製造方法

【課題】担持体上に形成したポリシラザン膜を転写することにより、基板表面に良好な膜を形成することのできる技術を提供する。

【解決手段】ポリシラザン材料を含む塗布液PをシートフィルムFの表面に塗布し、溶剤を揮発させることでポリシラザン薄膜Rを得る。これを半導体基板に転写するのに先立って、UV光源202から拡散板203を介して強度を均一化したUV光Lを薄膜Rに照射する。これにより、薄膜Rの表面Raの粘度が選択的に増大し、基板転写時に、基板表面に形成されたトレンチを埋めることなくエアギャップを形成することができる。

(もっと読む)

配線の形成方法

【課題】配線が微細化された場合でも、所望の高さの配線を得ることができる配線の形成方法を提供する。

【解決手段】実施形態によれば、まず、絶縁膜11上に形成した犠牲導体膜12に配線形成用溝12a,12bを形成する。ついで、配線形成用溝12a,12bが形成された犠牲導体膜12上の全面にCuを堆積し配線形成用溝12a,12b内に流動するようにリフローさせて、配線形成用溝12a,12b内にCu膜14bを形成する。その後、犠牲導体膜12とCu膜14bを通電層としてめっき法によって配線形成用溝12a,12b内のCu膜14b上にCu膜14cを積み増す。ついで、Cu膜14b,14cからなるCu配線14をCMP処理して平坦化した後、犠牲導体膜12を除去する。その後、Cu配線14が形成された絶縁膜11上に絶縁膜15を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】本実施形態は、配線形状の制御が容易になり、且つ、配線間を埋める絶縁膜表面の段差が回避できるような半導体装置及びその製造方法を提供する。

【解決手段】本実施形態の半導体装置の製造方法は、配線領域と非配線領域とを有する第1の絶縁膜において、配線領域に溝を形成し、第1の絶縁膜の上面と溝の底面及び側壁とを覆うように配線材料を堆積し、配線材料をエッチングすることにより、溝中に、溝と平行に、且つ、側壁と離して配置された複数の配線を形成し、第1の絶縁膜の上面と複数の配線の上面とを覆い、且つ、配線の間と側壁と側壁に隣り合うように配置された配線との間とを埋め込むように、第2の絶縁膜を形成する。

(もっと読む)

半導体装置の製造方法

【課題】制御性よく空洞部を形成することが可能な半導体装置の製造方法を提供する。

【解決手段】ダミーゲート電極22上にオフセットスペーサ材料層を形成し、オフセットスペーサ材料層に異方性エッチングを行い、ダミーゲート電極22の側壁下部にオフセットスペーサ24を形成する。そして、サイドウォール15の形成後、ダミーゲート電極22とオフセットスペーサ24とを除去し、高誘電率材料からなるゲート絶縁膜13とメタルゲート電極14とを異方性の高い堆積方法を用いて形成する。

(もっと読む)

配線パターン

【課題】コンタクトホールを起点とした絶縁膜の剥がれの伸展を防ぐことができる配線パターンを得る。

【解決手段】半絶縁性GaAs基板1上に、配線メタル2が設けられている。配線メタル2上に金メッキ4が設けられている。金メッキ4は、ボンディングパッド部5と配線部6を有する。ボンディングパッド部5及び配線部6を覆うように金メッキ4上に連続してSiN膜7が設けられている。ボンディングパッド部5上においてSiN膜7にコンタクトホール8が設けられている。ボンディングパッド部5と配線部6の間において金メッキ4に段差が設けられている。

(もっと読む)

半導体装置及びその製造方法

【課題】同層配線間の容量及び、上下層配線間の容量を低減し、配線間領域の実効誘電率を低減できる半導体装置及びその製造方法を提供する。

【解決手段】半導体装置は、基板上に形成された第1の絶縁膜101と、第1の絶縁膜101の上部に埋め込まれた複数の第1の配線120と、第1の絶縁膜101上及び複数の第1の配線120上に形成され、開口部を有するライナー絶縁膜104と、ライナー絶縁膜104上に形成された第2の絶縁膜107と、第2の絶縁膜107の上部に埋め込まれた複数の第2の配線110とを備える。第1の絶縁膜101における、第1の配線120の間であって、ライナー絶縁膜104の開口部と重なる部分には、絶縁膜によって塞がれたエアギャップ108が形成されており、第2の絶縁膜107の比誘電率は2.5以下である。

(もっと読む)

分離トレンチの形成方法

【課題】隣接デバイスの特性への悪影響を低減するTSV相互接続構造の製造方法を提供する。

【解決手段】第1の主面S1を有する基板を設け、少なくとも一つのTSV穴部と、TSV穴部を囲み残りの基板材料によって分離されるトレンチ状構造3、とをエッチングにより同時に作製する。基板の第1の主面でトレンチ状構造の開口をピンチオフするためと、TSV穴部側壁を平滑にするために、誘電性のライナー2a、2bを堆積し、トレンチ状構造にエアギャップ4を作製する。TSV相互接続10を生成するためにTSV穴部に導体材料を堆積する。

(もっと読む)

電力増幅装置及び連結電力増幅装置

【課題】ソース電極からビアホールまでの距離をさらに短くし、インダクタンスの影響をできる限り低下させる増幅装置を提供する。

【解決手段】電力増幅装置は、接地のためのビアホールと接続する接地部と、接地部を接続するソース電極接地導体と、ソース電極接地導体に連結したソース電極と、ソース電極接地導体に接触しない内側ソース電極と、ドレイン電極と、ゲート電極と、内側ソース電極と接地部とを直接接続する接地ブリッジと、を備える。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、多層配線構造を有する半導体装置及びその製造方法に関し、信頼性や製造歩留りが高く、設計的な制約の小さい半導体装置及びその製造方法を提供することを目的とする。

【解決手段】基板10上に形成された配線20、40、60、80と、配線20、40、60、80の周囲に形成された低誘電率膜12、32、52、72、92と、低誘電率膜12、32、52、72、92の形成材料より弾性係数の大きい誘電体材料で形成され、基板面に垂直に見て配線20、40、60、80に重なって配置された補強用絶縁膜42a、62a、82a、102aと、配線20、40、60、80に交差して配置された補強用絶縁膜22b、42b、62b、82b、102bとを有するように構成する。

(もっと読む)

不揮発性半導体記憶装置および不揮発性半導体記憶装置の製造方法

【課題】隣接する浮遊ゲート電極間の間隔を増大させることなく、隣接する浮遊ゲート電極間の寄生容量を低減する。

【解決手段】レンチ2内に埋め込まれた埋め込み絶縁膜3の一部を除去することで、ワード線方向DWに隣接する浮遊ゲート電極6間に空隙AG1を形成し、空隙AG1は、制御ゲート電極8下に潜るようにしてトレンチ2に沿って連続して形成する。

(もっと読む)

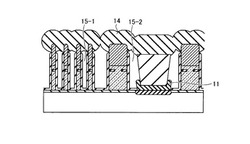

不揮発性半導体記憶装置及びその製造方法

【課題】周辺回路における回路動作の遅延を低減できる不揮発性半導体記憶装置を提供する。

【解決手段】半導体基板11上に所定間隔を空けて形成され、ゲート絶縁膜1、浮遊ゲート電極2、ゲート間絶縁膜3、及び制御ゲート電極4をそれぞれ有する複数のメモリセルMCと、メモリセルMCの浮遊ゲート電極2の側面、ゲート間絶縁膜3の側面、及び制御ゲート電極4の側面に形成され、空隙を有する側壁絶縁膜18Bと、基板11上に形成され、ゲート絶縁膜1、第1ゲート電極2、ゲート間絶縁膜3、及び制御ゲート電極4を有する周辺トランジスタPTと、周辺トランジスタPTの第1ゲート電極2の側面、ゲート間絶縁膜3の側面、及び制御ゲート電極4の側面に形成され、空隙19Aを有する側壁絶縁膜18Aとを備える。基板11上の最も低い位置にある空隙19Aの上端は、ゲート間絶縁膜3より基板11上の低い位置にある。

(もっと読む)

コプレーナ線路のエアブリッジ構造

【課題】コプレーナ線路の信号線路とエアブリッジとの交差容量の影響を抑制しつつ、複数のエアブリッジを容易に使用できるようにする。

【解決手段】エアブリッジ構造100のうち、下層配線層8に、接地線路2A,2Bのうち信号線路1を挟んで互いに対向する位置を切り欠いて形成した空孔領域12A,12Bをそれぞれ設けるとともに、上層配線層7に、空孔領域12Aの上部位置に下層配線層8の接地線路2Aと電気的に接続された上層接地電極13Aと、空孔領域12Bの上部位置に下層配線層8の接地線路2Bと電気的に接続された上層接地電極13Bとを設け、エアブリッジ3で、上層接地電極13A,13Bを介して接地線路2A,2B間を電気的に接続する。

(もっと読む)

エアブリッジの製造方法

【課題】エアブリッジの強度低下抑制、半導体素子の特性悪化抑制およびスペーサ材料残りの問題の回避を達成しつつ、被覆面積の大きなエアブリッジを製造することができるエアブリッジの製造方法を提供する。

【解決手段】レジスト層100の上に、二層目のレジスト層であるレジスト層102を塗布する。レジスト層102についても、一層目(レジスト層100)と同様に、所定の寸法W2を残すように露光現像を行い、その後、三層目のレジスト(レジスト層104)を塗布する。三層目(レジスト層104)においても所定の寸法W3を残すように露光現像を行う。形作られたレジスト層102、104、106の積層構造上に、エアブリッジ10を形成する材料の層106を積層することにより、エアブリッジ10の形成を行う。レジスト除去を行うことにより、断面形状が階段形状であるエアブリッジ10が完成する。

(もっと読む)

半導体装置およびその製造方法

【課題】 エアギャップ構造を簡易な方法で形成する。

【解決手段】 本発明の一態様の半導体装置の製造方法によれば、半導体基板上に導電層を含む被加工膜を形成する工程と、前記被加工膜上にダミー膜を形成する工程と、を備えている。さらに、前記ダミー膜を所望の形状にデポ条件の異方性エッチングにより加工する工程と、前記被加工膜を所望の形状に異方性エッチングにより加工する工程と、前記所望の形状に加工された被加工膜上の前記ダミー膜を異方性エッチングにより除去する工程と、前記被加工膜上に上層膜を形成する工程と、を備えている。

(もっと読む)

半導体装置およびその製造方法

【課題】センシング部を複数の基板で封止した半導体装置において、基板の平面方向に配線を設けたとしても、配線のレイアウトを簡略化することができる構造、およびその製造方法を提供する。

【解決手段】キャップ部300は、センサ部100に設けられた第1固定部と第2固定部とを電気的に接続したクロス配線部323を備え、クロス配線部323はキャップ部300の一面301に配置されたクロス配線322を備えている。また、キャップ部300は、キャップ部300を貫通し、一端がクロス配線322に電気的に接続され、他端がキャップ部300の他面302に配置された貫通電極344を備えている。これにより、貫通電極344を介してクロス配線322の電位、すなわち、センサ部100の第1固定部および第2固定部の電位をキャップ部300の他面302に取り出すことができる。

(もっと読む)

半導体装置の製造方法

【課題】高周波領域において優れた電気的特性が得られるように、寄生容量を低減し得る半導体装置の製造方法を得る。

【解決手段】第1のソース電極、ゲート電極、ドレイン電極、及び第2のソース電極が、所定方向に沿ってこの順に並んで半導体基板の上面上に形成された構造を有するトランジスタを形成する。犠牲層を、トランジスタを覆って半導体基板の上面上に形成する。犠牲層を部分的に除去することにより、第1のソース電極及び前記第2のソース電極を露出する。第1のソース電極及び第2のソース電極に接続され、所定方向に沿って延在する配線を、犠牲層の上面上に形成する。犠牲層を除去する。トランジスタ及び配線を覆う形状に加工されたシート、テープ、又は基板を、トランジスタ及び配線を覆って半導体基板の上面上に貼り付ける。

(もっと読む)

半導体装置の製造方法及び基板処理装置

【課題】生産性を向上し、空隙率が高いエアギャップを形成することができる半導体装置の製造方法及び基板処理装置を提供することができる。

【解決手段】表面に複数の配線層が形成された基板に対し処理ガスを供給して、前記基板の表面における隣り合う配線層間に形成される溝に対して段差被覆性の悪い条件で絶縁膜を形成する工程と、前記基板に対しエッチングガスを供給して、前記絶縁膜に対して等方性エッチングを行う工程と、を所定回数行うことにより、隣り合う配線層間にエアギャップを形成する。

(もっと読む)

21 - 40 / 208

[ Back to top ]