Fターム[5F033RR30]の内容

半導体集積回路装置の内部配線 (234,551) | 絶縁膜の材料 (22,565) | 空気絶縁、エアブリッジ (208)

Fターム[5F033RR30]に分類される特許

41 - 60 / 208

半導体装置およびその製造方法

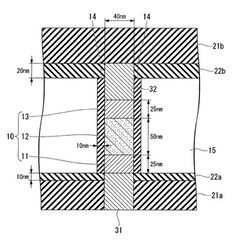

【課題】相変化記録素子のまわりを伝導率の低い真空の空隙部で覆うことで、さらに高い発熱効率を得ることができ、書き換え電流を低減することができる半導体装置を提供する。

【解決手段】半導体基板と、半導体基板の上に形成されたスイッチング素子を含む素子層と、素子層上において、スイッチング素子に接続されたヒータ電極11、ヒータ電極11の熱によって相転移する相変化記録材料層12及び上部電極13が順次積層されてなる相変化記録素子10と、相変化記録素子10の上に積層された層間絶縁膜21bと、素子層と層間絶縁膜21bの間にあってヒータ電極11または相変化記録材料層12のいずれか一方又は両方の周囲に形成された真空の空隙部15と、を具備してなる。

(もっと読む)

半導体装置、電子装置、及び半導体装置の製造方法

【課題】第1インダクタと第2インダクタを構成する金属材料のマイグレーションに起因して第1インダクタと第2インダクタの絶縁が確保できなくなることを、抑制する。

【解決手段】半導体チップ100は配線基板200の第1面上に実装されており、多層配線層を有している。第1インダクタ112は多層配線層に形成されており、巻き軸方向が配線基板200と水平方向を向いている。第2インダクタ122は多層配線層に形成されており、巻き軸方向が配線基板200と水平方向を向いている。第2インダクタ122は第1インダクタ112に対向している。封止樹脂400は、配線基板200の少なくとも第1面と、半導体チップ100とを封止している。溝500は、封止樹脂400と多層配線層の界面のうち、少なくとも第1インダクタ112と第2インダクタ122の間に位置している部分の全域に形成されている。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】選択メタルキャップを用いることなしに、生産性の高いエアギャップ配線を形成する。

【解決手段】ウエハ14上の絶縁膜200にCuダマシン配線210を形成する第1の工程と、ウエハ14上に第1のバリア膜220を形成する第2の工程と、後続する接続孔242を開口する工程において、接続孔242の孔底部244に露出するCu配線206と隣接する絶縁膜200、及び最小寸法スペースの3倍以上の幅をもつ幅広スペース200aを保護するように、第1のバリア膜220をパターニングする第3の工程と、第1のバリア膜220をマスクとして絶縁膜200を除去する第4の工程と、ウエハ14上に第2のバリア膜224を形成する第5の工程と、Cu配線206間にエアギャップ232を残しつつ絶縁膜230を形成する第6の工程と、を有する。

(もっと読む)

半導体装置の製造方法

【課題】高周波領域において優れた電気的特性が得られるように、寄生容量を低減し得る半導体装置の製造方法を得る。

【解決手段】第1のソース電極、ゲート電極、ドレイン電極、及び第2のソース電極が、所定方向に沿ってこの順に並んで半導体基板の上面上に形成された構造を有するトランジスタを形成する。犠牲層を、トランジスタを覆って半導体基板の上面上に形成する。犠牲層を部分的に除去することにより、第1のソース電極及び前記第2のソース電極を露出する。第1のソース電極及び第2のソース電極に接続され、所定方向に沿って延在する配線を、犠牲層の上面上に形成する。犠牲層を除去する。上面が開口した枠体を、トランジスタの周囲を取り囲んで、半導体基板の上面上に形成する。枠体上にテープを貼り付けることにより、枠体及びテープによってトランジスタ及び配線を覆う。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】ビアに位置ずれが生じても、ビアがエアギャップにつながることを抑制できるようにする。

【解決手段】複数の配線240は例えばCu配線であり、互いに平行に延伸している。側壁絶縁膜212は、複数の配線240それぞれの側壁に形成されている。エアギャップは、複数の配線240それぞれの相互間に形成され、複数の側壁絶縁膜212の間に位置している。絶縁膜302は、複数の配線240上、複数の側壁絶縁膜212上、およびエアギャップ214上に形成されている。ビア344は絶縁膜302を貫通しており、いずれかの配線240に接続している。そして側壁絶縁膜212は、絶縁膜302がエッチングされる条件では絶縁膜302よりエッチングレートが低い材料により形成されている。

(もっと読む)

半導体装置及び製造方法

【課題】 基板及び表面層にビアホールが形成された半導体装置において、表面層の剥離及び破壊を抑制すること。

【解決手段】 本半導体装置は、基板10と、基板10上に設けられた基板10と異なる材料からなる表面層20と、表面層20上に設けられた電極パッド50と、を備え、基板10及び表面層20にはビアホール30が形成され、ビアホール30内には、電極パッド50と電気的に接続された金属層32が設けられ、ビアホール30の開口部の周囲には、ビアホール30を囲むように表面層20に溝22が形成されている。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の配線間容量を低減する。

【解決手段】半導体装置の製造方法は、基板の上方に絶縁膜を形成する工程と、絶縁膜を貫通する第1の溝及び絶縁膜の内部で終端する第2の溝を絶縁膜に形成する工程と、絶縁膜の内部で終端する配線溝を絶縁膜に形成する工程と、第1の溝の表面及び配線溝の表面に第1の金属膜を形成するともに、第2の溝の上方を覆うように第1の金属膜を形成する工程と、第1の溝及び配線溝に第2の金属膜を埋め込む工程と、を備える。

(もっと読む)

半導体装置およびその製造方法

【課題】高い耐電圧特性、および耐リーク特性を有する配線構造を有する半導体装置およびその製造方法を提供する。

【解決手段】半導体素子が設けられた基板と、前記基板上に形成された第1および第2の配線と、前記第1の配線の下面の前記第2の配線側に接続されたビアと、前記ビアを含むビア層絶縁膜と、を有する半導体装置を提供する。前記ビアは、前記第1の配線と前記第2の配線の間の領域である配線間領域下の上端に凹部を有する。前記ビア層絶縁膜は、前記第1および第2の配線の幅方向に前記ビアと隣接する領域を含む溝を前記配線間領域の下に有する。前記配線間領域および前記溝内にはエアギャップが含まれる。

(もっと読む)

半導体装置

【課題】MEMSキャパシタとその制御用集積回路を反りの抑えられた1枚の基板上に有する半導体装置を提供する。

【解決手段】貫通孔を含む貫通孔領域を有する基板と、前記基板の上方のMEMSキャパシタと、前記MEMSキャパシタの下方の前記MEMSキャパシタの制御用集積回路とを有する半導体装置を提供する。前記制御用集積回路は、前記基板上のトランジスタを含む。前記MEMSキャパシタの真下の前記基板上の領域と前記貫通孔領域とは、少なくとも一部において重なる。

(もっと読む)

半導体装置及びその製造方法

【課題】微細化に伴うLERやLWRに起因する配線の抵抗率の増大を抑制し得る手法を提供する。

【解決手段】半導体装置は、基板101と、基板上において同一の配線層内に形成された複数の配線111と、配線間に埋め込まれるよう形成された複数の絶縁膜112とを備える。そして、これら複数の配線は、両側面のLER(Line Edge Roughness)の相関係数が正である配線が、連続して2N本(Nは4以上の整数)以上並んだ配線群を含む。

(もっと読む)

高耐圧配線、配線設計装置および方法

【課題】層間絶縁膜を厚くすることなく、放電耐圧を向上させ、デバイスの特性の安定化や性能の向上を図る。

【解決手段】高耐圧配線は、Si基板101上に形成された配線層103と、絶縁膜104と、上層配線105,106と、絶縁膜104に形成された溝107とを有する。配線層103上の絶縁膜104の厚さTは、上層配線105と106間の距離dよりも小さく、溝の幅Wは、距離dよりも小さい。絶縁膜104の厚さTは、配線層103と上層配線105,106との間に与えられる最大の電位差Vmaxよりも絶縁膜104の耐圧が大きくなるように設定され、絶縁膜104の露出量Xは、溝の幅Wと距離dとが等しいときの絶縁膜104に沿った沿面放電開始電圧をV0(V0=b×lnT+c、b,cは定数)としたとき、Vmax<aX+V0(aは定数)となるように設定される。

(もっと読む)

半導体装置の製造方法

【課題】安定した形状の信頼性の高いエアギャップを効率良く形成する半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法では、半導体基板上に、ビアホール及びエアギャップ用トレンチを含む複数のホールを有する層間絶縁膜を形成する。次に、エアギャップ用トレンチ内に有機材料を埋め込んだ後、硬化させる。また、ビアホール内にビアプラグを形成する。この後、エアギャップ用トレンチ内に埋め込まれた有機材料を除去することにより、エアギャップを形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】どのようなレイアウトの配線に対しても、個々の配線ごとにエアギャップ部を設ける。エアギャップ部によって、配線の寄生容量を低減する。

【解決手段】半導体装置は、層間絶縁膜と、層間絶縁膜内に埋め込まれた配線と、配線の側面と層間絶縁膜との間に設けられたエアギャップ部と、を有する。半導体装置の製造方法は、配線の側面上に第2のサイドウォール膜を形成した後、第2のサイドウォール膜の一部が露出するように第1の絶縁膜を形成する。次に、第2のサイドウォール膜を除去することによりサイドスペースを形成した後、サイドスペースが埋め込まれないように第2の絶縁膜を形成することによりサイドスペースから構成されるエアギャップ部を形成する。

(もっと読む)

制御された気孔を形成するための材料及び方法

【課題】基材の内部に空隙を形成するための方法を提供する。

【解決手段】基材を用意する工程;少なくとも1つの犠牲材料前駆体の堆積によって犠牲材料を堆積する工程;複合層を堆積する工程;該複合層中のポロゲン材料を除去して多孔質層を形成する工程;及び積層基材を除去媒体と接触させて前記犠牲材料を実質的に除去し、前記基材の内部に空隙を与える工程を含み、前記少なくとも1つの犠牲材料前駆体が、有機ポロゲン、シリコン、極性溶媒に可溶な金属酸化物、及びそれらの混合物からなる群より選択される方法が提供される。

(もっと読む)

半導体装置及びその製造方法

【課題】外力を受けても変形あるいは破壊しにくい半導体装置の構造及びその製造方法を提供する。

【解決手段】半導体基板1表面に第1の掘り込み部を形成する。複数の配線電極3は第1の掘り込み部に埋め込まれた埋め込み部と半導体基板1上に露出する露出部とからなる。複数の配線電極のうち所定の配線電極3間にエアーブリッジ電極6が設けられている。配線電極3とエアーブリッジ電極6との接続は、配線電極3の露出部に第2の掘り込み部を形成し、エアーブリッジ電極6の脚部の接続部を第2の掘り込み部に埋め込むことによって行う。

(もっと読む)

半導体装置、及びその製造方法

【課題】配線の導通信頼性を損なうことなく、エアギャップを形成でき、配線間容量Cが低減した配線膜構造を有する半導体装置を提供することである。

【解決手段】 半導体装置の製造方法において、第1絶縁膜を形成する第1絶縁膜形成工程と、前記第1絶縁膜に配線膜を形成する配線膜形成工程と、前記配線膜が形成されてない箇所の前記第1絶縁膜にドライエッチングで溝を形成するドライエッチング工程と、前記ドライエッチング工程の後、前記溝が埋め尽くされることが無いよう、前記配線膜および前記溝上に第2絶縁膜を形成する第2絶縁膜形成工程とを具備する。

(もっと読む)

導体トラック配列の製造方法

【課題】従来例に比べて結合容量が低下し、さらに機械的または電気的特性を向上させた導体トラック間のエアギャップの製造方法を提供する。

【解決手段】基材1、2と、少なくとも2つの導体トラック4と、空洞6と、導体トラック4を覆い、空洞6を塞ぐレジスト層5とを含む、導体トラック配列とする。導体トラック4の幅B1よりも小さい幅B2のキャリアトラックTBを形成することにより、結合容量と信号遅延を低減するためのエアギャップが、導体トラック4の下にその側面に沿ってセルフアライン技術により形成される。

(もっと読む)

段階化キャップ層を有するパターニング可能low−k誘電体配線構造、エアギャップ包含配線構造、および製作方法

【課題】パターニングされた段階化キャップ層の表面上に配される少なくとも1つのパターニングされ且つ硬化されたlow−k物質を含む配線構造を提供する。

【解決手段】少なくとも1つの硬化され且つパターニングされたlow−k物質およびパターニングされた段階化キャップ層は、その中に組み込まれる導電的充填領域を各々有する。パターニングされ且つ硬化されたlow−k物質は、1つ以上の酸感受性イメージング可能基を有する機能性ポリマー、コポリマー、あるいは少なくとも2種の任意の組み合わせのポリマー類もしくはコポリマー類またはその両方を含むブレンドの硬化生成物であり、段階化キャップ層はバリア領域として機能する下部領域および恒久的な反射防止膜の反射防止特性を有する上部領域を含む。

(もっと読む)

半導体装置

【課題】スルーホールの深さを正確に制御して、特定の配線層に選択的にエアギャップを形成した半導体装置を提供する。

【解決手段】本発明の一態様に係る半導体装置100は、半導体素子を有する半導体基板1と、半導体基板1の上方に形成され、配線10a、10b、10c、10d、配線10c、10dの周囲のエアギャップ101、およびエアギャップ101に連続するスルーホール102含む配線構造と、スルーホール102下に形成されたスルーホールストッパー103と、を有する。

(もっと読む)

微小コイル装置およびその製作方法

導電性コイルの製作方法。この方法は、コイル、通常、平面らせん状の導電性コイルを製作するために半導体製造プロセス(例えばTSV)を使用することを含む。 (もっと読む)

41 - 60 / 208

[ Back to top ]