Fターム[5F033TT02]の内容

半導体集積回路装置の内部配線 (234,551) | 絶縁膜の構造、形状 (4,088) | 積層構造 (1,984) | 全てが無機材料 (1,214)

Fターム[5F033TT02]に分類される特許

101 - 120 / 1,214

半導体装置及びその製造方法

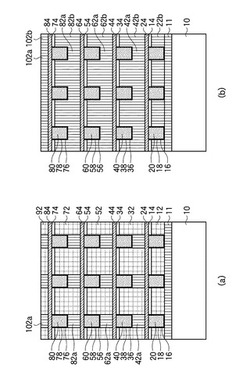

【課題】本発明は、多層配線構造を有する半導体装置及びその製造方法に関し、信頼性や製造歩留りが高く、設計的な制約の小さい半導体装置及びその製造方法を提供することを目的とする。

【解決手段】基板10上に形成された配線20、40、60、80と、配線20、40、60、80の周囲に形成された低誘電率膜12、32、52、72、92と、低誘電率膜12、32、52、72、92の形成材料より弾性係数の大きい誘電体材料で形成され、基板面に垂直に見て配線20、40、60、80に重なって配置された補強用絶縁膜42a、62a、82a、102aと、配線20、40、60、80に交差して配置された補強用絶縁膜22b、42b、62b、82b、102bとを有するように構成する。

(もっと読む)

半導体装置およびその製造方法

【課題】サリサイドプロセスにより金属シリサイド層を形成した半導体装置の信頼性を向上させる。

【解決手段】部分反応方式のサリサイドプロセスによりゲート電極8a、8b、n+型半導体領域9bおよびp+型半導体領域10bの表面に金属シリサイド層41を形成する。金属シリサイド層41を形成する際の第1の熱処理では、熱伝導型アニール装置を用いて半導体ウエハを熱処理し、第2の熱処理では、マイクロ波アニール装置を用いて半導体ウエハを熱処理することにより、第2の熱処理を低温化し、金属シリサイド層41の異常成長を防ぐ。これにより金属シリサイド層41の接合リーク電流を低減する。

(もっと読む)

カーボンナノチューブ配線の製造方法

【課題】カーボンナノチューブを有するプラグ配線において良好な電気的接続を得ることができるカーボンナノチューブ配線の製造方法を提供する。

【解決手段】第1配線層12上に層間絶縁膜13を形成する工程と、第1配線層上の層間絶縁膜内にコンタクト孔15を形成する工程と、コンタクト孔内の第1配線層上にカーボンナノチューブ16を成長させ、コンタクト孔から先端が突き出た複数のカーボンナノチューブを形成する工程と、層間絶縁膜上及び複数のカーボンナノチューブ間に、ストッパ膜17を形成する工程と、ストッパ膜上及び複数のカーボンナノチューブ上に絶縁膜を形成する工程と、ストッパ膜をストッパとして用い、ストッパ膜上の絶縁膜と共に、コンタクト孔上の複数のカーボンナノチューブを除去する工程と、複数のカーボンナノチューブ上に第2配線層14を形成する工程とを備える。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、ゲート電極の幅を十分に確保して、ゲート電極の抵抗値を小さくすることが可能で、かつゲート電極間の容量を小さくすることの可能な半導体装置及びその製造方法を提供することを課題とする。

【解決手段】半導体基板に設けられ、Y方向に延在する第1の溝15と、半導体基板に設けられ、第1の溝15と交差するXの方向に延在する第2の溝25と、第1及び第2の溝15,25に囲まれ、第2の溝25に露出された対向する第1及び第2の側面26a,26bを有するピラー26と、ゲート絶縁膜28を介して、ピラー26の第2の側面26bに接触するように、第2の溝25の下部に設けられた1つのゲート電極29と、ゲート電極29の側面とピラーの第1の側面26aとの間に配置された空隙と、を有する。

(もっと読む)

埋没ジャンクションを有する垂直型トランジスタ及びその形成方法

【課題】ドーパントの濃度をより高く確保しつつも、ドーパントが拡散されるジャンクション深さを制御することができ、改善された接触抵抗を実現し、チャネル領域との離隔間隔を減らしてチャネルのしきい電圧(Vt)を改善できる埋没ジャンクションを有する垂直型トランジスタ及びその形成方法を提供すること。

【解決手段】半導体基板に第1の側面に反対される第2の側面を有して突出した壁体)を形成し、壁体の第1の側面の一部を選択的に開口する開口部を有する片側コンタクトマスクを形成した後、開口部に露出した第1の側面部分に互いに拡散度が異なる不純物を拡散させて第1の不純物層及び該第1の不純物層を覆う第2の不純物層を形成することを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の電気的な接続信頼性を向上させる。

【解決手段】(a)半導体基板の主面上に、主導体膜(下地膜)7Aおよび主導体膜7A上のストッパ絶縁膜(被測定膜)6sを積層する工程、(b)ストッパ絶縁膜6sに開口部8を形成する工程、を含んでいる。また、(c)開口部8に電子ビーム(励起線)EBを照射して、特性X線を放出させる工程、および(d)特性X線を検出し、特性X線の検出結果に基いて開口部8の底部8Bにおけるストッパ絶縁膜6sの有無または膜厚を判定する工程、を含んでいる。また、(d)工程では、特性X線に含まれる複数の元素成分の比率により、ストッパ絶縁膜6sの有無または膜厚を判定する。

(もっと読む)

半導体装置

【課題】周辺部を損傷させずに、電流を供給することによって切断され得る電気ヒューズ構造を有する半導体装置を提供する。

【解決手段】電気ヒューズ10は、電子回路とその電子回路のスペアとしての冗長回路との間に電気的に接続され、それらの回路が樹脂封止された後に、外部から電流が供給されることによって切断され得るものである。電気ヒューズ10は、ファイン層中に設けられており、主配線1およびバリア膜3からなる。主配線1およびバリア膜3のそれぞれの線膨張係数は、その周辺に設けられている絶縁層2,4,および5のそれぞれの線膨張係数よりも大きい。また、主配線1およびバリア膜3のそれぞれの融点は、絶縁層2,4,および5のそれぞれの融点よりも低い。

(もっと読む)

薄膜トランジスタ及び液晶表示装置の作製方法

【課題】作製工程を大幅に削減し、低コストで生産性の良い液晶表示装置を提供する。消費電力が少なく、信頼性の高い液晶表示装置を提供する。

【解決手段】ゲート配線上の一部を含む半導体層のエッチングと、画素電極とドレイン電極を接続するためのコンタクトホールの形成を、同一のフォトリソグラフィ工程及びエッチング工程で行うことで、フォトリソグラフィ工程を削減する。これにより露出したゲート配線の一部を絶縁層で覆い、これに液晶層の間隔を維持するスペーサを兼ねさせる。フォトリソグラフィ工程を削減することにより、低コストで生産性の良い液晶表示装置を提供することができる。また、半導体層に酸化物半導体を用いることで、消費電力が低減され、信頼性の高い液晶表示装置を提供することができる。

(もっと読む)

表示装置

【課題】画素電極上に金属膜を形成して積層構造とする際に、1つのレジストマスクを用

いて、画素電極及び金属膜を形成することを課題とする。

【解決手段】画素電極となる導電膜と金属膜を積層させる。金属膜上に半透部を有する露

光マスクを用いて、膜厚の厚い領域と該領域よりも膜厚が薄い領域とを有するレジストパ

ターンを形成する。レジストパターンを用いて画素電極と、画素電極上の一部に接する金

属膜を形成する。以上により、1つのレジストマスクを用いて、画素電極及び金属膜を形

成することが可能となる。

(もっと読む)

半導体装置、およびその製造方法、ならびにデータ処理装置

【課題】テーパー部を有する溝を備えた半導体装置を容易に形成する。溝内に空洞が形成されるのを防止すると共に、製造歩留まりの低下を抑制する。

【解決手段】半導体装置は、第1の面を有する材料層と、材料層内に設けられ、第1の面に開口部を有する溝を備える。溝は、開口部に接し1以上のスキャロップ形成溝を有するテーパー部と、おおむね垂直な側壁を有する垂直部を有する。スキャロップ形成溝の幅は、垂直部の溝幅よりも大きくなっている。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】CFx膜を層間絶縁膜として有する多層配線構造の半導体装置において、低誘電率であるCFx膜の利点を生かすことができ、かつCMP処理による特性の劣化を防止することのできる半導体装置の製造方法を提供する。

【解決手段】本発明の半導体装置の製造方法は、CFx膜を成膜する工程(a)と、CFx膜に所定パターンの凹部を形成する工程(b)と、凹部を埋めかつCFx膜上にわたって配線層を設ける工程(c)と、凹部内以外の前記CFx膜上の余剰の配線層をCMP(化学機械研磨)によって除去してCFx膜の表面を露出させる工程(d)と、を有し、工程(b)の前または後において、CFx膜の表面を窒化する工程(e)を備える。

(もっと読む)

半導体装置及びその製造方法

【課題】容量素子の良好な特性と高い信頼性を実現することが可能な半導体装置を提供する。

【解決手段】半導体基板上に第1の絶縁膜を介して形成されている下部電極と、この下部電極の周囲に形成され、下部電極の表面よりも高い表面を有するダミー電極と、下部電極上にダミー電極の最上表面よりも表面が低い位置にある誘電体膜を介して形成された上部電極と、ダミー電極に周囲を囲まれた窪みを埋める第2の絶縁膜とを具備して成る半導体装置を構成する。

(もっと読む)

半導体装置の製造方法

【課題】メタルゲートプロセスにおけるプリメタル層間絶縁膜の平坦性を向上できるようにする。

【解決手段】まず、半導体基板1の上に、ゲート絶縁膜3を介在させてゲート電極4を形成する。その後、半導体基板1にゲート電極4をマスクとしてソース・ドレイン領域を形成する。続いて、ゲート電極4を覆うように半導体基板1上の全面に第1の酸化シリコン膜10を形成する。その後、ゲート電極4をストップ膜とするCMP法により、第1の酸化シリコン膜10を平坦化する。続いて、ゲート電極4を含む第1の酸化シリコン膜10の上に、第2の酸化シリコン膜11を形成する。その後、ゲート電極4をストップ膜とするCMP法により、第2の酸化シリコン膜10を平坦化する。さらに、ゲート電極4を含む第2の酸化シリコン膜10の上に、第3の酸化シリコン膜12を形成する。

(もっと読む)

半導体ウエハ装置およびその製造方法

【課題】 所望の配線構造を形成することができ、かつウエハ有効領域の欠陥率の増加を防止することのできる半導体ウエハ装置の製造方法を提供する。

【解決手段】 半導体ウエハ装置の製造方法は、(a)回路領域に半導体素子を形成した半導体ウエハ上に半導体素子に接続された下層配線パターンを形成する工程と、(b)下層配線パターンを覆って半導体ウエハ上に層間絶縁膜を形成する工程と、(c)回路領域上で下層配線パターンに接続されたビア導電体とその上に配置された配線パターンとを、回路領域外の周辺領域上で配線パターンに対応する導電体パターンを、層間絶縁膜に埋め込んで形成する工程とを含む。導電体パターンは電気的に分離された状態で形成される。

(もっと読む)

半導体装置の製造方法

【課題】厚みのばらつきが低減したCu配線層を形成する半導体装置の製造方法を提供する。

【解決手段】実施形態の半導体装置の製造方法は、基板1上に所望の配線厚みに対応する厚みのエッチングストッパー膜2を形成し、酸化膜3を形成し、マスク材4を形成し、マスク材に配線の形状の溝パターンを形成し、溝パターンが形成されたマスク材をマスクとして酸化膜に溝パターンが形成されるようにエッチングする。溝パターンが形成された酸化膜をマスクとして、溝パターンが形成されるようにエッチングストッパー膜を貫通するまでエッチングし、エッチングストッパー膜および酸化膜に形成された溝パターンを埋め込み、酸化膜の上面を覆いつくすようにCu膜5を形成し、エッチングストッパー膜をストッパーとして、その上面が露出するまでCu膜及び酸化膜にCMPを行う。

(もっと読む)

半導体集積回路装置の製造方法

【課題】プラズマCVD法を用いてCu配線上に良好な拡散バリア膜を形成する技術を提供する。

【解決手段】ダマシン法を用いて形成したCu配線19上にCuの拡散を防止する窒化シリコン膜21を形成する工程は、Cu配線19が形成された基板1をプラズマCVD装置のチャンバ内に搬入し、基板1を所定の温度に加熱する工程と、チャンバ内にアンモニアを供給し、第1のRFパワーでアンモニアをプラズマ分解することによって、Cu配線19の表面を還元処理する工程と、RFパワーが印加された状態で、チャンバ内にアンモニアとモノシランとを含む原料ガスを供給し、第2のRFパワーでアンモニアとシラン系ガスとをプラズマ分解することによって、Cu配線19上に窒化シリコン膜21を形成する工程とを含んでいる。

(もっと読む)

半導体装置およびその製造方法

【課題】コンタクト孔に埋め込まれる金属プラグの材料が層間絶縁膜に染み出すのを防止できる半導体装置を提供する。

【解決手段】隣り合う2つのメモリセル1のサイドウォール間の不純物拡散領域に電気的接続されるコンタクトプラグ40が、層間絶縁膜18を貫通して設けられている。コンタクト孔41の側壁は、層間絶縁膜18より緻密なシール膜42で覆われている。コンタクトプラグ40は、シール膜42の表面およびコンタクト孔41の底面部を覆うように形成されたバリアメタル膜43と、バリアメタル膜43に包囲された状態でコンタクト孔41内に埋め込まれた金属プラグ44とを含む。

(もっと読む)

半導体装置及びその製造方法

【課題】接続不良の発生を抑制することのできる、信頼性の高い半導体装置及びその製造方法を提供する。

【解決手段】半導体装置は、所定ピッチで所定の幅の素子領域が形成された半導体基板と、半導体基板上に積層された層間絶縁膜と、層間絶縁膜の上面から半導体基板の素子領域にかけて設けられ素子領域に接続される第1コンタクトとを備える。第1コンタクトは、素子領域上の層間絶縁膜に形成された素子領域の幅よりも大きい径を有するコンタクトホールと、コンタクトホールの底部に設けられ、素子領域に達する開口を有するスペーサ膜と、スペーサ膜の開口を介して素子領域に接続されるようにコンタクトホール内に埋め込まれたコンタクトプラグとを有する。

(もっと読む)

半導体装置とその製造方法

【課題】半導体装置とその製造方法において、ヒューズの微細化を図ること。

【解決手段】シリコン基板1に素子分離絶縁膜2を形成する工程と、素子分離絶縁膜2の上に第1の絶縁膜13を形成する工程と、第1の絶縁膜13にスリット13xを形成する工程と、スリット13xを通じて素子分離絶縁膜2をウエットエッチングして凹部2bを形成する工程と、凹部2bとスリット13xの各々の内面に第2の絶縁膜24を形成することにより、第2の絶縁膜24によりスリット13xを塞ぎつつ、凹部2b内にボイド24aを形成する工程と、ボイド24aの上の第2の絶縁膜24にホール25bを形成し、ホール25b内にボイド24aを露出させる工程と、露出したボイド24aとホール25bのそれぞれの中に導電膜27を形成することによりヒューズFを形成する工程とを有する半導体装置の製造方法による。

(もっと読む)

半導体装置の製造方法

【課題】基板に形成される第1の膜と第2の膜との重なり量を精度良く算出する。

【解決手段】半導体装置の製造方法は、基板の第1の領域及び第2の領域に第1の膜を形成する工程と、第2の領域の第1の膜の幅を測定する工程と、基板の第2の領域及び第3の領域に第2の膜を形成する工程と、第2の領域の第2の膜の幅及び第2の領域の第1の膜と第2の膜との距離を測定する工程と、第2の領域における第1の膜の幅の測定値、第2の膜の幅の測定値、第1の膜と第2の膜との距離の測定値及び第1の膜と第2の膜とに関する設計値に基づいて、第1の領域における第1の膜と第3の領域における第2の膜との重なり量を算出する工程と、を備える。

(もっと読む)

101 - 120 / 1,214

[ Back to top ]