Fターム[5F033TT02]の内容

半導体集積回路装置の内部配線 (234,551) | 絶縁膜の構造、形状 (4,088) | 積層構造 (1,984) | 全てが無機材料 (1,214)

Fターム[5F033TT02]に分類される特許

121 - 140 / 1,214

エッチング方法、エッチングシステムおよびエッチング装置

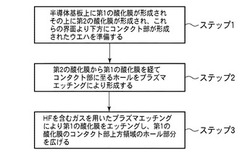

【課題】シリコン酸化膜にコンタクト部に到達する高アスペクト比のホールを形成する際に、ホール内のコンタクト材料とコンタクト部との間で十分なコンタクトがとれるようなホールを形成すること。

【解決手段】基板上にBおよびPの少なくとも一方を含むシリコン酸化物からなる第1の酸化膜と、その上に形成された、BおよびPを含まないシリコン酸化物からなる第2の酸化膜とを有し、さらに第1の酸化膜および第2の酸化膜の界面より下方に形成されたコンタクト部を有する被処理体を準備し(ステップ1)、第2の酸化膜と前記第1の酸化膜をエッチングしてコンタクト部に到達するホールを形成し(ステップ2)、HFガスおよび不活性ガスを用いたドライプロセスにより第1の酸化膜をエッチングし、第1の酸化膜のコンタクト部上方領域のホール部分を広げる(ステップ3)。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】リークパスを確実に防止することができる、半導体装置及び半導体装置の製造方法を提供する。

【解決手段】半導体装置は、ゲート絶縁膜を介して半導体基板上に設けられたゲート電極と、前記ゲート電極の側部に設けられた側壁絶縁膜と、前記半導体基板内における前記ゲート絶縁膜を挟むような位置に形成され、前記側壁絶縁膜により覆われた被覆領域と前記側壁絶縁膜により覆われていない露出領域とを有する、ソース又はドレイン領域と、前記ゲート電極及び前記側壁絶縁膜を覆うように形成された、エッチングストッパ膜と、前記半導体基板上に、前記エッチングストッパ膜を埋め込むように設けられた、層間絶縁膜と、前記層間絶縁膜を貫通するように設けられ、前記露出領域に接続される、第1セルコンタクトプラグとを具備する。前記エッチングストッパ膜は、前記被覆領域と前記露出領域との境界部分が完全に覆われるように、前記露出領域の一部を覆っている。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】半導体装置の信頼性を向上させる。

【解決手段】複数のゲート電極3bを覆うように窒化シリコン膜(第1絶縁膜)5を形成した後、オゾンTEOS膜(第1酸化シリコン膜)6、プラズマTEOS膜(第2酸化シリコン膜)を順次積層する。ここで、オゾンTEOS膜6を積層後、プラズマTEOS膜を積層する前に、窒化シリコン膜5をCMPストッパ膜として、CMP法により研磨する。これにより、プラズマTEOS膜の膜厚を均一化させることができるので、半導体装置の信頼性を向上させることができる。

(もっと読む)

半導体装置及びその製造方法

【課題】ストレッサ膜を有する半導体装置及びその製造方法に関し、ストレッサ膜からの応力を効率よくチャネル領域に印加してMISFETの電流駆動能力を向上しうる半導体装置及びその製造方法を提供する。

【解決手段】半導体基板に、素子領域を画定する素子分離絶縁膜を形成し、素子領域上に、ゲート絶縁膜を介してゲート電極を形成し、ゲート電極の両側の半導体基板内にソース/ドレイン領域を形成し、ゲート電極及びソース/ドレイン領域が形成された半導体基板上に第1の絶縁膜を形成し、素子分離絶縁膜の端部に生じた窪み内に第1の絶縁膜が残存するように第1の絶縁膜をエッチバックし、半導体基板上に、半導体基板の表面に平行な方向に応力を印加する第2の絶縁膜を形成する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】ビアに位置ずれが生じても、ビアがエアギャップにつながることを抑制できるようにする。

【解決手段】複数の配線240は例えばCu配線であり、互いに平行に延伸している。側壁絶縁膜212は、複数の配線240それぞれの側壁に形成されている。エアギャップは、複数の配線240それぞれの相互間に形成され、複数の側壁絶縁膜212の間に位置している。絶縁膜302は、複数の配線240上、複数の側壁絶縁膜212上、およびエアギャップ214上に形成されている。ビア344は絶縁膜302を貫通しており、いずれかの配線240に接続している。そして側壁絶縁膜212は、絶縁膜302がエッチングされる条件では絶縁膜302よりエッチングレートが低い材料により形成されている。

(もっと読む)

半導体装置及びその製造方法

【課題】信頼性の高い半導体装置を高い製造歩留まりで提供し得る半導体装置及びその製造方法を提供する。

【解決手段】第1応力膜38上に第1ストッパ膜39及び第2ストッパ膜40を形成する工程と、第1領域2を覆う第1マスク60をマスクとし、第1ストッパ膜をストッパとして、第2領域4内の第2ストッパ膜をエッチングするとともに、第1領域のうちの第2領域に近接する部分の第2ストッパ膜をサイドエッチングする工程と、第2ストッパ膜とエッチング特性が異なる第2応力膜42を形成する工程と、第2領域を覆い、第1領域側の端面が第2ストッパ膜上に位置する第2マスクとし、第2ストッパ膜をストッパとして、第2応力膜の一部が第1応力膜の一部及び第2ストッパ膜の一部と重なり合うように第2応力膜をエッチングする工程と、第1領域と第2領域との境界部におけるゲート配線20に達するコンタクトホールを形成する工程とを有している。

(もっと読む)

薄膜トランジスタ表示板の製造方法

【課題】エッチング工程時に銅が露出して不純物が発生することを最小化できる薄膜トランジスタ表示板の製造方法を提供する。

【解決手段】絶縁基板の上にゲート線124、ゲート絶縁膜140、第1非晶質シリコン膜154、第2非晶質シリコン膜164、第1金属膜174a、及び第2金属膜174bを順次形成する段階と、第2金属膜174bの上に第1部分と第1部分より厚さの厚い第2部分とを有する感光膜パターン52を形成する段階と、感光膜パターン52をマスクとして第2金属膜174b及び第1金属膜174aをエッチングして、第2金属パターン及び第1金属パターンを形成する段階と、第2金属パターンにSF6気体またはSF6とHeの混合気体で前処理する段階とを含む。

(もっと読む)

SiCの除去法

【課題】基板に形成されたカーバイドシリコン層の少なくとも露出された部分を除去するための方法を提供する。

【解決手段】カーバイドシリコン層45を酸素含有プラズマに曝すことにより、前記カーバイドシリコン層45の少なくとも露出された部分を酸化シリコン層に変換し、そして基板から前記酸化シリコン層を除去するステップからなる。

(もっと読む)

半導体装置の作製方法

【課題】電気的特性が向上した、酸化物半導体を用いた半導体装置の作製方法を提供することを目的の一とする。

【解決手段】酸化物半導体膜と、酸化物半導体膜と重畳するゲート電極と、酸化物半導体膜と電気的に接続するソース電極およびドレイン電極と、を有する半導体装置の作製方法であって、酸化物半導体膜上に接して、酸化ガリウムを含む第1の絶縁膜を形成し、第1の絶縁膜上に接して第2の絶縁膜を形成し、第2の絶縁膜上にレジストマスクを形成し、第1の絶縁膜および第2の絶縁膜にドライエッチングを行ってコンタクトホールを形成し、レジストマスクを、酸素プラズマによるアッシングを用いて除去し、コンタクトホールを介して、ゲート電極、ソース電極またはドレイン電極のいずれか一または複数と電気的に接続される配線を形成する、半導体装置の作製方法である。

(もっと読む)

半導体装置の製造方法

【課題】溝部を絶縁膜で埋設する際に、溝部のアスペクト比が大きい場合であっても、内部にボイドを残存させることなく、溝部内に絶縁膜を充填する。これにより微細化した半導体装置の製造を容易に行うことを可能とする。

【解決手段】隣り合う凸部の間に形成される溝部の上端部においてオーバーハング形状を有すると共に、溝部の上部にボイドを有するように溝部内に溝部用絶縁膜を形成する。凸部の高さ方向に対して斜め方向から、溝部用絶縁膜に不純物をイオン注入することにより、溝部内に形成された溝部用絶縁膜の一部に不純物をドープする。溝部用絶縁膜の不純物がドープされた部分を除去した後、溝部内に溝部用絶縁膜を充填する。

(もっと読む)

半導体装置

【課題】コンタクト抵抗の上昇を防止することが可能な半導体装置を提供すること。

【解決手段】シリコン基板に形成される複数の拡散領域と、複数の拡散領域にボトム部が接続して形成される複数のコンタクトプラグ33と、ボトム部を含んでシリコン基板上に形成されるアモルファスカーボン膜24とを備え、ボトム部はアモルファスカーボン膜24を貫通して拡散領域に接合される。アモルファスカーボン層24をコンタクトプラグ33形成時のエッチングストッパ層として用いることで、拡散領域がオーバーエッチングによりダメージを受けることが防止される。

(もっと読む)

半導体装置およびその製造方法

【課題】高い耐電圧特性、および耐リーク特性を有する配線構造を有する半導体装置およびその製造方法を提供する。

【解決手段】半導体素子が設けられた基板と、前記基板上に形成された第1および第2の配線と、前記第1の配線の下面の前記第2の配線側に接続されたビアと、前記ビアを含むビア層絶縁膜と、を有する半導体装置を提供する。前記ビアは、前記第1の配線と前記第2の配線の間の領域である配線間領域下の上端に凹部を有する。前記ビア層絶縁膜は、前記第1および第2の配線の幅方向に前記ビアと隣接する領域を含む溝を前記配線間領域の下に有する。前記配線間領域および前記溝内にはエアギャップが含まれる。

(もっと読む)

半導体素子及びその製造方法

【課題】半導体素子のビア構造物及び導電構造物を提供する。

【解決手段】前記ビア構造物は、平坦部及び突出部を含む表面を有する。前記導電構造物は前記平坦部のうち、少なくとも一部上に形成され、前記突出部のうち、少なくとも一部上には形成されない。例えば、前記導電構造物は前記平坦部上のみに形成されて前記突出部上には全く形成されない。これによって、前記導電構造物と前記ビア構造物との間に高品質の接続を形成することができる。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】CMOS回路を構成するnチャネルMISFETとpチャネルMISFETの両者において、キャリア移動度を高めて高い性能を実現する半導体装置を提供する。

【解決手段】半導体基板の第1領域及び第2領域において第1ゲート絶縁膜及び第1ゲート電極(16,17)を形成し、第1ゲート電極の両側部における半導体基板中にソースドレイン領域を形成し、ソースドレイン領域の導電性不純物を活性化し、第1ゲート電極を被覆して全面に半導体基板に応力を印加するストレスライナー膜(27,28)を形成し、少なくとも第1領域に形成された部分のストレスライナー膜は残しながら第2領域における第1ゲート電極の上部部分のストレスライナー膜を除去し、第2領域における第1ゲート電極の上部を露出させて第1ゲート電極を全て除去して第2ゲート電極形成用溝Tを形成し、第2ゲート電極形成用溝内に第2ゲート電極(31,32)を形成する。

(もっと読む)

半導体装置の製造方法

【課題】信頼性が損なわれるのを防止しつつ、電気的特性の良好な半導体装置を提供する。

【解決手段】半導体基板10上に、化学気相堆積法により、シリコンと酸素と炭素とを含む絶縁膜42を形成する工程と、絶縁膜を形成する工程の後、350℃以下の温度で加熱しながら絶縁膜に対して紫外線キュアを行う工程と、紫外線キュアを行う工程の後、絶縁膜に対してヘリウムプラズマ処理を行う工程とを有している。

(もっと読む)

配線形成方法

【課題】配線層で、配線密度の高い領域では隣接する配線間のショートを防ぎ、配線密度の低い領域では所望の平坦度が得られるとともに所望の配線抵抗が得られるように配線高さを制御できる配線形成方法を提供する。

【解決手段】まず、基板上に第1の絶縁膜111と、第1の絶縁膜111に比してCMP研磨レートの小さい所定の厚さの第2の絶縁膜112を順に積層させて層間絶縁膜11を形成し、ついで、層間絶縁膜11の第1の領域に第1の配線密度となり、第2の領域に第1の配線密度よりも低い第2の配線密度となるように、第2の絶縁膜112を貫通し、底部が第1の絶縁膜111に至る配線形成用溝21を形成した後、配線形成用溝21を形成した層間絶縁膜11上に導電性材料膜14を形成し、そして、CMP法によって、少なくとも第1の領域で第1の絶縁膜111が露出、後退するように層間絶縁膜11と導電性材料膜14を研磨する。

(もっと読む)

半導体装置及びその製造方法

【課題】下層の金属配線のダメージがなく上層の金属配線が形成され、かつ、配線間の寄生容量が低減された半導体装置及びその製造方法を提供する。

【解決手段】本発明に係る半導体装置は、半導体基板上に設けられた第1の金属配線層と、

前記第1の金属配線層上に設けられ、該第1の金属配線層の金属の拡散を防止する拡散防止膜と、前記拡散防止膜上に設けられた第1の絶縁膜と、前記第1の絶縁膜上に設けられた、前記拡散防止膜と同じ材料からなる第2の絶縁膜と、前記第2の絶縁膜上に設けられた第3の絶縁膜と、前記拡散防止膜、前記第1の絶縁膜、前記第2の絶縁膜及び前記第3の絶縁膜に形成された接続孔に充填され、前記第1の金属配線層に電気的に接続された第2の金属配線層と、を備えたことを特徴とする。

(もっと読む)

半導体装置とその製造方法

【課題】 相互接続配線とその上方のキャップ層との接着力を向上することが可能な半導体装置とその製造方法を提供する。

【解決手段】 半導体基板101上の誘電体層305中にその上面に自然酸化膜を含む金属の相互接続配線310を形成し、誘電体層及び前記金属の相互接続配線の少なくとも一部を覆いマンガン原子又はイオンを含む第1のキャップ層405を形成し、第1のキャップ層405上に絶縁体である第2のキャップ層410形成し、自然酸化膜及び第1のキャップ層は、第1のキャップ層と相互接続配線との間に酸化マンガンを形成するために反応する。

(もっと読む)

半導体装置の製造方法

【課題】コンタクトの抵抗値のばらつきを抑え、歩留りを安定させることが可能な半導体装置の製造方法を提供する。

【解決手段】半導体基板上に形成された導電層上に、絶縁膜を形成し、ハロゲンガスを含む第1のガスを用いて絶縁膜をドライエッチングして、導電層の表面を露出させ、露出した導電層に対しハロゲンガスを還元可能な第2のガスを用いて第1のプラズマ処理を行い、露出した導電層に対しC元素及びO元素を含みハロゲン元素を含まない第3のガスを用いて、第2のプラズマ処理を行う。

(もっと読む)

半導体素子、及びその形成方法

【課題】 信頼性が向上する半導体素子、及びその形成方法を提供する。

【解決手段】 半導体素子の形成方法は、半導体基板100の上にゲート電極120及びゲート電極120の両側にスペーサー110を形成する段階、ゲート電極120の上にキャッピングパターン170を形成する段階、ゲート電極120の間にメタルコンタクト195を形成する段階を含み、キャッピングパターン170の幅はゲート電極120の幅より大きく形成される。これにより、形成された半導体素子は、メタルコンタクト195とゲート電極120との間での電気的な短絡を效果的に防止することができる。

(もっと読む)

121 - 140 / 1,214

[ Back to top ]