Fターム[5F033TT02]の内容

半導体集積回路装置の内部配線 (234,551) | 絶縁膜の構造、形状 (4,088) | 積層構造 (1,984) | 全てが無機材料 (1,214)

Fターム[5F033TT02]に分類される特許

201 - 220 / 1,214

半導体装置の製造方法

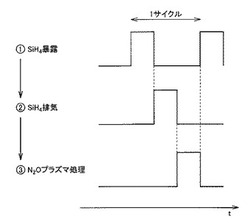

【課題】比較的低い温度のもとで、良質で、かつ、薄いシリコン酸化膜等を均一に形成することができる半導体装置の製造方法を提供する。

【解決手段】ステップ1では、半導体基板がモノシラン(SiH4)に暴露される。次に、ステップ2では、残存するモノシラン(SiH4)が排気される。そして、ステップ3では、半導体基板が亜酸化窒素プラズマに晒される。ステップ1〜3を1サイクルとして、必要とされる膜厚が得られるまでこのサイクルを繰り返すことで、所望のシリコン酸化膜が形成される。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】配線絶縁膜としてSiOCH膜を用いる場合に、ビアホールの開口径に依らず、その加工制御性を十分に得て、下層Cu配線の表面の組成のバラツキを十分に抑制する。

【解決手段】下層Cu配線3上に形成されている積層構造20は、シリコンと炭素を含有するキャップ絶縁膜4と、キャップ絶縁膜4上に形成されている配線絶縁膜5としてのSiOCH膜を有する。積層構造20にビアホール8、9を形成する工程は、第1及び第2ドライエッチングを組み合わせて行う。第1ドライエッチングでは開口径が小さいビアホール9のエッチングレートが、開口径が大きいビアホール8のエッチングレートよりも大きくなるようにO2濃度が設定された第1混合ガスを用いる。第2ドライエッチングではビアホール8のエッチングレートがビアホール9のエッチングレートよりも大きくなるようにO2濃度が設定された第2混合ガスを用いる。

(もっと読む)

ビアホールの形成方法

【課題】異なる種類の絶縁体が積層された構造を有する絶縁膜に、高精度の加工形状を有するビアホールを形成することができるビアホールの形成方法を提供する。

【解決手段】

ドライエッチングによって第2の絶縁層に第1の貫通孔を形成する工程と、第1の絶縁層及び第2の絶縁層の第1の貫通孔からの露出部分を同一組成からなる絶縁体にする同一化工程と、第1の貫通孔から露出する第1の絶縁層をドライエッチングにより除去して下層配線に達するビアホールを形成する工程と、を有すること。

(もっと読む)

半導体装置の製造方法

【課題】レジストスリミング幅のばらつきを抑制する半導体装置の製造方法を提供する。

【解決手段】本発明の半導体装置の製造方法は、シリコンを含む被加工層上にレジスト41を形成するレジスト形成工程と、処理室内にハロゲン元素を含むガスを導入し、レジスト41をマスクにして被加工層をハロゲン元素を含むガスを用いてエッチングするエッチング工程と、エッチング工程の後、同じ処理室内に酸素ガスとハロゲン元素を含むガスを導入し、酸素ガスとハロゲン元素を含むガスを用いてレジスト41の平面サイズを縮小するレジストスリミング工程と、を有する。

(もっと読む)

層間絶縁膜の平坦化方法

【課題】配線層による層間絶縁膜の凹凸の影響を排除することで、平坦化を容易とすることができる層間絶縁膜の平坦化方法を提供する。

【解決手段】層間絶縁膜の平坦化方法は、まず、配線層12a,12bを形成し、高密度プラズマCVDにより配線層12a,12bを覆って第1HDP酸化膜13を形成し、テトラエトキシシランガスを用いたプラズマCVDにより第1HDP酸化膜13上にPL−TEOS酸化膜14を形成し、高密度プラズマCVDによりPL−TEOS酸化膜14上に、第2HDP酸化膜15を形成する。次に、PL−TEOS酸化膜14が露出するまでCMPにより第2HDP酸化膜15を研磨する。そして、PL−TEOS酸化膜14が除去されるまで、第2HDP酸化膜15とPL−TEOS酸化膜14とを同時にCMPにより平坦化する。そうすることで、平坦化された層間絶縁膜10を得ることができる。

(もっと読む)

多層配線の形成方法

【課題】 工程数の増加がなく、しかも銅を使用している配線にダメージが及ぶ可能性も少ない多層配線の形成方法を提供すること。

【解決手段】 銅を使用している下層配線3上にエッチングストップ層5を形成し、エッチングストップ層5上に層間絶縁膜6を形成し、層間絶縁膜6にエッチングストップ層5に達する開孔7を形成し。層間絶縁膜6上に酸化マンガン膜8を形成し、酸化マンガン膜8を開孔7から露呈した層間絶縁膜6の表面に残しながら、下層配線3上に形成されたエッチングストップ層5を除去し、開孔7の底に下層配線3を露呈させ、開孔7の底に露呈した下層配線3上に、上層配線を形成する。

(もっと読む)

貫通電極基板及びその製造方法、並びに貫通電極基板を用いた半導体装置

【課題】基板の表裏を導通する導通部における電気特性を向上した貫通電極基板及びそれを用いた半導体装置を提供すること。

【解決手段】本発明の貫通電極基板100は、表裏を貫通する貫通孔104を有する基板102と、貫通孔104内に充填される金属材料を含む導通部106と、を備え、導通部106の一端は、導通部106の他端より面積重み付けした平均結晶粒径が大きい金属材料を少なくとも含む。また、導通部106は、結晶粒径が13μm以上の金属材料を含む。

(もっと読む)

電界効果トランジスタ

【課題】電流コラプス現象およびゲートリーク電流を抑制することが可能な電界効果トランジスタを提供する。

【解決手段】電界効果トランジスタ1は、基板10と、チャネル層11と、キャリア供給層12と、ソース電極21と、ドレイン電極22と、ゲート電極23と、ソース電極21とドレイン電極22との間でキャリア供給層12に積層されて電流コラプス現象を抑制する第1絶縁層31と、ドレイン電極22に対向する第1絶縁層31の端とドレイン電極22との間に形成された開口部40と、開口部40に露出したキャリア供給層12に積層された第2絶縁層32とを備える。

(もっと読む)

半導体装置の製造方法

【課題】配線表面の酸化膜を除去する際の低誘電率絶縁膜の変質を抑える半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、半導体基板10上のSiOC膜11表面に配線12を形成する工程と、配線12が表面に形成されたSiOC膜11を希ガス、又は希ガスとN2ガスの混合ガスを含むプラズマに曝してSiOC膜11表面に緻密層14を形成する工程と、緻密層14が形成された後に、配線12の表面に形成された酸化膜13を除去する工程と、酸化膜13が除去された配線12、及び緻密層14上に絶縁膜としての拡散防止膜15を形成する工程と、を含み、酸化膜13を除去する工程から拡散防止膜15を形成する工程までが、大気に暴露されることなく行われる。

(もっと読む)

半導体装置

【課題】高周波デバイスを形成する複数の素子を一つのチップに形成できる技術を提供する。

【解決手段】基板1上にて抵抗素子および容量素子の下部電極を同一の多結晶シリコン膜から形成し、前記多結晶シリコン膜とは異なる同一の多結晶シリコン膜およびWSi膜からパワーMISFETのゲート電極、容量素子の上部電極、nチャネル型MISFETのゲート電極およびpチャネル型MISFETのゲート電極を形成し、領域MIMにおいては基板1上に堆積された酸化シリコン膜30上に形成された配線を下部電極とし酸化シリコン膜34上に形成された配線を上部電極とする容量素子MIMCを形成し、酸化シリコン膜34上に堆積された酸化シリコン膜37上に堆積された同一のアルミニウム合金膜を用い領域INDにて配線39Aからなるスパイラルコイルを形成し、領域PADでは配線39Bからなるボンディングパッドを形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】電極パッドの損傷を抑制することができる半導体装置を提供する。

【解決手段】半導体基板11と、半導体基板11の上方に形成された電極パッド30とを有し、電極パッド30は、第1の融点温度を有する材料からなる第1の層32と、第1の層32上に位置するとともに外に向けて表出し、第1の融点温度よりも高い第2の融点温度を有する材料からなる第2の層33とを含むことを特徴とする。これにより、外部から電極パッド30への圧力により第1の層32に達する傷ができても、必要に応じて第1の融点以上の温度で加熱することにより電極パッド表面の平坦性を修復することができる。

(もっと読む)

半導体装置及びその製造方法

【課題】絶縁膜の表面に対するダメージを防ぎ、配線膜厚を均一に制御することにより、配線間ショート及び信頼性劣化を防止できるようにする。

【解決手段】半導体基板101の上に絶縁膜102を形成し、絶縁膜102の内部にイオン注入法によりイオン注入層103を形成し、絶縁膜102に少なくともイオン注入層103に達する深さの配線溝104を形成し、配線溝104に導電膜107Aを形成し、絶縁膜102及び導電膜107Aにおけるイオン注入層103よりも上に形成されている領域を除去する。

(もっと読む)

半導体装置の製造方法

【課題】パワーMOSFETにおいては、アルミニウム系ソース電極下のアルミニウム拡散バリア・メタル膜として、チタンおよび窒化チタンからなるチタン系バリア・メタル膜が広く使用されている。しかし、本願発明者らが検討したところによると、チタン系バリア・メタル膜を使用すると、ウエハの反りが増大して、ウエハ・ハンドリングが困難となり、ウエハ割れやウエハ欠け等の問題が不可避となることが明らかとなった。この傾向は、最小寸法が0.35マクロ・メートル以下の製品において特に顕著である。

【解決手段】本願発明は、アルミニウム系メタル層と下層のシリコン系半導体層の間のバリア・メタル層として、タングステン系バリア・メタル膜(TiW等のタングステンを主要な成分とする合金膜)をスパッタリング成膜によって形成する際、スパッタリング成膜チャンバの気圧を1.2パスカル以下とするものである。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】本発明は、薄膜トランジスタのソース領域やドレイン領域へのコンタクトを確実

にした半導体装置を提供するものである。

【解決手段】本発明における半導体装置において、半導体層上の絶縁膜およびゲイト電極

上に形成された第1の層間絶縁膜と、前記第1の層間絶縁膜の上に形成された第2の層間

絶縁膜と、前記第2の層間絶縁膜、前記第1の層間絶縁膜、および前記絶縁膜に設けられ

たコンタクトホールとを有する。前記第1の絶縁層の膜厚は、前記積層の絶縁膜の合計膜

厚の1/3以下に形成する。

(もっと読む)

フレキシブル半導体デバイスを高温で提供する方法およびそのフレキシブル半導体デバイス

いくつかの実施例は、半導体デバイスを提供する方法を含む。当該方法は、

(a)フレキシブル基板を提供する段階、(b)フレキシブル基板上に少なくとも1つの材料層を堆積させる段階であって、そのフレキシブル基板上の少なくとも1つの材料層の堆積は、少なくとも180℃の温度で生じる、段階、および(c)金属層とa−Si層との間に拡散バリアを提供する段階を含む。他の実施例も本願において開示される。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】高温環境下での絶縁膜の腐食を抑制して、絶縁不良を回避した半導体装置及びその製造方法を提供することことを課題とする。

【解決手段】半導体基板11上にエピタキシャル成長により第1絶縁膜12が積層形成され、この第1絶縁膜12上には、耐熱性の電極13が選択的に形成され、この電極13の上部には、シリカガラスを主成分とする層間絶縁膜14が形成され、この層間絶縁膜14の表面には絶縁バリア膜15が形成され、この絶縁バリア膜15の上には、Alの配線16が形成され、絶縁バリア膜15は、絶縁性の窒化物、炭化物、窒化炭化物の単層膜、多層膜、または混合膜で構成されている。

(もっと読む)

配線層レイアウト方法及び半導体装置

【課題】配線層にスリットを設けたり、下層に位置する配線層にライン幅及びスペース間隔の比率を制限したりすることなく、SOG膜を含む層間絶縁膜におけるクラックの発生を防止する。

【解決手段】下地絶縁膜3上に第1配線層5が形成されている。下地絶縁膜3上及び第1配線層5上に第1層間絶縁膜7が形成されている。回転塗布法及びエッチバック処理により第1層間絶縁膜7上に第2層間絶縁膜9が形成されている。第1層間絶縁膜7上及び第2層間絶縁膜9上に第3層間絶縁膜11が形成されている。第3層間絶縁膜11上に第2配線層13が形成されている。第1配線層5のうち幅寸法が10.0μm以上の幅広第1配線層5に対して、第2配線層13のうち幅寸法が10.0μm以上の幅広第2配線層13は、上方から見て、幅広第1配線層5と1.0μm以上の重なりをもって配置されているか、幅広第1配線層5とは2.0μm以上の間隔を設けて配置されている。

(もっと読む)

半導体装置およびその製造方法

【課題】平坦な表面を有する層間絶縁膜を短時間で形成することができ、また、層間絶縁膜の厚さの増大を招くことなく、金属イオンによる半導体基板の汚染に対する長期信頼性を保証することができる、半導体装置およびその製造方法を提供する。

【解決手段】半導体装置1は、半導体基板2と、半導体基板2上に形成された層間絶縁膜8とを備えている。そして、層間絶縁膜8は、半導体基板2側から順に、HDP膜10、ゲッタリング層12およびNSG膜11が積層された構造を有している。ゲッタリング層12は、金属イオン、とくに可動イオンを捕獲する性質を有している。

(もっと読む)

半導体装置の製造方法

【課題】保護素子としてSBDを搭載したMOSFETにおいては、SBDの特性を確保するためアルミニウム・ソース電極下のアルミニウム拡散バリア・メタル膜として、TiW(タングステンを主要な成分とする合金)膜が使用される。しかし、本願発明者らが検討したところによると、タングステン系バリア・メタル膜はTiN等のチタン系バリア・メタル膜と比べて、バリア性が低い柱状粒塊を呈するため、比較的容易にシリコン基板中にアルミニウム・スパイクが発生することが明らかとなった。

【解決手段】本願発明は、アルミニウム系メタル層と下層のシリコン系半導体層の間のバリア・メタル層として、タングステン系バリア・メタル膜をスパッタリング成膜によって形成する際、その下層をウエハ側にバイアスを印加したイオン化スパッタにより成膜し、上層をウエハ側にバイアスを印加しないスパッタにより成膜するものである。

(もっと読む)

半導体装置及びその作製方法

【課題】酸化物半導体層を用いた薄膜トランジスタにおいて、酸化物半導体層とソース電極層又はドレイン電極層との間のコンタクト抵抗を低減し、電気特性を安定させた薄膜トランジスタを提供する。

【解決手段】酸化物半導体層を用いた薄膜トランジスタにおいて、酸化物半導体層の上に高抵抗領域及び低抵抗領域を有するバッファ層を形成し、酸化物半導体層とソース電極層又はドレイン電極層とがバッファ層の低抵抗領域を介して接触するように薄膜トランジスタを形成する。

(もっと読む)

201 - 220 / 1,214

[ Back to top ]