Fターム[5F033TT02]の内容

半導体集積回路装置の内部配線 (234,551) | 絶縁膜の構造、形状 (4,088) | 積層構造 (1,984) | 全てが無機材料 (1,214)

Fターム[5F033TT02]に分類される特許

141 - 160 / 1,214

半導体装置の製造方法

【課題】信頼性の向上に寄与し得る半導体装置の製造方法を提供する。

【解決手段】半導体基板10にトランジスタ36を形成する工程と、半導体基板上に、トランジスタを覆う第1のシリコン窒化膜38を形成する工程と、第1のシリコン窒化膜にNH4Fラジカルを供給する工程と、NH4Fラジカルを供給する工程の後、第1のシリコン窒化膜に対して熱処理を行う工程と、熱処理を行う工程の後、第1のシリコン窒化膜上に第2のシリコン窒化膜を形成する工程とを有している。

(もっと読む)

半導体装置

【課題】本発明は、薄膜トランジスタのソース領域やドレイン領域へのコンタクトを確実

にした半導体装置を提供するものである。

【解決手段】本発明における半導体装置において、半導体層上の絶縁膜およびゲイト電極

上に形成された第1の層間絶縁膜と、前記第1の層間絶縁膜の上に形成された第2の層間

絶縁膜と、前記第2の層間絶縁膜、前記第1の層間絶縁膜、および前記絶縁膜に設けられ

たコンタクトホールとを有する。前記第1の絶縁層の膜厚は、前記積層の絶縁膜の合計膜

厚の1/3以下に形成する。

(もっと読む)

半導体集積回路装置および半導体集積回路装置の製造方法

【課題】TSVを形成した後の工程においては、Cuの拡散防止膜である絶縁膜形成後に、当該絶縁膜に割れが発生し、その後のエッチングやアッシングなどのパターン加工を行う工程において、露出したCuが変色する問題が発生する場合がある。これは、拡散防止膜の成膜工程における熱履歴によりCuが体積膨張したことが問題の要因と考えられる。このような、膜割れが発生した場合には、Cu拡散防止膜の機能破壊、TSV上部のCuの酸化による上部配線との導通不良等の種々の問題を誘発する。

【解決手段】本願の一つの発明は、貫通電極を有する半導体集積回路装置において、プリメタル配線層形成よりも後に貫通ビアを形成する場合において、貫通電極の上端に当たる層間絶縁膜の界面に、メタル拡散防止絶縁膜として、窒化シリコン系絶縁膜を使用し、それ以外の層間絶縁膜の界面に、メタル拡散防止絶縁膜として、炭化シリコン系の絶縁膜を使用するものである。

(もっと読む)

半導体基板および半導体基板の製造方法

【課題】ボンディングワイヤが接続されたボンディングパッドを一面に有する半導体基板において、ワイヤの接続によるボンディングパッド下部のクラックの発生を適切に検出できるようにする。

【解決手段】半導体基板1の内部にてボンディングパッド10の下部には、当該半導体基板1の特性を検査するための検査用配線40が設けられており、検査用配線40は、ボンディングパッド10のうちボンディングワイヤ70の端部が位置する部位の直下に配置されている。

(もっと読む)

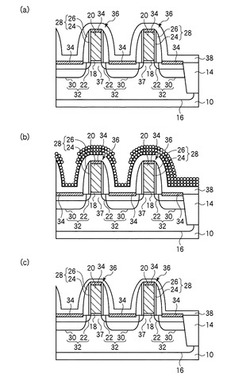

半導体装置およびその製造方法

【課題】無機材料を用いてコストの低減を図りながら、応力集中によるクラックを回避しつつ、銅配線を覆うことができるパッシベーション膜を有する半導体装置およびその製造方法を提供する。

【解決手段】半導体装置10は、層間絶縁膜25と、層間絶縁膜25上に突出して形成され、銅を主成分とする材料からなる配線27と、配線27を覆うように形成されたパッシベーション膜30とを含む。パッシベーション膜30は、配線27側から順に第1窒化膜31、中間膜33および第2窒化膜32を積層した積層膜からなる。中間膜33は、第1および第2窒化膜31,32とは異なる絶縁材料(たとえば酸化物)からなる。

(もっと読む)

半導体装置及びその製造方法

【課題】層間絶縁膜が剥離しにくい半導体装置及びその製造方法を提供する。

【解決手段】半導体装置の製造方法において、複数のデバイス領域がスクライブライン領域によって区画された半導体ウェーハ上に、層間絶縁膜内に配線及びビアが設けられた多層配線膜を形成する工程と、前記スクライブライン領域内に設定されたダイシング領域の一部に配置された前記多層配線膜及び前記半導体ウェーハを除去することにより、前記多層配線膜及び前記半導体ウェーハを前記デバイス領域毎に切り分ける工程と、を設ける。そして、前記多層配線膜を形成する工程において、前記スクライブライン領域における前記ダイシング領域を除く領域には、前記配線及び前記ビアを上下方向に連結させたダミーパターンを形成し、前記ダイシング領域における前記層間絶縁膜の少なくとも上部には、前記配線及び前記ビアを上下方向に連結させたダミーパターンを形成しない。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】本発明は、コンタクト電極の形状を改善し、コンタクト抵抗を低くすることがで

きる。

【解決手段】 半導体基板10と、半導体基板上10に形成されたゲート絶縁膜11と、

半導体基板10上にワード線方向に沿って配置され、ゲート絶縁膜11を介して形成され

た浮遊ゲート電極12と、浮遊ゲート電極12上に第1ゲート間絶縁膜13を介して形成

された制御ゲート14を有する複数のメモリセルトランジスタMCと、ゲート絶縁膜11

上に形成されたボトム電極32と、ゲート絶縁膜11及びボトム電極32に形成された開

口EIIを通じて半導体基板10に接するトップ電極33と、開口EIIの下に形成され

、半導体基板10と逆の不純物濃度の型である接続拡散層31とを有するビット線コンタ

クトBCとを備えたことを特徴とする。

(もっと読む)

半導体装置、半導体装置の製造方法、半導体装置の設計方法、及び電子機器

【課題】積層される半導体ウェハのそれぞれの性能を十分に発揮して高性能化を図り、且つ量産性、コスト低減を図った、固体撮像装置等の半導体装置とその製造方法を提供する。また、固体撮像装置を備えたカメラ等の電子機器を提供する。

【解決手段】第1の半導体ウェハ31と、第2の半導体ウェハ45とを、基板間配線68で接続する構成とする。基板間配線は、第1の半導体ウェハ31表面の第1の多層配線層に形成される接続孔66と、第2の半導体ウェハ45表面の第2の多層配線層に形成された貫通接続孔65とに、導電材料が埋め込まれて形成されている。そして、貫通接続孔65は接続孔66の直径よりも大きく形成されている。これにより、貫通接続孔65の構内に導電材料を埋め込む際のボイドの発生を防ぐ。

(もっと読む)

半導体装置の製造方法

【課題】ボイド、ディッシング、及びエロージョンの発生を抑制することのできる半導体装置の製造方法を提供する。

【解決手段】絶縁膜に幅の異なる複数の開口部36,37を形成し、次いで、絶縁膜の上面、及び幅の異なる複数の開口部内にシード層38を形成し、次いで、第1の成長速度により、シード層の表面を覆う第1のめっき膜71を形成し、次いで、第1の成長速度よりも速く、かつボイドを生じさせない第2の成長速度により、第1のめっき膜の表面に第2のめっき膜72を形成し、次いで、第2の成長速度よりも速い第3の成長速度により、第2のめっき膜上に第3のめっき膜73を形成し、その後、シード層及び第1乃至第3のめっき膜のうち、絶縁膜の上面よりも上方に形成された部分を研磨により除去することで、開口部内に少なくとも第1及び第2のめっき膜よりなる導電部を形成する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】半導体装置の広幅の配線におけるディッシングの抑制と、抵抗の抑制と、を両立させる。

【解決手段】半導体装置100は、半導体基板1と、半導体基板1上に形成された配線層絶縁膜9と、を有している。配線層絶縁膜9には、第1配線用配線溝11と、第1配線用配線溝11よりも広幅の第2配線用配線溝12と、が形成されている。第1配線用配線溝11内には第1配線21が、第2配線用配線溝12内には第2配線22が、それぞれ形成されている。第2配線用配線溝12の底面の少なくとも一部分は、絶縁膜(例えば、絶縁膜4及びエッチングストッパー膜5)によって、第2配線用配線溝12の上端に達しない高さで第1配線用配線溝11の底面よりもかさ上げされた、かさ上げ部15となっている。

(もっと読む)

集積回路装置及びその製造方法

【課題】チップ面積が小さく、製造コストが低い集積回路装置及びその製造方法を提供する。

【解決手段】集積回路装置の製造方法において、複数の第1絶縁層及び複数の第2絶縁層を1層ずつ交互に積層させて積層体を形成すると共に、少なくとも2層の前記第2絶縁層内に少なくとも2本の配線を形成する工程と、前記積層体における前記積層体の積層方向から見て前記配線から離隔した位置に、前記積層方向に延びるコンタクトホールを形成する工程と、前記第2絶縁層における前記コンタクトホールと前記配線との間の部分を除去する工程と、前記第2絶縁層が除去された部分及び前記コンタクトホールの内部に導電材料を埋め込む工程と、を実施する。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の製造方法において、ヒューズ層を覆う絶縁膜の膜厚を精度良く調整する。

【解決手段】半導体基板10上にザッピング素子1のヒューズ層12を形成し、ヒューズ層12を覆う第1の絶縁膜13を形成する。第1の絶縁膜13上にはヒューズ層12を覆うエッチングストッパー膜14を形成し、エッチングストッパー膜14を覆う第2の絶縁膜16を形成する。他の工程を経た後、第1のエッチング工程として、ヒューズ層12上で、第2の絶縁膜16をエッチングストッパー膜14に対して選択的にエッチングすることにより、エッチングストッパー膜14の表面を露出させる。次に、第2のエッチング工程として、ヒューズ層12上で、エッチングストッパー膜14を第1の絶縁膜13に対して選択的にエッチングすることにより、第1の絶縁膜13の表面を露出させる。

(もっと読む)

低水分誘電体膜を形成する方法

半導体装置及びその製造方法

【課題】リーク電流が低く、電界効果移動度が高いなどの優れた特性を有するTFTを備え、駆動回路を内蔵して部材点数を減らすことが可能な半導体装置において、駆動回路内部における腐食などの発生を防止する。

【解決手段】本発明の半導体装置においては、駆動回路を内蔵したTFTアレイ基板100に、ゲート電極2と、ゲート絶縁膜3と、結晶性半導体部分を含んでチャネル領域4cが形成される半導体層4と、チャネル領域4cを保護するチャネル保護膜5と、半導体層4に接続されたソース電極6及びドレイン電極7を備えたTFT、並びに、ゲート電極2と同層に形成された配線層2aとソース電極6と同層に形成された配線層6aを駆動回路内部においてコンタクトホール13を介し直接接触させて接続させる配線変換部12を備えるものである。

(もっと読む)

半導体装置

【課題】 パッド内での過度の電流集中を抑制することが可能なパッド構造を有する半導体装置を提供する。

【解決手段】 半導体基板の上に、絶縁性材料からなる第1の絶縁膜が形成されている。第1の絶縁膜の上に、導電材料からなるパッド部が形成されている。パッド部に電気的に連続し、第1の幅W1を有する配線部が形成されている。第1の絶縁膜の上であって、パッド部の外周線から第2の幅W2より内側の第1の領域に、複数の第2の絶縁膜が配置されている。配線部とパッド部との境界線に最も近い第2の絶縁膜を連ねる直線のうち、配線部をパッド部内に延長した領域と重なる部分が、パッド部の導電材料と交差する長さをL3としたとき、W1≦2×W2+L3を満たす。

(もっと読む)

表示装置およびその製造方法

【課題】ゲート絶縁層内に拡散する汚染元素によってトランジスタ特性が低下するのを防止した薄膜トランジスタを有する表示装置、および、その製造方法を提供することを目的とする。

【解決手段】基板101の上側に積層された半導体層104と、半導体層104の上側に積層されるゲート電極106と半導体層104とゲート電極106との間に積層されるゲート絶縁層105と、ソース電極112およびドレイン電極111と、を含む薄膜トランジスタを有する表示装置であって、ソース電極112およびドレイン電極111の少なくとも一方は、ゲート絶縁層105の上側に形成されて、ゲート絶縁層105に形成されるコンタクトホール109を介して半導体層に接続され、コンタクトホール109の側壁には、窒素化合物を含む側壁膜110が形成される、ことを特徴とする表示装置。

(もっと読む)

半導体装置の製造方法

【課題】 組み立て工程やCMP工程時における剥離を抑制した、低誘電率層間絶縁膜の製造方法とそれを用いた半導体装置を提供する。

【解決手段】低誘電率層間絶縁膜の成膜の際、高周波と低周波の2周波を切り替え、膜厚方向に膜特性の変調をかけることで、低誘電率を保持したまま密着強度を向上させる。プラズマ発生のための高周波と低周波が同一電極から印加される。そして絶縁膜の成膜開始時あるいは成膜終了時の少なくとも一方において、低周波の入力が成膜開始時及び成膜終了時を除いた他のタイミングより高い。例えば絶縁膜は、厚さ方向における少なくともどちらか一方の端部が、高周波と低周波の2周波により密着層となり、密着層以外の部分は低周波の入力を低下あるいは0にすることで低誘電率絶縁膜となる。

(もっと読む)

半導体装置

【課題】SRAM回路の動作速度を向上させる。

【解決手段】駆動MISFETと転送MISFETとそれらの上部に形成された縦型MISFETとでメモリセルを構成したSRAMにおいて、周辺回路を構成するMISFET間の電気的接続を、メモリセルの縦型MISFET(SV1、SV2)よりも下部に形成されるプラグ28および中間導電層46、47で行うとともに、縦型MISFET(SV1、SV2)よりも上部に形成されるプラグ、第1および第2金属配線層を用いて行うことにより、配線の自由度を向上でき、高集積化できる。また、MISFET間の接続抵抗を低減でき、回路の動作スピードを向上できる。

(もっと読む)

半導体装置とその製造方法、及び電子機器

【課題】寄生容量を低減し、高性能化を図った固体撮像装置等の半導体装置とその製造方法、前記固体撮像装置を備えたカメラ等の電子機器を提供するものである。

【解決手段】本発明の半導体装置は、2つ以上の半導体チプ部22,26が貼り合わされた積層半導体チップ27を有する。積層半導体チップ27では、少なくとも第1の半導体チップ部22に画素アレイ23と多層配線層41が形成され、第2の半導体チップ部26にロジック回路25と多層配線層55が形成される。第1の半導体チップ部22には、一部の半導体部分が全て除去された半導体除去領域52が形成され、半導体除去領域52内に第1の半導体チップ部22と第2の半導体チップ部26との間を接続する複数の接続配線67が形成される。この半導体装置は、裏面照射型の固体撮像装置として構成される。

(もっと読む)

半導体装置

【課題】電極パッドからの水分の拡散を防止できると共に、絶縁膜の薄膜化及び低誘電率化に対応できるようにする。

【解決手段】半導体装置は、半導体基板11の上方に形成され、外部との電気的な接続を取る接続部25である電極パッドと、半導体基板と接続部との間に積層された絶縁膜14等にそれぞれ形成され、上層の配線34が接続部と接続された複数の第1配線層及び該第1配線層同士を接続するビア31よりなる積層構造体27と、複数の絶縁膜に積層構造体の周囲を隙間なく囲むように形成され、複数の第2配線層40等及び該第2配線層同士を線状に接続するラインビア41よりなるリング構造体28と、接続部と内部回路とを電気的に接続する引き出し配線32Aとを有している。積層構造体とリング構造体とは複数の第1配線層の少なくとも1つによって互いに接続されており、引き出し配線はリング構造体と接続されている。

(もっと読む)

141 - 160 / 1,214

[ Back to top ]