Fターム[5F033TT07]の内容

半導体集積回路装置の内部配線 (234,551) | 絶縁膜の構造、形状 (4,088) | 側壁絶縁膜 (2,038) | コンタクトホールの側壁 (799)

Fターム[5F033TT07]に分類される特許

101 - 120 / 799

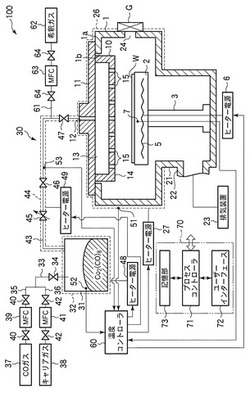

成膜方法および記憶媒体

【課題】成膜原料としてコバルトカルボニルを用いてCo膜を成膜する場合に、下地との密着性を良好にすることができる成膜方法を提供すること。

【解決手段】処理容器1内に基板Wを配置し、処理容器1内に気体状のコバルトカルボニルを供給し、基板W上でコバルトカルボニルを熱分解させて基板W上にCo膜を成膜するにあたり、基板WのCo膜の下地が、Co膜との界面近傍に混合層を形成する材料で構成されており、基板Wの加熱温度を190〜300℃とする。

(もっと読む)

半導体素子及びその形成方法

【課題】半導体素子及びその形成方法に関し、工程マージンを向上させる。

【解決手段】半導体素子は、半導体基板10に備えられるメインゲート20及び素子分離構造、前記素子分離構造の上部に備えられる分離パターン40及び前記分離パターンの両端に備えられるコンタクトプラグ54を含む。格納電極コンタクトと活性領域との間のフルオーバーラップを提供し、食刻工程でのオーバーレイ問題を解消し、格納電極の食刻線幅を増加させる。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】コストが低い半導体記憶装置及びその製造方法を提供する。

【解決手段】実施形態に係る半導体記憶装置の製造方法は、絶縁膜及び電極膜が交互に積層された積層体を形成する工程と、前記積層体上に、サイズが相互に異なる複数のホールが形成されたハードマスクを形成する工程と、マスク材料を堆積させることにより、最も小さい前記ホールを閉塞させると共に、その他の前記ホールを小さくする工程と、前記マスク材料及び前記ハードマスクをマスクとしてエッチングを施すことにより、前記その他のホールの直下域において、各所定枚数の前記絶縁膜及び前記電極膜を除去して、コンタクトホールを形成する工程と、前記コンタクトホールを介してエッチングを施すことにより、前記電極膜の一部分を除去して隙間を形成する工程と、前記隙間内に絶縁材料を埋め込む工程と、前記コンタクトホール内に導電材料を埋め込む工程と、を備える。

(もっと読む)

半導体装置

【課題】貫通電極の形成に時間を要さず、貫通電極内でのボイドの発生を抑制できる半導体装置、およびこの半導体装置の製造方法を提供すること。

【解決手段】半導体装置1は、孔111が形成された絶縁性あるいは半導体の層11と、層11の孔111内に設けられた貫通電極12と、を備える。貫通電極12は、シード層121と、めっき層122と、を備える。シード層121は、孔111の底面111Aを覆う。また、シード層121は、孔111の側面111Bのうち、孔111の開口から、孔111の開口と孔111の底面111Aとの間の所定の位置までの第1の領域を未被覆とし、この第1の領域(未被覆領域)111B1を除いた第二の領域を被覆している。めっき層122は、シード層121と、未被覆領域111B1の少なくとも一部を覆う。

(もっと読む)

半導体素子及びその製造方法

【課題】絶縁膜を貫通するコンタクトプラグの抵抗を改善させられる半導体素子及びその製造方法を提供する。

【解決手段】半導体基板上に形成された第1層間絶縁膜と、前記第1層間絶縁膜を貫通して形成されたコンタクトホールと、前記コンタクトホールの内部に形成されたコンタクトプラグと、前記コンタクトホール内で前記コンタクトプラグの上部側壁を部分的に覆うスペーサと、を含む。

(もっと読む)

ヴィア構造およびその作製方法

【課題】より小さな径の基板貫通ヴィアが形成できるようにする。

【解決手段】基板101の回路が形成されている主表面101a側から所望の孔径の範囲で形成可能な深さに形成された第1孔部102と、基板101の裏面側から形成されて第1孔部102に接続する第2孔部103と、第1孔部102の内部に形成された第1孔部配線104と、第1孔部配線104に接続して基板101の主表面101a側に形成された表面配線層105と、第2孔部103の内部に第1孔部配線104に接続して形成された第2孔部配線106と、第2孔部配線106に接続して基板101の裏面側に形成された裏面配線層107とを備える。

(もっと読む)

半導体装置

【課題】埋め込み電極プラグからの応力伝播による半導体装置の特性変動、および、埋め込み電極プラグからの電気的雑音伝播による、半導体装置の動作不安定化を防止する。

【解決手段】半導体基板と、半導体基板上に形成された半導体素子を有する素子形成領域と、半導体基板を貫通するように設けられた1以上の埋め込み電極プラグと、素子形成領域と埋め込み電極プラグの間の半導体基板内に位置するトレンチ内に埋め込まれた溝型電極と、を有する半導体装置。

(もっと読む)

半導体装置

【課題】封止される被対象物に段差部を備えているが、封止部を設けた際に該段差部に起因したボイドの発生が抑制され、ひいては優れた耐食性を備える半導体装置と、その製造方法を提供する。

【解決手段】本発明に係る半導体装置1は、導電性を有する剛体からなる基板2と、該基板の少なくとも一方の面に絶縁部3を介して配された導電部5と、該絶縁部及び該導電部を覆うように配された感光性樹脂からなるフィルム6と、を備えている。前記基板2は、一方の面に開口する凹部及び/又は貫通孔2aを備え、該凹部及び/又は該貫通孔はその内部が略全域にわたって、前記フィルム6により充填されている形態をなす。

(もっと読む)

半導体装置

【課題】制御チップと複数の被制御チップが積層されたタイプの半導体装置において、コマンド信号よりも層アドレス信号を早く伝送させる。

【解決手段】互いに異なる層情報を保持する複数の被制御チップCC0〜CC7と、被制御チップCC0〜CC7に対して層アドレス信号A13〜A15及びコマンド信号ICMDを共通に供給する制御チップIFとを備える。層アドレス信号A13〜A15を構成する各ビットは、複数の第1の貫通電極のうち、被制御チップごとに並列接続された少なくとも2本の貫通電極を経由して伝送され、コマンド信号ICMDを構成する各ビットは、出力切り替え回路及び入力切り替え回路によって選択された対応する1本の貫通電極を経由して伝送される。これにより、コマンド信号ICMDよりも先に層アドレス信号A13〜A15が各被制御チップに到達する。

(もっと読む)

半導体装置及びその製造方法

【課題】多結晶シリコンプラグと上層の導体プラグとの界面に十分な膜厚の金属シリサイド層を形成してコンタクト抵抗の低減を図る。

【解決手段】多結晶シリコンプラグを形成した後、多結晶シリコンプラグの表面からゲルマニウムイオン注入を実施してゲルマニウム含有多結晶シリコン16Gとし、その後、シリサイド化可能な金属膜を成膜して金属シリサイド層19を形成し、金属シリサイド19上に導体膜(バリア膜20、W膜21)を形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】 表面側から特性試験が行える縦型の半導体装置を提供する。

【解決手段】 半導体装置10では、半導体基板11は第1の面と、第1の面に対向する第2の面を有している。半導体素子12は半導体基板11のダイシングライン14、15で囲まれた矩形状格子に形成されるとともに、第1の面に形成された第1電極26と、第2の面に形成された第2電極28とを有している。電流は第1電極26と第2電極28の間に流れる。貫通電極16は半導体基板11のダイシングライン14、15で囲まれていない領域に形成されるとともに、一端が第1の面上に延在し、他端が第2電極28と電気的に接続されている。

(もっと読む)

シリコン配線基板およびその製造方法

【課題】金属配線層間の絶縁を良好に維持することが可能で、シリコン基体上の絶縁層と金属配線層との密着性を向上したシリコン配線基板を提供する。

【解決方法】シリコン基体上に形成された二酸化ケイ素を主成分とする絶縁層と、前記絶縁層上に形成され、絶縁層のSiと酸素を介してシロキサン結合されたシラノール基もしくはアルコキシシラン基を有する有機単分子皮膜と、前記有機単分子皮膜に担持された触媒金属と、前記有機単分子皮膜に前記触媒金属を介して形成されたシード層と、前記シード層上に形成された金属からなる配線層とを具備したことを特徴とするシリコン配線基板。

(もっと読む)

半導体装置の製造方法

【課題】携帯電話などのフロントエンドモジュールに使用されているハイパワーアンプは、シリコン系CMOS集積回路をベースとするデバイスであるが、その出力段に多数のLDMOSFETセルを集積し、通常、複数のLDMOSFETを構成したLDMOSFET部を有する。このLDMOSFETセルにおいては、裏面のソース電極と表面のソース領域との間の抵抗を低減するために、半導体基板に高濃度にボロンドープされたポリシリコンプラグが埋め込まれている。このポリシリコンプラグは、熱処理に起因する固相エピタキシャル成長により収縮し、シリコン基板に歪が発生する。

【解決手段】本願発明は、LDMOSFET等の半導体装置の製造方法において、基板の表面からエピタキシャル層を貫通するホールを形成し、ポリシリコンプラグを埋め込むに際して、ホールの内面に薄膜酸化シリコン膜が存在する状態で、ポリシリコン部材の堆積を行うものである。

(もっと読む)

半導体記憶装置

【課題】動作速度の向上と面積の縮小を図る。

【解決手段】半導体記憶装置は、半導体基板100と、前記半導体基板上に形成され、データを記憶する複数のメモリセルが配置されたメモリセルアレイ部Aと、前記メモリセルアレイ部上に絶縁層を介して形成され、かつ、前記絶縁層および前記メモリセルアレイ部を貫通する孔106内に形成されて前記半導体基板に接続された単結晶半導体層109と、前記単結晶半導体層上に形成された回路部Bと、を具備し、前記メモリセルアレイ部上における前記単結晶半導体層の下部側は、上部側よりもGe濃度が高い。

(もっと読む)

異方性エッチング方法、三次元構造体、及び、デバイス

【課題】被対象物を効率よく所望する形状となるようにエッチングすることが可能な異方性エッチング方法、該異方性エッチング方法を用いて形成可能な三次元構造体、及び、該三次元構造体を備えたデバイスを得る。

【解決手段】異方性エッチング方法は、表面に所定形状のマスクを有した基板に対して、SF6とC4F8とを含む混合ガス、又は、SF6とC4F8とO2とを含む混合ガスを用いた反応性イオンエッチングによって、所定条件下で結晶異方性エッチングを行う結晶異方性エッチング工程を有している。本方法と、Bosch法による垂直異方性エッチングを行う垂直異方性エッチング工程とを用いて三次元構造体を製造し、該三次元構造体をデバイスに利用する。

(もっと読む)

半導体装置、スタックドパッケージ型半導体装置および半導体装置の製造方法

【課題】巣及びボイドのないビアを形成する。

【解決手段】半導体基板11を貫通するビアホール51と、ビアホール51の内壁面を被覆する無機絶縁膜13と、無機絶縁膜13の表面に脱水縮合により一端が結合され、他端にメルカプト基又は含硫黄芳香族複素環式基を有するカップリング剤から形成されたカップリング層15と、メルカプト基又は含硫黄芳香族複素環式基に結合された触媒金属16と、触媒金属16上に形成された無電解めっき金属からなるシード層17と、ビアホール51を埋め込みシード層17上に形成された電解めっき金属18からなるビア18aと、を有する半導体装置。

(もっと読む)

半導体装置

【課題】積層型の半導体装置においていずれかのバンクがアクティブ状態であるか否かを判定する。

【解決手段】バンクアドレス信号BA及びアクティブ信号ACT0を出力するインターフェースチップIFと、インターフェースチップIFに積層され、それぞれ対応するバンクアドレス信号BA及びアクティブ信号ACT0を受けて独立にアクティブ状態となる複数のメモリバンクを備えるコアチップCC0〜CC7とを備える。コアチップCC0〜CC7は、其々に含まれる複数のメモリバンクの少なくとも1つがアクティブ状態であるか否かを示すローカルバンクアクティブ信号MCIDTをインターフェースチップIFに其々出力し、インターフェースチップIFは、ローカルバンクアクティブ信号MCIDTの少なくとも1つが活性状態を示すときにバンクアクティブ信号PMCITを活性化させる。

(もっと読む)

集積回路装置およびその調製方法

【課題】 非常に複雑で費用がかかるバンプ・パッドを形成せずに、集積回路装置を製造する。

【解決手段】 集積回路装置100は、第1の環状誘電体ブロック21Aを有する底部ウェハー10Aと、底部ウェハー10A上に配置される、第2の環状誘電体21Bを有する少なくとも1つの積層ウェハー10Bと、実質的に直線状に底部ウェハー10A中へと積層ウェハー10Bを貫通する導電性ビア49とを備える。底部ウェハー10Aと積層ウェハー10Bはその間の接着層41により接合されている。底部ウェハー10Aと積層ウェハー10Bとの間にはバンプ・パッドは配置されない。導電性ビア49は、第1の環状誘電体ブロック21Aおよび第2の環状誘電体ブロック21Bの内部に位置している。

(もっと読む)

半導体装置

【課題】半導体基板を貫通する基板貫通孔に埋め込まれた基板貫通電極と該半導体基板との間の絶縁膜に対してその絶縁性を高めることの可能な半導体装置を提供する。

【解決手段】第1シリコン基板11と、前記第1シリコン基板11に形成された第1多層配線層12と、前記第1シリコン基板11を貫通して前記第1多層配線層12の内部に延びる基板貫通孔Hと、前記基板貫通孔H内に埋め込まれた基板貫通電極18と、前記基板貫通孔Hの内周面と前記基板貫通電極18の外周面とに挟まれた絶縁膜17とを備え、前記絶縁膜17が、金属元素の酸化ホウ化物膜であって、前記金属元素が、アルミニウム、チタン、バナジウム、ジルコニウム、ハフニウム、ベリリウム、及びマグネシウムのいずれか一つである。

(もっと読む)

埋め込みビットラインを備えた半導体装置の製造方法

【課題】埋め込みビットラインの抵抗を減少させることができる半導体装置の製造方法を提供すること。

【解決手段】本発明の半導体装置の製造方法は、基板201に活性領域203を分離するトレンチ202をエッチングにより形成するステップと、活性領域203の何れか1つの側壁の一部を露出させた開口部207を有する絶縁膜205を形成するステップと、絶縁膜205上にトレンチ202を部分的に埋め込み、開口部207を埋め込むようにシリコン膜パターン208Aを形成するステップと、シリコン膜パターン208A上に金属膜209を形成するステップと、金属膜209及びシリコン膜パターン208Aを反応させて、埋め込みビットラインとなる金属シリサイド膜211を形成するステップとを含む。

(もっと読む)

101 - 120 / 799

[ Back to top ]