Fターム[5F033TT07]の内容

半導体集積回路装置の内部配線 (234,551) | 絶縁膜の構造、形状 (4,088) | 側壁絶縁膜 (2,038) | コンタクトホールの側壁 (799)

Fターム[5F033TT07]に分類される特許

61 - 80 / 799

半導体チップおよびその製造方法

【課題】半導体チップ本体を貫通する電極を有する半導体チップにおいて、半導体チップ本体が厚い場合であっても、電極と半導体チップ本体との間に介在する絶縁部を容易に形成でき、且つ電極の信頼性を高くすることができるようにする。

【解決手段】半導体チップ1は、第1の面2aおよび第2の面2bと、4つの側面を有する半導体チップ本体2を備えている。半導体チップ1は、更に、半導体チップ本体2を貫通する電極収容部4と、少なくとも一部が電極収容部4内に収容された電極7と、電極収容部4内において、電極7と半導体チップ本体2との間に介在する絶縁部5とを備えている。絶縁部5に接する電極収容部4の壁面4Wは、第1の面2aに垂直な方向に対して傾いている。電極7と絶縁部5の界面が第1の面2aに垂直な方向に対してなす角度は、壁面4Wが第1の面2aに垂直な方向に対してなす角度よりも小さい。

(もっと読む)

半導体装置及びその製造方法

【課題】 半導体装置全体の応力緩和を実現すると共に、応力制御するための特別な構造が不要となり、装置の設計自由度も確保することができる半導体装置及びその製造方法を提供する。

【解決手段】 半導体装置1において、シリコン基板2とその上部に形成される金属配線層との絶縁を確保するために形成される絶縁部5を二層(第一絶縁部5a、第二絶縁部5b)に分離し、その一部に他の成膜工程で発生する残留応力と逆方向の残留応力を持たせることにより、半導体装置全体に作用する残留応力を低減する。

(もっと読む)

機能膜形成方法、配線基板の製造方法および配線基板

【課題】液体に対し金属膜の表面の濡れ性を改質し、金属表面と液体との接触角を増加させて液体の濡れ広がりを抑制し、信頼性の高い機能膜を低コストで実現すること。

【解決手段】基材1の平板面1aに金属膜2を形成する(金属膜形成工程)。次いで、金属膜2の表面2aに機能材料を含有する液体3を付与し、液体3を固化させて機能膜3Aを形成する(機能膜形成工程)。金属膜形成工程では、平板面1aに対する成膜入射角αが5°以上15°以下となる条件で平板面1aに金属を真空蒸着し、金属膜2を平板面1aに対して20°以上45°以下に傾斜する柱状結晶構造に形成する。

(もっと読む)

超音波スキャンに基づくシリコン貫通配線(TSV)におけるボイドの存在の推定

【課題】 3次元集積化構造中の不良を超音波スキャンによって検出することであって、シリコンウエハなどのボードに配列されているシリコン貫通配線(TSV)においてプロセス中に発生してしまう可能性のあるボイドの存在を非破壊的に検出すること。

【解決手段】 ボード面にわたって超音波スキャンをすると、(はんだ)バンプ等が物理的な遮蔽物として超音波を散乱させてしまい、超音波スキャンによる測定を妨げてしまう。そこで、これら複数のTSVの中から、テスト要素グループ(TEG)に属する単数または複数のTSVを選び出すにあたって、物理的な遮蔽物を少なく存在するように選び出す。

(もっと読む)

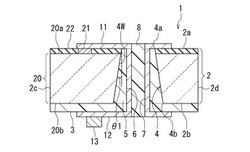

配線基板、赤外線センサー及び貫通電極形成方法

【課題】基板と貫通電極との間で形成される浮遊容量が小さい基板を提供する。

【解決手段】第1面2aと第1面2aと対向する第2面2bとを貫通して開口するビアホール2cを有する基板2と、基板2の第1面2aに設置され熱酸化膜を含む第1絶縁膜3と、ビアホール2c内の面とに設置され熱酸化膜を含む第3絶縁膜5と、ビアホール2c内で第3絶縁膜5に囲まれた導電体7と、を有し、第1面2aにおける第1絶縁膜3の厚みに比べてビアホール2c内の面における第3絶縁膜5の厚みが厚くなっている。

(もっと読む)

半導体基板の製造方法

【課題】サイドエッチ発生の可能性を軽減させた半導体基板の製造方法を提供する。

【解決手段】絶縁膜の形成後、シード膜の形成の前に配線パターンの形成を行う。次いで、シード膜の形成後、配線パターン用レジストの剥離を行う。次いで、メッキマスクレジストの形成を行なったのち、半導体基板の表面からのメッキ電流により、ウエットエッチング工法を行うこと無く、配線パターンの形成を行う。

(もっと読む)

多層接続構造及びその製造方法

【課題】3次元積層ICデバイスにおいて、相互接続領域のコンタクトレベルのスタックへの電気接続形成工程を簡略化する製造方法を提供する。

【解決手段】各コンタクトレベルは導電層と絶縁層とを有する。コンタクト開口を作り出すために、第1のコンタクトレベルを露出させるように上部層の一部が除去される。N個のマスクを用いて、最大2N個のコンタクトレベルまでコンタクト開口がエッチングされる。各マスクは、コンタクト開口のうちの実効的に半数をエッチングするために使用される。Nが3であるとき、第1のマスクにより1つのコンタクトレベルがエッチングされ、第2のマスクにより2つのコンタクトレベルがエッチングされ、第3のマスクにより4つのコンタクトレベルがエッチングされる。コンタクト開口の側壁に誘電体層が形成され得る。コンタクト開口内に導電体が形成され、前記誘電体層が該導電体を前記側壁から電気的に絶縁する。

(もっと読む)

電子デバイス、及び、その製造方法

【課題】素子に不具合が生じることが抑制された電子デバイス、及び、その製造方法を提供する。

【解決手段】接合された2つの基板(10,50)に素子(20,60)と貫通電極(30)とが形成されて成る電子デバイスであって、素子(20,60)は、2つの基板(10,50)の少なくとも一方に形成され、貫通電極(30)は、2つの基板(10,50)の少なくとも一方に形成されており、貫通電極(30)は、一方の基板(10)における他方の基板(50)との接合面(10a)側から、その裏面(10b)まで除去されて成るトレンチ(31)と、該トレンチ(31)を構成する壁面の一部に形成された導電膜(35)と、を有する。

(もっと読む)

半導体装置及びその製造方法

【課題】コンタクトホールの一部が素子分離領域上に配置された構造の半導体装置において、短絡及び接合漏れ電流の増大を抑制する。

【解決手段】半導体装置50は、半導体基板10における活性領域10aを取り囲むように形成された溝15bに素子分離絶縁膜15aが埋め込まれた素子分離領域15と、活性領域10aに形成された不純物領域26と、半導体基板10上を覆う層間絶縁膜28と、層間絶縁膜28を貫通し、活性領域10a上及び素子分離領域15上に跨って形成されたコンタクトプラグ34と、少なくともコンタクトプラグ34下方において、不純物領域26上に形成された金属シリサイド膜33とを備える。素子分離領域15は、コンタクトプラグ34の下方において、素子分離絶縁膜15と活性領域10aとの間に設けられた保護絶縁膜35を更に有する。

(もっと読む)

ボンディングパッドを有する半導体デバイス及びその製造方法

【課題】 ボンディングパッドを有する半導体デバイス及びその製造方法を提供する。

【解決手段】 表面側及び裏面側を有するデバイス基板、前記デバイス基板の前記表面側に配置され、n層数の金属層を有する相互接続構造、及び前記相互接続構造を通過して延伸し、前記n層数の金属層の前記第n番目の金属層に直接接触するボンディングパッドを含む半導体デバイス。半導体デバイスは、前記デバイス基板の前記裏面側に配置された遮蔽構造、及び、前記デバイス基板の前記表面側に配置され、前記デバイス基板の前記裏面側から前記放射線検出領域に向けて投射された放射線を検出することができる放射線検出領域をさらに備える。

(もっと読む)

半導体装置、及び、半導体装置の製造方法

【課題】 プローバーテストの製品への影響をさらに軽減して、より一層信頼性の高い半導体装置を提供する。

【解決手段】 半導体装置100を、半導体基板10aと、半導体基板10aの一方の面上に形成された絶縁膜10bと、縦孔配線部30と、金属膜11と、導電性保護膜12とを備える構成とする。金属膜11は、絶縁膜10b内に形成され、縦孔配線部30と電気的に接続される。そして、導電性保護膜12は、絶縁膜10b内において金属膜11に接して形成され、かつ、金属膜11の膜面において製造途中で行うプローバーテスト時のプローブの接触領域を含む領域に形成される。

(もっと読む)

半導体装置及びその製造方法並びに積層型半導体装置

【課題】貫通電極と直接に接続される配線の信頼性を向上できるようにする。

【解決手段】半導体装置100は、貫通孔1Aを有する半導体基板1と、半導体基板1の上に形成された第2層間絶縁膜7bと、第2層間絶縁膜7bに貫通孔1Aを覆うように形成された第1の外部接続用配線8a1と、第2層間絶縁膜7bの上に、第1の外部接続用配線8a1を覆うように形成された第3層間絶縁膜7cと、第3層間絶縁膜7cにおける第1の外部接続用配線8a1の上側部分に形成された第2の外部接続用配線8b1と、貫通孔1Aにおける少なくとも内壁面に形成されると共に、各外部接続用配線8a1、8b1とそれぞれ電気的に接続される貫通電極15Aとを備えている。第1の外部接続用配線8a1は、複数の孔部19aを有し、第2の外部接続用配線8b1は、第1の外部接続用配線8a1の孔部19aを覆うように形成されている。

(もっと読む)

導電性ビアの製造と充填のための方法、およびそのように形成された導電性ビア

【課題】ビアホール表面上の絶縁コーティングとビアホール内に挿入される導電材料との付着性を向上する。

【解決手段】導電性ビアを形成する方法は、一つ以上のビアホールを基板内に形成するステップを含む。ビアホールは、単一マスク、保護層、ボンドパッド、もしくは、エッチングプロセスの間にフォトマスクが除去される場合にハードマスクとして機能する、基板のその他のフィーチャで形成され得る。ビアホールは、その表面に低誘電率(低K)誘電材料を含む誘電体コーティングの付着を促進するように構成されてもよい。障壁層が各ビアホールの表面の上に形成されてもよい。種材料(seed material)を含み得るベース層は、その後のビアホールの表面上の導電材料の選択的堆積を促進するように形成されてもよい。

(もっと読む)

半導体装置、半導体装置の製造方法、回路基板および電子機器

【課題】電極パッドと貫通電極との接続面積を確保しつつ、下地膜が確実に形成される半導体装置、半導体装置の製造方法、回路基板および電子機器を提供する。

【解決手段】半導体基板10の能動面10a側に設けられた第一絶縁膜22と、第一絶縁膜22上に設けられた電極パッド12と、電極パッド12の形成位置に対応し、半導体基板10および第一絶縁膜22に形成された貫通孔H3と、貫通孔H3の少なくとも側面に設けられた第二絶縁膜23と、第二絶縁膜23と電極パッド12とを覆うように設けられた下地膜24と、下地膜24の内側で、貫通孔H3に埋め込まれた導電材料からなる貫通電極30と、を具備した半導体装置100において、貫通孔H3の側面と電極パッド12の裏面との角部23aに、第二絶縁膜23がフィレット状に形成されている。

(もっと読む)

半導体装置の製造方法

【課題】貫通電極の形成過程で、余分な酸化膜を確実に除去する。

【解決手段】貫通電極を形成するビアホール25の内面に酸化膜26を形成した後、Cu膜28を埋め込む。第1層間絶縁膜22の上に形成された余分なCu膜28をCMP法による研磨で除去するときに、酸化膜26も研磨されて膜厚が薄くなる。膜厚が薄くなった酸化膜26Bをハードマスクとして第1層間絶縁膜14に配線溝を形成する。このとき、酸化膜26Bの膜厚が薄くなる。配線溝に導電材を埋め込んだ後、余分な導電材を研磨によって除去する。このとき、残りの酸化膜26Bが全て研磨により除去される。

(もっと読む)

導電性構成部品、貫通ビア及び導電性貫通ウェーハ・ビアを含む半導体構成部品を製造するためのプロセス及び集積化スキーム

【課題】公知のプロセスよりも高速であり、充てんされたビアにボイド、凹み又はキーホールを残さず、製造の費用効果が高い、改善された方法を提供する。

【解決手段】第1の表面214及び対向する第2の表面216を有する基板212を設け、基板の第1の表面に部分的にのみ前記基板の中に広がる少なくとも1つのブラインドビア218を形成する。酸化材料によって前記少なくとも1つのブラインドビアの表面をパッシベーションし、少なくとも一つのブラインドビアの酸化材料の表面に銅を含むシード材料228を、シード材料を前記少なくとも一つのブラインドビアの内部に閉じ込め、かつ、基板の前記第1の表面を露出させるように形成する。シード材料の上に導電性材料230を前記少なくとも一つのブラインドビアを充填するように無電解めっきし、少なくとも一つのブラインドビアの導電性材料を露出させるために基板の前記第2の表面に研磨平坦化を実施する。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体基板の一表面上に絶縁膜を介して形成された導電層と、半導体基板の他面上に形成されたバンプ部と、導電層とバンプ部とを接続する半導体基板を貫通する貫通電極部とを有する半導体装置を提供する。

【解決手段】半導体基板の他面側から導電層に接続する貫通孔を形成し、貫通孔及び他面上にメタル膜(バリアメタル及びシードメタル)6を形成し、その上にフォトレジスト10を形成し、貫通孔より大きなパターンに加工してメッキマスク層を形成し、電解メッキ法により銅からなる第1メッキ膜7を形成して、貫通電極部と第1バンプ部を形成し、第1バンプ部上に第2バンプ部となる第2メッキ膜8を形成する。

(もっと読む)

複数の開口部を備える基板上への層の蒸着方法

【課題】多孔性低誘電率絶縁膜のトレンチおよびビア内にカバレージ良くライニング層を形成する半導体装置の製造方法を提供する。

【解決手段】第1パルス期間に供給される第1反応物と、第2パルス期間に供給される第2反応物とを利用する原子層堆積(ALD)プロセスにより成膜する。まずシーリング層を低コンフォマリティーを有する条件で成膜し、ポアをブロックする。この後、接着層を高いコンフォマリティーを有する条件で成膜する。

(もっと読む)

半導体装置、半導体装置の製造方法、固体撮像装置及び電子機器

【課題】 ビア形成時のエッチングによる基板や配線への影響を抑制しつつ積層された半導体ウェハの回路どうしを接続する。

【解決手段】 半導体装置の製造方法は、第1基板と第1基板の一面と接するように形成された第1絶縁層を有する第1の半導体ウェハと、第2基板と第2基板の一面と接するように形成された第2絶縁層を有する第2の半導体ウェハを接合する工程と、第1基板の他面に第3絶縁層を形成する工程と、第3絶縁層、第1基板、及び第1絶縁層を貫通し第2絶縁層に形成された第2の配線上に第2絶縁層が残るようにエッチングを行い第1接続孔を形成する工程と、第1接続孔に絶縁膜を形成する工程と、第2の配線上の第2絶縁層及び絶縁膜のエッチングを行い第2接続孔を形成し第2の配線を露出させる工程と、第1及び第2接続孔の内部に形成され第2の配線と接続する第1のビアを形成する工程とを備え、第1基板の他面に形成された第1接続孔の径は第3絶縁層に形成された前記第1接続孔の径より大きい。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】信頼性に優れた半導体装置を提供する。

【解決手段】半導体装置の製造方法は、主面に複数の埋込導電部(埋込導電部106)が設けられたシリコンウエハ102と、シリコンウエハ102の主面に配置された、埋込導電部106に電気的に接続する複数の第1の半導体素子(半導体チップ108)と、を備える構造体を用意する工程と、半導体封止用樹脂組成物を用いて、シリコンウエハ102の主面上の複数の半導体チップ108を封止する封止材層110を形成する工程と、シリコンウエハ102の裏面を研削して、裏面に埋込導電部106を露出させて、貫通プラグ105とする工程と、を含む。

(もっと読む)

61 - 80 / 799

[ Back to top ]