Fターム[5F033VV06]の内容

半導体集積回路装置の内部配線 (234,551) | 配線の用途 (10,506) | ゲート電極配線 (2,049)

Fターム[5F033VV06]に分類される特許

41 - 60 / 2,049

半導体装置

【課題】微細化が可能な半導体装置を提供する。

【解決手段】実施形態に係る半導体装置は、上面に、一方向に延び上方に突出した複数本のアクティブエリアが形成された半導体基板と、前記アクティブエリア間のトレンチの下部に埋め込まれた素子分離絶縁体と、第1の絶縁材料からなり、前記素子分離絶縁体の直上域に配置され、下部が前記トレンチ内に配置され、上部が前記アクティブエリアの上端よりも上方に突出した絶縁ブロックと、前記第1の絶縁材料とは異なる第2の絶縁材料からなり、前記半導体基板及び前記絶縁ブロックの上方に設けられた層間絶縁膜と、前記層間絶縁膜内に形成され、下端が前記アクティブエリアの上面に接続されたコンタクトと、を備える。前記コンタクトにおける前記絶縁ブロックの直上域に位置する部分の下面は、前記コンタクトにおける前記アクティブエリアの直上域に位置する部分の下面よりも上方に位置している。

(もっと読む)

液晶表示装置の製造方法及びレジスト剥離装置

【課題】2層構造の走査線を、絶縁膜を介して映像信号線が乗り越える際の、映像信号線の断線を防止する。

【解決手段】エッチングによってAl合金層11、キャップ層12で形成される走査線10をパターニングした後、レジスト200をMEA(モノエタノールアミン)によって剥離する。MEAを剥離したあと、第1水洗槽において、基板に付着しているMEAを水によって洗浄する。この時、洗浄液である水に所定の量以上のMEAが含まれていると、Al合金が溶解し、キャップ層12であるMoCrの庇が発生する。これを防止するために、第1水洗槽における洗浄液のMEAの濃度を10PPM以下、好ましくは5PPM以下に管理する。これによって、Al合金の溶解を防止し、キャップ層12の庇が発生することを防止する。

(もっと読む)

3Dフラッシュ構造用のエッチングプロセス

【課題】プラズマ処理室において、ウェハ上でスタックを形成するシリコン系の複数の二重層の中に高アスペクト比のフィーチャをエッチングするための方法を提供する。

【解決手段】プラズマ処理室に主エッチングガスが流入される。第1の圧力を提供しながら、主エッチングガスがプラズマにされる。20℃未満のウェハ温度が維持される。プラズマにより上記複数のシリコン系二重層のうちの複数の組を貫いてエッチングする間に、第1の圧力よりも低い第2の圧力まで圧力を降下させる。上記複数の二重層のうち第1の複数の組がエッチングされた後に、主エッチングガスの流入を停止させる。

(もっと読む)

半導体装置及びその製造方法

【課題】柱状半導体層の幅を広く維持することができる半導体装置を提供すること。

【解決手段】半導体装置は、一つの直線上に順に形成された、第1、第2及び第3の柱状半導体層と、第2及び第3の柱状半導体層の間の空間であって第2及び第3の柱状半導体層の側面に夫々設けられた第1及び第2のゲート電極と、第1及び第2の柱状半導体層の間の空間及び第2及び第3の柱状半導体層の空間に埋め込まれた層間絶縁膜とを有する。層間絶縁膜は、第1及び第2の柱状半導体層の間の空間内であってゲート電極を介することなく第1及び第2の柱状半導体層の側面に形成され、第2及び第3の柱状半導体層の間の空間内であって第1及び第2のゲート電極を介して第2及び第3の柱状半導体層の側面に形成されている。

(もっと読む)

半導体装置及びそれを用いたSiPデバイス

【課題】高耐圧の能動素子を含む回路と低電圧で動作するロジック回路とが同一基板上に混載された半導体装置を低コストで実現する。

【解決手段】半導体装置が、ロジック回路50と、能動素子回路とを具備している。ロジック回路50は、半導体基板1に形成された半導体素子2を備えている。該能動素子回路は、半導体基板1の上方に形成された拡散絶縁膜7−1の上に形成された半導体層8−1、8−2を用いて形成されたトランジスタ21−1、21−2を備えている。この能動素子回路がロジック回路50により制御される。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】半導体装置の反りを抑制し、且つ、その反りの経時変化を抑制する。

【解決手段】半導体装置は、基板と、基板上に形成された多層配線層と、を有し、多層配線層は、配線と、配線を覆う層間絶縁膜と、をそれぞれ有する複数層の配線層を有する。少なくとも何れか1つの層間絶縁膜(例えば、層間絶縁膜27、30)は、第1絶縁膜41と第2絶縁膜42とを有する。第1絶縁膜41は、基板を第1方向(例えば下に凸)に反らせる応力を基板に与える。第2絶縁膜42は、第1絶縁膜41よりも表層側に形成され、第1絶縁膜41よりも吸湿性が低く、基板を第1方向に対する反対方向(例えば上に凸)に反らせる応力を基板に与える。

(もっと読む)

半導体装置及びその製造方法

【課題】プロセス条件の見直しを最小限に抑制しつつ電気的特性を向上させることができる半導体装置及びその製造方法を提供する。

【解決手段】半導体装置1は、半導体構造11の上面領域に形成された島状の絶縁膜20と、絶縁膜20の上面領域に配列された複数の凸状絶縁部23と、これら凸状絶縁部23と絶縁膜20とを被覆する層間絶縁膜26とを備える。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】メモリセル積層構造間に空隙を有する不揮発性半導体記憶装置において、隣接するメモリセル積層構造間、及び、メモリセル積層構造−選択ゲート積層構造間のショートを防ぐことができる不揮発性半導体記憶装置およびその製造方法を提供する。

【解決手段】実施形態に係る不揮発性半導体記憶装置は、シリコン基板上にゲート絶縁膜、浮遊ゲート電極、電極間絶縁膜および制御ゲート電極が順に積層されたメモリセル積層構造が複数隣接して配置され、隣接する前記メモリセル積層構造間に空隙を有する不揮発性半導体記憶装置であって、前記メモリセル積層構造間のシリコン基板上に、前記メモリセル積層構造の側壁に形成されたシリコン酸化膜より厚いシリコン酸化膜が形成されている。

(もっと読む)

半導体装置

【課題】残渣による配線間のショートの発生を防ぐ。

【解決手段】本発明の半導体装置は、高誘電率材料を含む第1のゲート絶縁膜4と第1のゲート絶縁膜4上に形成された第1のメタルゲート電極5とを備える第1のトランジスタが形成される半導体基板上の第1の領域と、高誘電率材料を含む第2のゲート絶縁膜4と第2のゲート絶縁膜上に形成された第2のメタルゲート電極12とを備え、第1のトランジスタとは閾値電圧の異なる第2のトランジスタが形成される半導体基板上の第1の領域に並ぶ第2の領域と、電位の異なる第1および第2の配線と、を有し、第1の領域と第2の領域との境界が、第1および第2の配線の少なくとも一方としか重ならない。

(もっと読む)

不揮発性半導体記憶装置

【課題】隣接する配線の間におけるリークを抑制することができる不揮発性半導体記憶装置を提供する。

【解決手段】不揮発性半導体記憶装置1は、シリコンを含む基板11と、基板11の上に設けられた複数のメモリセルと、複数のメモリセルの上方に設けられた配線7と、配線7の上に設けられたリーク抑制層8と、前記リーク抑制層8の上方に設けられた層間絶縁膜10と、を備えている。そして、隣接するメモリセルの間、および、隣接する配線7の間には空隙12が形成され、リーク抑制層8の幅寸法は、配線7の幅寸法よりも短いこと、および、隣接するリーク抑制層8の間の寸法は、隣接する配線7の間の寸法よりも長いこと、の少なくともいずれかである。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】ワード線抵抗を低減し、かつ、周辺回路のトランジスタの特性変化を抑制することができる半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、半導体基板と、複数のメモリセルと、周辺回路とを備える。メモリセルは、半導体基板の上方に設けられたフローティングゲートと、フローティングゲート上に設けられたゲート間絶縁膜と、ゲート間絶縁膜上に設けられたコントロールゲートとを含む。周辺回路は、互いに電気的に接続されたフローティングゲートおよびコントロールゲートと、少なくともフローティングゲートとコントロールゲートとの間の電気的接触部分に設けられ該フローティングゲートと該コントロールゲートとの間の電気的接続を妨げない絶縁薄膜とを含むトランジスタを含む。複数のメモリセルは、コントロールゲート内に絶縁薄膜を含まない。メモリセルおよび周辺回路において、コントロールゲートの少なくとも上部はシリサイド化されている。

(もっと読む)

炭化珪素半導体装置の製造方法

【課題】配線を形成したときに電極と配線との密着性を向上できる炭化珪素半導体装置の製造方法を提供する。

【解決手段】第1の面と、第1の面と反対の第2の面とを有する炭化珪素半導体層110が準備される。炭化珪素半導体層110の第2の面を部分的に覆う金属層と、炭化珪素半導体層110の第2の面を部分的に覆う熱酸化膜130とが形成される。金属層を熱処理することにより電極150が形成される。金属層を形成する工程は、金属層を熱処理する温度において炭素よりもシリコンとの反応性が高い材料を用いて行われる。電極150を形成する工程において電極150の表面上に炭素が偏析する。電極150の表面および熱酸化膜130の表面の両方において、炭素を除去可能なエッチングが行われる。

(もっと読む)

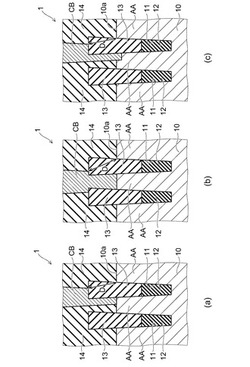

多層配線基板、アクティブマトリクス基板及びこれを用いた画像表示装置、並びに多層配線基板の製造方法

【課題】上部配線層と下部配線層とを、微細なコンタクトホールを介して接続する多層配線基板、アクティブマトリクス基板及びこれを用いた画像表示装置、並びに多層配線基板の製造方法を提供する。

【解決手段】基板10上に形成された第1の導電層20と、層間絶縁層30と、第2の導電層70とを有し、前記層間絶縁層に形成されたコンタクトホール40を介して前記第1の導電層と前記第2の導電層とが電気的に接続された構造を有する多層配線基板において、

前記層間絶縁層は、前記コンタクトホールを含まない第1の領域50と、前記コンタクトホールを含み、該第1の領域よりも表面エネルギーが高く形成された第2の領域60とを有し、

前記第1の導電層の前記コンタクトホール内の領域は、前記第2の領域よりも表面エネルギーが高く、

前記第2の導電層は、前記層間絶縁層の前記第2の領域に接触して堆積形成され、前記コンタクトホールを介して前記第1の導電層と接続されている。

(もっと読む)

半導体装置およびその製造方法

【課題】論理素子のnチャネルMOSトランジスタに十分な膜厚の引張応力膜を形成し、メモリ素子がゲート電極間の層間絶縁膜の埋込不良を生じない製造方法の提供。

【解決手段】論理素子は、第1及び第2のnチャネルMOSトランジスタを含み、第1のゲート高さGH1及び第1のゲート長を有するゲート電極を有し、ゲート電極は第1の間隔Dを有し、メモリ素子は、第3および第4のnチャネルMOSトランジスタを含み、ゲート高さGH2および第2のゲート長を有するゲート電極を含み、論理素子及びメモリ素子は第1の引張応力膜64で覆われ、論理素子は、さらに第2の引張応力膜65で覆われ、論理素子及びメモリ素子のゲート間に形成された引張応力膜の最小距離は各々第1の距離LL及び第1の距離LMで隔てられ、第1のアスペクト比(GH1/LL)と、第2のアスペクト比(GH2/LM)とは略等しい。

(もっと読む)

半導体装置の製造方法

【課題】局所配線を有する半導体装置に関し、位置ずれに起因する電気特性や歩留まりの低下を抑制しうる半導体装置の製造方法を提供する。

【解決手段】半導体基板上に、隣接して配された第1の配線及び第2の配線を形成し、第1の配線の側壁に第1の側壁絶縁膜を、第2の配線の側壁に第2の側壁絶縁膜を形成し、第1及び第2の配線、第1及び第2の側壁絶縁膜が形成された半導体基板上に導電膜を形成し、第1及び第2の配線上の導電膜を選択的に除去し、第1の配線と第2の配線との間の領域に、導電膜により形成され、第1及び第2の側壁絶縁膜によって第1及び第2の配線から隔てられた第3の配線を形成する。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】メモリセルアレイと周辺回路との間のアレイ端パターンにおける耐圧を向上させる。

【解決手段】浮遊ゲートは半導体基板上の第1の絶縁膜上に設けられる。ゲート間絶縁膜は浮遊ゲート上に、制御ゲートはゲート間絶縁膜上に設けられる。メモリセルは、第1の絶縁膜、浮遊ゲート、ゲート間絶縁膜および制御ゲートを含む。周辺回路はメモリセルアレイの周辺に設けられる。第1のダミーセルは、第1の絶縁膜、浮遊ゲート、ゲート間絶縁膜および制御ゲートを含み、メモリセルアレイの端に設けられる。第2のダミーセルは、第1の絶縁膜よりも厚い第2の絶縁膜を含み、第1のダミーセルと周辺回路との間に設けられる。第1のダミーセルにおいて、ゲート間絶縁膜および制御ゲートは浮遊ゲートの上面および2つの側面に設けられる。

(もっと読む)

半導体装置

【課題】酸化物半導体層を用いた表示装置に代表される半導体装置において、画面サイズの大型化や高精細化に対応し、表示品質が良く、安定して動作する信頼性のよい半導体装置を提供する。

【解決手段】引き回し距離の長い配線にCuを含む導電層を用いることで、配線抵抗の増大を抑える。また、Cuを含む導電層を、TFTのチャネル領域が形成される酸化物半導体層と重ならないようにし、窒化珪素を含む絶縁層で包むことで、Cuの拡散を防ぐことができ、信頼性の良い半導体装置を作製することができる。特に、半導体装置の一態様である表示装置を大型化または高精細化しても、表示品質が良く、安定して動作させること

ができる。

(もっと読む)

半導体装置及びその製造方法

【課題】電極端部への電界集中を抑えるとともに、ゲート電極の変形や、ゲート−フィールドプレート間に生じる容量による特性劣化を抑える。

【解決手段】半導体装置において、第1の基板と、第1の基板表面に形成された素子領域と、素子領域と接続され、第1の基板上に形成されたゲート電極、ソース電極及びドレイン電極と、第1の基板と、第1の面で積層される第2の基板と、第2の基板を貫通し、電極上に配置されるビアホールと、ビアホール内に形成され、電極と接続される金属層と、第2の基板に設けられ、ゲート電極、ソース電極及びドレイン電極のいずれかと接続されるフィールドプレート電極と、を備える。

(もっと読む)

半導体装置及びその製造方法

【課題】通電領域表面の周辺の強電界の影響がナノワイヤに及び難くして、ホットキャリアの生成やオフリーク電流を低減する。半導体装置を高性能化する。

【解決手段】基板の表面よりも深い位置に配置され互いに対向する2つの側壁を有する導電膜と、導電膜の2つの側壁の側方に形成され互いに同じ導電型の半導体領域である第1及び第2の通電領域と、導電膜を貫通して2つの半導体領域どうしを接続し第1及び第2の通電領域の導電型とは逆導電型の半導体領域であるナノワイヤと、導電膜と前記ナノワイヤとの境界部に形成された絶縁膜と、を有することを特徴とする半導体装置。

(もっと読む)

半導体装置およびその製造方法

【課題】本発明は、製造コストを低減し、さらにゲート電極およびゲートコンタクトの抵抗を低減した半導体装置およびその製造方法を提供することを目的とする。

【解決手段】本発明にかかる半導体装置は、ゲート電極7の少なくとも上層は、第2金属シリサイド膜としてのWSix膜72からなり、第1金属シリサイド膜としてのNiSi2膜18に含まれる第1金属(Ni)とシリコンとの結合エネルギーが、WSix膜72に含まれる第2金属(W)とのシリコンとの結合エネルギーよりも小さく、WSix膜72の組成MSix(Mは第2金属を示す)において、xが1.5以上2.0未満であることを特徴とする。

(もっと読む)

41 - 60 / 2,049

[ Back to top ]