Fターム[5F033VV10]の内容

半導体集積回路装置の内部配線 (234,551) | 配線の用途 (10,506) | 受動素子 (1,084) | 容量 (664)

Fターム[5F033VV10]に分類される特許

81 - 100 / 664

半導体装置及びその製造方法

【課題】トランジスタの微細化が進展しても、広いキャパシタ面積を確保し、容量を増大させることが可能なキャパシタを備える、半導体装置およびその製造方法を提供する。

【解決手段】半導体装置は、基板111と、基板上に、第1の電極材で形成された複数の第1の電極層と、第1の電極材と異なる第2の電極材で形成された複数の第2の電極層とが、キャパシタ絶縁膜を介して交互に積層されたキャパシタ102と、第1及び第2の電極層の側方に形成されており、第1の電極層と電気的に接続され、第2の電極層と電気的に絶縁されている、1つ以上の第1のコンタクトプラグ171Aと、第1及び第2の電極層の側方に形成されており、第2の電極層と電気的に接続され、第1の電極層と電気的に絶縁されている、1つ以上の第2のコンタクトプラグ171Bとを備える。

(もっと読む)

半導体素子及びその製造装置

【課題】汎用性が高く、低コストで省資源である方法を採用し、実用性に富み、任意の場所、任意の形状に金属又は半導体を二次元的又は三次元的に形成できる半導体素子及びその製造装置を提供する。

【解決手段】炭素材料と金属酸化物材料又は半導体酸化物材料とを有する還元反応構造1Aを持つ層構造30Aを準備し、還元反応構造1Aに対して局所的にエネルギーを集中することが可能で、かつ還元反応構造1Aに対して2次元的又は3次元的に走査することが可能な熱源を用い、この熱源によって酸化還元反応が起こる温度以上に還元反応構造1Aの一部を走査しつつ選択的に加熱して、炭素材料により金属酸化物材料又は半導体酸化物材料をそれぞれ金属又は半導体に還元し、所望の形状の金属領域又は半導体領域(金属層又は半導体層3A)を形成することによって製造されることを特徴とする半導体素子40Aとすることにより上記課題を解決する。

(もっと読む)

半導体装置

【課題】高周波デバイスを形成する複数の素子を一つのチップに形成できる技術を提供する。

【解決手段】基板1上にて抵抗素子および容量素子の下部電極を同一の多結晶シリコン膜から形成し、前記多結晶シリコン膜とは異なる同一の多結晶シリコン膜およびWSi膜からパワーMISFETのゲート電極、容量素子の上部電極、nチャネル型MISFETのゲート電極およびpチャネル型MISFETのゲート電極を形成し、領域MIMにおいては基板1上に堆積された酸化シリコン膜30上に形成された配線を下部電極とし酸化シリコン膜34上に形成された配線を上部電極とする容量素子MIMCを形成し、酸化シリコン膜34上に堆積された酸化シリコン膜37上に堆積された同一のアルミニウム合金膜を用い領域INDにて配線39Aからなるスパイラルコイルを形成し、領域PADでは配線39Bからなるボンディングパッドを形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】新たな工程を追加することなく信頼性の高い半導体装置およびその製造方法を提供すること。

【解決手段】半導体素子を表面側に有する基板11と、半導体素子を覆うように基板11に積層された第1絶縁膜12と、第1絶縁膜12を厚さ方向に貫通する貫通孔の内面に積層されたバリア導電層13を介して貫通孔内に埋め込まれたコンタクトプラグ14と、第1絶縁膜12の表面に形成されてコンタクトプラグ14を介して半導体素子と電気的に接続された1種類以上の機能層とを備え、前記機能層は、バリア導電層13の材料と同じ材料からなり第1絶縁膜12の表面の所定領域に積層された第1バリア導電層13と、第1バリア導電層13上に、直接積層されるか、または第2絶縁膜15を介して積層されるか、またはそれらの両方の形態で積層された第2バリア導電層16と、第2バリア導電層16に積層された導電層17とを有してなることを特徴とする半導体装置。

(もっと読む)

アナログディジタル変換器

【課題】アナログディジタル変換器が半導体基板上で占める面積の低減する。また、アナログディジタル変換器の高精度化を図る。

【解決手段】半導体基板200上には、Pチャネルトランジスタ104aを有するアナログスイッチが形成されている。アナログスイッチの上層には、アナログスイッチに重なる領域に、櫛形電極401・402・501・502が形成され、キャパシタが構成されている。

(もっと読む)

半導体装置、下層配線設計装置、下層配線設計方法およびコンピュータプログラム

【課題】MIMキャパシタの構造破壊に起因するリーク電流の上昇を低減する構成を備えた半導体装置を提供することを課題とする。

【解決手段】複数の下層配線11を備える下層配線層10と、下層配線層10の上方に設けられる、下部電極21と容量誘電膜22と平面形状が下部電極21より小さい上部電極23とを下からこの順に積層したMIMキャパシタ20と、MIMキャパシタ20の上方に設けられ、ビア40、41を介して下部電極21および上部電極23のそれぞれに接続する複数の上層配線31を備える上層配線層30と、を備えた半導体装置であって、上部電極23の平面形状は矩形に構成され、上部電極23の平面のいずれか一以上の辺であるエッジ部の直下には下層配線11が配置されていない半導体装置を提供する。

(もっと読む)

半導体装置およびその製造方法

【課題】平坦な表面を有する層間絶縁膜を短時間で形成することができ、また、層間絶縁膜の厚さの増大を招くことなく、金属イオンによる半導体基板の汚染に対する長期信頼性を保証することができる、半導体装置およびその製造方法を提供する。

【解決手段】半導体装置1は、半導体基板2と、半導体基板2上に形成された層間絶縁膜8とを備えている。そして、層間絶縁膜8は、半導体基板2側から順に、HDP膜10、ゲッタリング層12およびNSG膜11が積層された構造を有している。ゲッタリング層12は、金属イオン、とくに可動イオンを捕獲する性質を有している。

(もっと読む)

薄膜トランジスタ装置およびその製造方法

【課題】

使用現場で使用者や顧客の要望に応じて、回路システムを形成することのできる薄膜トランジスタ装置およびその製造方法を提供する。

【解決手段】

薄膜トランジスタ装置において、TFTにより構成した複数の集積回路ブロック1,2と、これらの集積回路ブロックを相互に接続するための網目状に交差したマトリックス配線3、4、5、6を設ける。相互の集積回路ブロック間の接続は、使用現場で使用者や顧客の要望に応じて導電性材料を印刷等により、マトリックス配線の各々の配線交差部に選択的に設けることにより行い、所望の回路システムを構成する。

(もっと読む)

半導体装置及びその製造方法

【課題】高信頼性でかつ高レイアウト密度配線と混載可能な容量素子を備えた半導体装置及びその製造方法を提供する。

【解決手段】本発明は、容量素子を有する半導体装置であって、アルミニウム合金膜102と、高融点金属膜を含む上層バリア膜103とを含む金属配線200aおよび下部電極200bと、下部電極200b上に形成された容量絶縁膜104と、容量絶縁膜104上に形成された上部電極105とを有する。高融点金属膜の膜厚は、40nm以上、80nm以下であり、容量絶縁膜104は、有機シランを原料としたシリコン酸化膜からなることを特徴とする。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】強誘電体キャパシタの下部電極とバリアメタル膜との間の酸化膜の形成を防止する半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、トランジスタTのソース/ドレイン拡散層11に接続するように形成された第1、第2のビアコンタクト23、24と、バリアメタル膜31を介して第1、第2のビアコンタクト23、24に接続された強誘電体キャパシタCとを備える。強誘電体キャパシタCは、バリアメタル膜31上に設けられた下部電極32と、強誘電体膜33と、上部電極34とを備える。下部電極32は、錐台形状の上部322と、この上部322に比べ水平方向に突出した鍔部を有する底部321とからなり、下部電極32の底部321は、バリアメタル膜31の上面を全て覆い、バリアメタル膜31の端面、鍔部の端面、及び強誘電体膜33の端面が水平方向において整合している。

(もっと読む)

デュアル・ダマーシン相互接続構造および金属電極コンデンサを有する集積回路デバイスとその製造方法

【課題】本発明は、コンデンサを有する集積回路デバイスに関する。

【解決手段】集積回路デバイスおよびその製造方法は、相互接続構造およびコンデンサを含む。相互接続構造は、金属線および接点を含み、コンデンサは上部および下部金属電極を含む。この方法は、半導体基板に隣接する誘電体層を形成することと、第一誘電体層において相互接続構造の第一開口部およびコンデンサの第二開口部を同時に形成することとを含む。この方法は、相互接続構造を形成するために、第一導電層を選択的にデポジットさせて、第一開口部を充填することと、第二開口部にコンデンサを形成するために、その間にコンデンサ誘電体を有する上部および下部金属電極を形成することとを含む。集積回路デバイスは、金属電極を有し、デュアル・ダマシーン構造にも使用でき、統合される高密度コンデンサを提供する。この様に、コンデンサは、デュアル・ダマシーン相互接続構造と同一レベルに位置される。

(もっと読む)

半導体装置及びその製造方法

【課題】 信号線の形成位置に関わらず、信号線とMIM構造のキャパシタ11との間で発生する寄生容量が抑制できるようにする。

【解決手段】 MIM構造のキャパシタ11と、絶縁膜12a,12bを介してMIM構造のキャパシタ11を挟む、少なくとも一対の遮蔽部13a,13bとを備える。

(もっと読む)

半導体装置及びその製造方法

【課題】 下部電極とビア配線とのコンタクト抵抗の増大を抑制可能な、容量素子を有する半導体装置及びその製造方法を提供する。

【解決手段】 半導体装置は、半導体基板101上に形成され下部電極110と誘電体膜120と上部電極130とを有する容量素子を含む。容量素子の下部電極110は、例えばTi膜である金属膜111と、金属膜111上に形成されたTiN膜113とを有する。半導体装置は更に、容量素子を覆う絶縁膜142と、絶縁膜142を貫通して下部電極110のTiN膜113と接触するビア配線150とを含む。TiN膜113は好ましくは30nm未満の厚さを有する。Ti膜111の表面の少なくとも一部には、ビア配線150とTi膜111との間に介在するよう、Ti膜111の窒化処理による窒化層112が形成されている。

(もっと読む)

半導体装置

【課題】容量素子を構成する第1電極及び第2電極を形成するためのリソグラフィ工程で重ね合わせズレが生じた場合にも容量ばらつきを抑制できる半導体装置を提供する。

【解決手段】複数の配線層L1〜L5のそれぞれは、絶縁膜103〜106と、当該絶縁膜中に相互に離隔し且つ向かい合うように埋め込まれた第1電極101及び第2電極102とを有する。一の配線層の第1電極101と、その上方又は下方に設けられた他の配線層の第2電極102とは相互に向かい合うように配置されている。一の配線層の第1電極101の幅と、他の配線層の第2電極102の幅とは異なっている。

(もっと読む)

半導体装置及びその製造方法

【課題】導電プラグの酸化を抑止し、コンタクト抵抗の安定化された信頼性の高い半導体装置を実現する。

【解決手段】下部電極101と上部電極103とで強誘電体膜102を挟持してなる強誘電体キャパシタ構造100と、導電プラグ110との間に、酸化しても導電性を有する導電材料(例えば金属)からなる導電層112を形成し、ここでは、導電プラグ110の下地膜を導電層112(Ag,Ni,Cu,Zn,In,Sn,Ir,Ru,Rh,Pd,Osから選ばれた少なくとも1種を材料として形成される。)とする。

(もっと読む)

表示装置

【課題】オフ電流の低減とともにオフリーク電流の低減が図れ、製造工数の増大をもたらすことなく回路の集積化が図れる薄膜トランジスタを備えた表示装置の提供。

【解決手段】表示部が形成された基板上に複数の薄膜トランジスタが形成されている表示装置であって、

前記薄膜トランジスタは、

ゲート電極と、

前記ゲート電極を跨って形成されたゲート絶縁膜と、

このゲート絶縁膜の上面に形成され、平面的に観て前記ゲート電極の形成領域内に開口が形成された層間絶縁膜と、

前記層間絶縁膜の表面に前記開口を間にして配置された一対の高濃度半導体膜と、

前記層間絶縁膜の前記開口を跨いで形成され、平面的に観て、前記ゲート電極の形成領域内に形成されるとともに前記一対の高濃度半導体膜に電気的に接続された多結晶半導体層と、

前記一対の高濃度半導体膜のそれぞれに重ねられ前記多結晶半導体膜に重ねられることなく形成された一対の電極と、

を備えたものを含む。

(もっと読む)

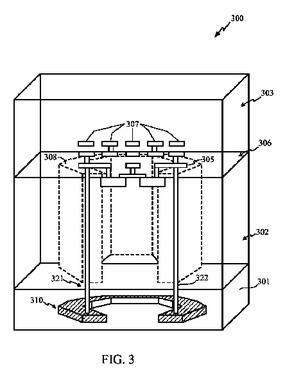

能動および受動デバイスをチップ内に配置する方法

半導体ダイ(300)は、第1および第2の面をもつ半導体基板層(302)と、半導体基板層の第2の面に隣接する金属層と、半導体基板層の第1の面上の活性層(306)内の1つまたは複数の能動デバイス(305)と、活性層と電気的に接続される金属層内の受動デバイス(310)とを含む。受動デバイスは、シリコン貫通ビア(TSV)(321、322)によって、活性層に電気的に結合することができる。  (もっと読む)

(もっと読む)

表示装置及びその作製方法

【課題】酸化物半導体を用いた薄膜トランジスタを具備する画素を作製する際に、生産性の向上を図る。

【解決手段】基板上に形成されたゲート電極として機能する第1の配線と、前記第1の配線上に形成されたゲート絶縁膜と、前記ゲート絶縁膜上に、低抵抗酸化物半導体層及び前記低抵抗酸化物半導体層上に導電層が積層して設けられた第2の配線、並びに前記低抵抗酸化物半導体層及び前記低抵抗酸化物半導体層の画素電極として機能する領域が露出するように前記導電層が積層して設けられた電極層と、前記ゲート絶縁膜上の前記第2の配線と前記電極層との間に形成された高抵抗酸化物半導体層と、を有する。

(もっと読む)

半導体装置およびその製造方法

【課題】本発明は、裏面コンタクト電極と拡散層とのコンタクト抵抗が低減して、半導体装置の動作速度の向上を図ることを可能にする。

【解決手段】基板10の表面側に形成された拡散層25P、26P、25N、26Nと、前記拡散層25P、26P、25N、26Nの表面に形成されていて前記拡散層25P、26P、25N、26Nよりも抵抗が低い低抵抗部27P、28P、27N、28Nと、前記基板10の裏面側より前記基板10を貫通して前記拡散層25P、26P、25N、26Nを通して前記低抵抗部27P、28P、27N、28Nに接続された裏面コンタクト電極63P、64P、63N、64Nを有する。

(もっと読む)

半導体装置

【課題】大量生産上、大型の基板に適している半導体装置を提供する。

【解決手段】ゲート電極と、チャネルを含む島状半導体層と、島状半導体層上に形成されたドレイン配線およびソース配線とを有し、島状の半導体層は、In−Ga−Zn−Oを含み、ドレイン配線及びソース配線は島状半導体層をキャリアの移動方向と垂直に横断し、チャネルの長さはドレイン配線およびソース配線の間隔に等しいことを特徴としている。

(もっと読む)

81 - 100 / 664

[ Back to top ]