Fターム[5F033VV10]の内容

半導体集積回路装置の内部配線 (234,551) | 配線の用途 (10,506) | 受動素子 (1,084) | 容量 (664)

Fターム[5F033VV10]に分類される特許

101 - 120 / 664

半導体装置及びその製造方法

【課題】柱状構造体の形成の際のリソグラフィの合わせずれの許容度を拡大し、デバイス特性の劣化を抑制する半導体装置及びその製造方法を提供する。

【解決手段】第1層と、前記第1層の主面の上に設けられた第2層と、前記主面を貫通し、前記第1層と前記第2層とに延在する導電性の柱状構造体と、前記主面の前記第2層の側において前記柱状構造体の側壁に付設された側部と、を備えたことを特徴とする半導体装置を提供する。

(もっと読む)

発光装置の作製方法

【課題】平坦性の向上により、TFTの移動度を向上させ、TFTのオフ電流を低減する

。

【解決手段】基板上に非晶質構造の半導体膜を形成する工程と、前記半導体膜上に結晶化

を促進する金属元素を添加する工程と、加熱処理を行って、前記半導体膜を結晶構造の半

導体膜とする工程と、前記結晶構造の半導体膜に第1のレーザー光を照射する工程と、前

記結晶構造の半導体膜に第2のレーザー光を照射する工程とを有する。レーザー光を照射

する工程を2回設けることにより、結晶構造の半導体膜の平坦化を向上させることができ

る。その結果、TFTの移動度を向上させ、TFTのオフ電流を低減させることができる

。

(もっと読む)

半導体装置の製造方法

【課題】キャパシタ誘電体膜の劣化を防止しながら、金属配線間を絶縁膜で所望に埋め込むことができる半導体装置の製造方法を提供すること。

【解決手段】シリコン基板(半導体基板)1の上方に下地絶縁膜9を形成する工程と、キャパシタQ1、Q2を下地絶縁膜9の上に形成する工程と、キャパシタQ1、Q2を覆う第1層間絶縁膜68を形成する工程と、第1、第2配線溝30、33と、該配線溝30、33の底部から下に延びる第1、第2コンタクトホール31、34とを第1層間絶縁膜68に形成する工程と、第1、第2配線溝30、33と第1、第2コンタクトホール31、34とに第1拡散防止膜35と第1銅膜36(第1導電体)とを埋め込む工程と、水素を含まない還元性ガス中において第1銅膜36をアニールする工程とを有することを特徴とする半導体装置の製造方法による。

(もっと読む)

半導体装置の製造方法

【課題】段差上に被覆された被エッチング膜を大幅にオーバーエッチングすることなく、エッチング残渣を除去することができるとともに、下地酸化膜を薄膜化することができる半導体装置の製造方法を提供する。

【解決手段】配線パターンが形成された半導体基板上に酸化膜を被覆する工程と、酸化膜上に導電材料の被エッチング膜を被覆する工程と、炭素を含まず硫黄を含む化合物を添加して、被エッチング膜を酸化膜に対して選択性を持たせつつプラズマエッチングしてパターニングする工程とを含む。

(もっと読む)

半導体装置

【課題】外部からの電気的な干渉が十分に低減されるとともに、所望の特性を発揮する容量素子が形成される半導体装置、を提供する。

【解決手段】半導体装置は、主表面1aを含む半導体基板1と、主表面1a上に規定された容量形成領域22に形成され、所定の方向に延在する複数の配線11と、容量形成領域22の周縁に配置された配線11pに隣り合い、所定の方向に延在し、電位固定された複数の配線12と、主表面1a上に形成され、複数の配線11の各々の間と、隣り合う配線11および配線12の間とを充填する絶縁体層5とを備える。複数の配線11および12は、主表面1aに平行な平面21内においてほぼ等しい間隔を隔てて配置され、かつ所定の方向に対してほぼ直角方向に並んで配置されている。

(もっと読む)

フォトセンサ及び表示装置

【課題】マトリクス状に配置した光電変換素子が捉える光の強度分布を、再現よく電気信号に変換して取り出せる大型のエリアセンサおよび、エリアセンサを搭載した書き込み速度が速く、表示ムラが少ない表示装置を提供する。

【解決手段】インジウム、ガリウム、および亜鉛を含む酸化物半導体を用いた薄膜トランジスタは、大面積基板にマトリクス状に配置することが容易であり、また特性にバラツキが少ない。インジウム、ガリウム、および亜鉛を含む酸化物半導体を用いた薄膜トランジスタで構成した特性にバラツキが少ない増幅回路と表示素子の駆動回路を用いて、マトリクス状に配置したフォトダイオードが捉える光の強度分布を再現よく電気信号に変換して取り出し、マトリクス状に配置した表示素子をムラなく駆動する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】酸素ガスを主に含有したガスでエッチングを行う必要がある金属材料を用いてピラー型電極を形成する際に、ピラー型電極のアスペクト比が高くなると製造が困難になるという課題があった。

【解決手段】層間絶縁膜上に第1〜第6の絶縁膜を積層した後、第1のフォトレジスト膜を形成する工程と、前記第1のフォトレジスト膜をマスクとして第1の溝部を形成する工程と、前記第1の溝部を充填するように電極材料を堆積する工程と、前記第4の絶縁膜上に第7〜第9の絶縁膜を形成した後、第2のフォトレジスト膜を形成する工程と、前記第2のフォトレジスト膜をマスクとして第2の溝部を形成すると共に、前記電極材料をピラー型に残存させる工程と、前記第8、前記第7、前記第4および前記第2の絶縁膜を除去して、前記電極材料からなるピラー型電極を露出する工程と、を有する半導体装置101の製造方法を用いることにより、上記課題を解決できる。

(もっと読む)

半導体装置およびその製造方法、固体撮像素子、電子情報機器

【課題】半導体基板から1層目メタル配線までの高さを低く抑えることにより、コンタクト形成時にアスペクト比を小さくできて、コンタクト形成時の不良による導通不良を抑制する。

【解決手段】同一半導体基板1に、MIS構造のトランジスタ15と、下部電極5と上部電極8間にキャパシタ絶縁膜7を介在させたキャパシタ16とが設けられている。コンタクト形成不良を防止するために、キャパシタ16の形成前にキャパシタ形成領域3の素子分離膜2を予めエッチングにより掘り下げ、このキャパシタ16は、この掘り下げられた素子分離膜2上に設けられている。

(もっと読む)

半導体装置、半導体装置の製造方法およびスイッチ回路

【課題】トランジスタのリーク電流の低減。

【解決手段】半導体材料の表面に沿って互いに隣接する複数の電気素子要素と、複数の電気素子要素を覆う、シリコンを含まない下層保護絶縁膜と、下層保護絶縁膜の上に配置され、シリコンを含む上層保護絶縁膜と、を備える半導体装置が提供される。上記半導体装置において、複数の電気素子要素の少なくとも一つは、シリサイド化される金属を含有でき、下層保護絶縁膜は、電気素子要素に含有される金属と上層保護絶縁膜に含有されるシリコンとの接触を阻害できる。下層保護絶縁膜は、比誘電率が10以上の高誘電体層を有してよい。上層保護絶縁膜は、シリコンおよび窒素を含有することができる。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】配線層に新たな機能を有する素子を設けた半導体装置を提供する。

【解決手段】半導体基板上に形成された第1配線層150、及び半導体素子200を備える。第1配線層150は、絶縁層156と、絶縁層156の表面に埋め込まれた第1配線154とを備える。半導体素子200は、半導体層220、ゲート絶縁膜160、及びゲート電極210を備える。半導体層220は、第1配線層150上に位置する。ゲート絶縁膜160は、半導体層220の上又は下に位置する。ゲート電極210は、ゲート絶縁膜160を介して半導体層220の反対側に位置する。

(もっと読む)

キャパシタ構造体

【課題】面積を増加せずとも、キャパシタの静電容量を増大させることのできるキャパシタ構造体を提供すること。

【解決手段】本発明のキャパシタ構造体は、複数個の開口部を有する第1の電極と、前記開口部の各々の中央に形成される第2の電極と、前記開口部を埋め込んで第2の電極を囲むように形成される誘電膜とを備えることを特徴とする。

(もっと読む)

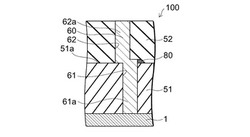

半導体装置

【課題】ノイズの影響を低減できるともに、レイアウト効率のよいMIM型容量素子を提供する。

【解決手段】半導体装置100は、下部電極112と、下部電極112上に設けられた中間電極116と、中間電極116上に設けられた上部電極124と、下部電極112と中間電極116との間に設けられた第1の絶縁膜と、中間電極116と上部電極124との間に設けられた第2の絶縁膜と、中間電極116と同層に設けられている第1の接続配線118と、下部電極112と第1の接続配線118とを電気的に接続する第1のビア114と、第1の接続配線118と上部電極124とを電気的に接続する第2のビア122とを有し、第1の接続配線118、第1のビア114、および、第2のビア122が、中間電極116の第1の辺に隣接して設けられているとともに、中間電極116の第1の辺と対向する第2の辺に隣接して設けられている。

(もっと読む)

半導体装置およびその製造方法

【課題】MIM構造のキャパシタを含む半導体装置において、安定した容量値を与える。

【解決手段】半導体装置100は、基板(不図示)上に形成された絶縁膜154、同層に形成されるとともに、絶縁膜154を介して対向配置された第1の電極および第2の電極、を有するMIMキャパシタ200とを含む。第1の電極および第2の電極は、それぞれ、基板の積層方向において、他の領域300に形成されたビア130および当該ビア上に当該ビアに接続して設けられた配線132が形成された層にわたって延在する第1の高アスペクトビア110および第2の高アスペクトビア120により構成される。

(もっと読む)

薄膜多層配線基板およびその製造方法

【課題】 剥離の発生の少ない薄膜多層配線基板とその製造方法を提案する。

【解決手段】 少なくとも一つの前記配線層が、下層の配線層上に形成された第一のSiO2薄膜と、前記第一のSiO2薄膜上に形成されたSiON薄膜と、前記SiON薄膜上に形成された第二のSiO2薄膜と、前記第二のSiO2薄膜に埋め込まれて形成された配線導体と、前記配線導体と接続しかつ前記第一のSiO2薄膜、前記SiON薄膜および前記第二のSiO2薄膜を貫通して前記下層の配線層の配線導体と電気的に接続するビア導体と、前記第二のSiO2薄膜上に形成されたSiN薄膜と、で構成されている。

(もっと読む)

半導体装置

【課題】チャネル長を、トランジスタごとに自由に設計が可能な半導体装置を提供する。

【解決手段】複数の半導体柱2が立設された半導体基板1と、半導体柱2の外周面に設けられたゲート絶縁膜7と、半導体柱2の外周面を覆うゲート電極8と、半導体柱2の上側に設けられた第1不純物拡散領域3と、半導体柱2の下側に設けられた第2不純物拡散領域4と、を備え、第1不純物拡散領域3の厚さが半導体柱2ごとに異なっていることを特徴とする半導体装置。

(もっと読む)

半導体装置の配線構造物及びその形成方法

【課題】後工程における、キャパシタの下部電極と接続されるべき第2コンタクトプラグの形成の際の洗浄液による第1コンタクトパッドの損傷を防止できる、半導体装置の配線構造物及びその形成方法を提供する。

【解決手段】配線構造物は、第1コンタクトパッド126、第1コンタクトプラグ150、スペーサー140、及び層間絶縁膜パターン120、130を含む。第1コンタクトパッド126は、基板100の第1コンタクト領域116aと電気的に接続される。第1コンタクトプラグ150は、第1コンタクトパッド126上に具備され、第1コンタクトパッド126と電気的に接続される。スペーサー140は、第1コンタクトプラグ150の側壁と第1コンタクトパッド126の側壁の上部とに同時に面接する。層間絶縁膜パターン120,130は、コンタクトパッド126とスペーサー140を収容する開口を有する。

(もっと読む)

電子デバイスの製造方法及び設定装置

【課題】電子デバイスの更なる微細化及び高集積化が進んでも、リソグラフィー及びエッチングにより被加工対象の極めて高い寸法精度を達成し、信頼性の高い電子デバイスを実現する。

【解決手段】被加工対象上に形成されたレジスト膜を加工してレジストパターンを形成する工程と、レジストパターンをマスクとして、所定のエッチング条件で被加工対象をエッチングする工程とを実行する際に、形成されたレジストパターンの寸法及び形状(膜厚及びテーパ角度)を測定し、測定されたレジストパターンの寸法及び形状に基づいて前記エッチング条件を調整する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】製造安定性に優れ、接触抵抗の低減を図ることができる半導体装置およびこの半導体装置の製造方法を提供する。

【解決手段】半導体装置1は、上層配線12と、下層配線11と、上層配線12および下層配線11間に配置された絶縁層22〜24と、絶縁層22〜24中に形成されて上層配線12および下層配線11を接続する接続部13と、絶縁層24中に配置されて、接続部13に接続される導電層を有する素子14とを有する。接続部13は、下層配線11上および素子14の前記導電層の端部上にわたって配置され、接続部13は、下層配線11上面、素子14の導電層の端部の上面および側面に接触している。

(もっと読む)

半導体装置

【課題】同一種のチップ間で、容量値にばらつきの少ない容量を形成できる技術を提供する。

【解決手段】配線M1A、M2A、M3A、M4Aを容量電極の一方とし、配線M1B、M2B、M3B、M4Bを容量電極の他方とし、層間絶縁膜9、13、16、19を容量絶縁膜とするフリンジ容量において、配線M1A、M1B、M2A、M2B、M3A、M3B、M4A、M4Bの配置ピッチLPは、これらの配線のうちの最も配線幅の大きい配線M4A、M4Bの配置ピッチに合わせる。配線M1A、M1B、M2A、M2B、M3A、M3Bの隣接配線間距離L1は、配線M1A、M1B、M2A、M2B、M3A、M3Bの配線幅LWより大きく、かつ最小加工寸法の1.3倍〜3倍程度、好ましくは2倍〜3倍程度とする。

(もっと読む)

透明薄膜トランジスタ及び画像表示装置

【課題】配線抵抗を低下させて、均一かつ確実に動作させる透明薄膜トランジスタ及び画像表示装置を提供すること。

【解決手段】実質的に透明な基板と、基板上に実質的に透明な導電材料の第1の薄膜と金属材料の第2の薄膜とを2層以上積層して形成されたゲート配線と、ゲート配線上に形成された実質的に透明なゲート絶縁膜と、ゲート絶縁膜上に形成された実質的に透明な半導体活性層と、実質的に透明な半導体活性層を挟んで離間して形成された実質的に透明な導電材料の第5の薄膜と金属材料の第6の薄膜とを2層以上積層して形成されたソース配線と、実質的に透明な半導体活性層を挟み、ソース配線に離間して実質的に透明な導電材料の第7の薄膜で形成されたドレイン電極と、を備えることを特徴とする透明薄膜トランジスタ。

(もっと読む)

101 - 120 / 664

[ Back to top ]