Fターム[5F033VV12]の内容

半導体集積回路装置の内部配線 (234,551) | 配線の用途 (10,506) | 検査、試験 (365)

Fターム[5F033VV12]に分類される特許

21 - 40 / 365

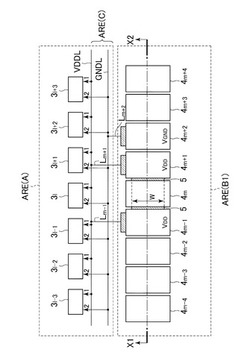

半導体チップ、半導体ウェハおよび半導体チップの検査方法

【課題】配線抵抗に起因した電圧降下を抑制し、検査工程での誤判定を受けにくい半導体チップおよび半導体ウェハを提供する。更に、配線抵抗に起因した電圧降下を抑制し、検査工程で誤判定を受けにくい半導体チップの検査方法を提供する。

【解決手段】電極パッド領域は、絶縁膜(7)上で一列に配列されたn個(n≧3)の電極パッド(4m−4から4m+4)を備える。内部セル領域は、電極パッド領域側に配列されている半導体回路(3l−3から3l+3)にそれぞれ接続された配線(VDDL)をn個の電極パッドの配列方向に備える。n個の電極パッドの内、第1の電極パッド(4m−1)と、第1の電極パッドから1個の電極パッドを隔てた第2の電極パッド(4m+1)とが、絶縁膜中で互いに接続され、かつ、配線Lm−1およびLm+1によって、配線(VDDL)にそれぞれ接続されている。

(もっと読む)

半導体装置、及び、半導体装置の製造方法

【課題】 プローバーテストの製品への影響をさらに軽減して、より一層信頼性の高い半導体装置を提供する。

【解決手段】 半導体装置100を、半導体基板10aと、半導体基板10aの一方の面上に形成された絶縁膜10bと、縦孔配線部30と、金属膜11と、導電性保護膜12とを備える構成とする。金属膜11は、絶縁膜10b内に形成され、縦孔配線部30と電気的に接続される。そして、導電性保護膜12は、絶縁膜10b内において金属膜11に接して形成され、かつ、金属膜11の膜面において製造途中で行うプローバーテスト時のプローブの接触領域を含む領域に形成される。

(もっと読む)

半導体チップのクラックのチェックテスト構造を有する半導体装置

【課題】半導体チップ積層後に、チップごとにクラックの有無検出可能な半導体装置の提供。

【解決手段】積層半導体装置において、半導体チップ21〜24は、基板10とこの表裏面の対向する位置に形成した対のテスト端子と配線61を備える。これらは、一対の(表側)第1のテスト端子621h、(裏側)第1のテスト端子621t及び複数対の(表側)第2のテスト端子622〜625h、(裏側)第2のテスト端子622〜625tで、貫通電極TSVT1が(表側)第1のテスト端子と(裏側)第1のテスト端子を接続し、貫通電極TSVT2〜5が対の(表側)第2のテスト端子と(裏側)第2のテスト端子同士を接続し、配線は、一端が第1のテスト端子と、他端が第2のテスト端子の一つに接続され、基板の外周に沿って延びる。また異なる半導体チップの上下に隣接する第2のテスト端子同士も接続する。

(もっと読む)

電子部品、電子部品の製造方法、基板

【課題】チッピング検出用配線が他の部材で覆われている状態であっても、ダイシングによって電子部品を形成した後に、チッピング検出用配線の導通状態を検出するための電圧を印加できる基板を提供する。

【解決手段】電子部品40は、互いに平行を成す一方の主面41aと他方の主面41bが矩形状の基体41を有する。基体41の一方の主面41aには、第一チッピング検出用配線42が配されている。また、基体41の他方の主面41bには、第二チッピング検出用配線44が配されている。第一チッピング検出用配線42は貫通配線43aを介して第二チッピング検出用配線44に電気的に接続される。

(もっと読む)

半導体装置

【課題】LSIチップの製造コストを低減することが可能な半導体装置を提供する。

【解決手段】半導体装置は、半導体基板と、前記半導体基板に形成され、第1の電源配線を含む第1の電源配線層を備える複数のLSI領域と、前記半導体基板に形成された第1の電源端子と、前記LSI領域の間のダイシングライン領域に、前記LSI領域と前記ダイシングライン領域とを区画するダイシングラインに沿って形成され、前記第1の電源配線と前記第1の電源端子とを電気的に接続する第2の電源配線を含む第2の電源配線層と、を備える。少なくとも前記LSI領域において、前記第1の電源配線と前記第2の電源配線との境界にバリアメタル膜が形成されている。

(もっと読む)

半導体装置の製造方法、半導体装置の製造装置および半導体装置

【課題】配線溝へのめっきの埋め込み性を安定させることができる半導体装置の製造方法等を提供すること。

【解決手段】実施形態によれば、半導体装置の製造方法が提供される。半導体装置の製造方法は、めっき処理によって金属膜を埋め込んで検査パターン10を形成する形成工程と、検査パターン10の特性を検出する検出工程と、検出工程によって検出された検査パターン10の特性に基づいて、前記めっき処理の条件を調整する調整工程とを含む。前記形成工程は、3層以上の配線層11〜13に亘って形成され、かつ中間層にスタックドビア22を有するパターンを、前記検査パターン10として形成する。

(もっと読む)

半導体装置及びその試験方法

【課題】論理値の反転処理を行う回路をコアチップ側に設けることなく、TSVを含む電流パスラインのショート不良を検出する。

【解決手段】半導体装置10は、第1及び第2の電流パスSa,Sbと、これらとそれぞれ電気的に接続する第1及び第2のラッチ回路100a,100bと、第1のラッチ回路100aに第1のデータD1を供給するとともに、第2のラッチ回路100bに第1のデータとは逆の論理値を有する第2のデータD2を供給するドライバ回路101と、第1のデータD1が第1のラッチ回路100aに供給され、かつ第2のデータD2が第2のラッチ回路100bに供給されない第1の期間と、第2のデータD2が第2のラッチ回路100bに供給され、かつ第1のデータD1が第1のラッチ回路100aに供給されない第2の期間と、が交互に繰り返されるよう、ドライバ回路101を制御する制御回路104と、モニタ回路120とを備える。

(もっと読む)

金属層の結晶粒径及び粒径分布評価方法並びにそれを用いた半導体集積回路装置の製造方法

【課題】非破壊かつオンラインで金属層の結晶粒径及び粒径分布を評価する方法を実現する。

【解決手段】結晶組織を有し特定の面方位においてX線に対して回折ピークを持つ金属層にX線を照射して得られる回折ピークを入手するステップA、回折ピークに基づいて面積平均コラム長及び体積平均コラム長を求めるステップB、面積平均コラム長及び体積平均コラム長から結晶粒径の対数正規分布を求めるステップCを具備する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】一つのTEGで複数方向の位置ずれを検出できるようにする。

【解決手段】この半導体装置は、TEG300を有している。TEG300は、プラグ及び配線のいずれか一方である第1要素と、プラグ及び配線の他方である第2要素を有している。第2要素は、互いに異なる方向から第1要素に面しており、第1要素から離間している。本実施形態において、第1要素はプラグ320であり、第2要素は配線330である。プラグ320は、コンタクトであってもよいし、ビアであってもよい。またプラグ320は、配線330の上に位置していてもよいし、下に位置していてもよい。

(もっと読む)

半導体装置、及び積層型半導体装置

【課題】本発明は、積み重ねられた半導体装置間の電気的接続信頼性を向上可能な半導体装置及び積層型半導体装置を提供することを課題とする。

【解決手段】表面58a及び裏面58bを有する半導体チップ38を貫通する第1の貫通電極48と、半導体チップ38の表面側に位置する第1の貫通電極48の一端に接続される第1の表面電極53と、半導体チップ38の裏面側に位置する第1の貫通電極48の一端に接続される第1の裏面電極55と、半導体チップ38を貫通する第2の貫通電極49と、半導体チップ38の裏面側に位置する第2の貫通電極49の一端に接続される第2の裏面電極56と、を備え、半導体チップ38の表面側に位置する第2の貫通電極49の一端には電極を設けない。

(もっと読む)

半導体装置

【課題】兼用パッドのサイズを専用パッドよりも大きくするとともに、半導体装置のサイズ増大を抑制する。

【解決手段】半導体装置は、第1の方向に延伸された第1のエッジE1と、第1の方向と実質的に直交する第2の方向に延伸された第2のエッジE2とを含む半導体チップ10と、半導体チップ上に形成され、互いに第2の方向に沿った長さが実質的に等しい複数の第1グループパッドGP1と、半導体チップ上に形成され、第2の方向に沿った長さが、複数の第1グループパッドの第2の方向に沿った長さよりも長い、第2グループパッドGP2と、を備える。複数の第1グループパッドと第2グループパッドとは、第2グループパッドと第2のエッジとの間に複数の第1グループパッドのいずれをも含まずに、第1の方向に沿って一列に並んで配置されている。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】電極パッド部の安定した電気的接触を確保しつつ電極パッド部の面積を小さくすることができる半導体装置および半導体装置の製造方法を提供する。

【解決手段】半導体装置は、半導体基板と、半導体基板の主表面上であって平面視において素子形成領域内およびダイシングライン領域内の少なくともいずれかに形成された半導体チップ用電極パッド部,TEG用電極パッド部PTとを備えている。半導体チップ用電極パッド部,TEG用電極パッド部PTは、外部と電気的に接続するための表面OSFを有し、かつ半導体チップ用電極パッド部,TEG用電極パッド部PTの辺SIDに対して斜めに傾斜した方向に延びた溝部THPを表面OSFに有している。

(もっと読む)

半導体装置およびその製造方法

【課題】 表面側から特性試験が行える縦型の半導体装置を提供する。

【解決手段】 半導体装置10では、半導体基板11は第1の面と、第1の面に対向する第2の面を有している。半導体素子12は半導体基板11のダイシングライン14、15で囲まれた矩形状格子に形成されるとともに、第1の面に形成された第1電極26と、第2の面に形成された第2電極28とを有している。電流は第1電極26と第2電極28の間に流れる。貫通電極16は半導体基板11のダイシングライン14、15で囲まれていない領域に形成されるとともに、一端が第1の面上に延在し、他端が第2電極28と電気的に接続されている。

(もっと読む)

半導体装置の製造方法

【課題】ヒューズ(FUSE)を備えた半導体装置の信頼性を向上する。

【解決手段】半導体基板11の主面上に形成にされた多層配線を構成する層M1〜M6のうちの層M4に設けられた電気溶断型の救済用のヒューズ4aおよび試験用のヒューズ4bと、ヒューズ4aの近傍であって層M2および層M6に設けられた一対の導電板10aと、ヒューズ4bの近傍であって層M3および層M5に設けられた一対の導電板10bとから構成する。ヒューズ4bと導電板10bとの間が、ヒューズ4aと導電板10aとの間より近いものとする。

(もっと読む)

配線構造、半導体装置及び不良箇所特定方法

【課題】不良箇所の特定の容易化を実現し得る配線構造、半導体装置及び不良箇所特定方法を提供することにある。

【解決手段】基板10上に形成された第1の配線14と、第1の配線上に形成され、第1の領域において第1の配線と重なり合う第2の配線20とを有し、第1の配線は、第1の領域外に突出する第1のタブ部16を有している。

(もっと読む)

半導体装置、半導体装置の検査方法、及び、半導体装置の製造方法

【課題】半導体装置の製造工程の増大を抑制しつつ、パッドの針跡を容易に確認できるようにする。

【解決手段】半導体装置は、半導体基板1と、半導体基板1上に形成された回路素子と、半導体基板1上に形成され、回路素子と電気的に接続されたパッド(接続パッド4)と、を有している。パッドは、平面視において、導体が存在する実体パターン41と、前記導体が存在しない開口パターン42と、を含む所定のパターン形状に形成されている。

(もっと読む)

半導体装置、および半導体装置の検査方法

【課題】高抵抗回路の面積の狭小化を図り、集積率の高い半導体装置への高抵抗回路の形成を容易とする。

【解決手段】配線層2に形成された下層配線20および下層配線22と、配線層2上に形成された層間絶縁膜12と、層間絶縁膜12に形成され、下層配線20と接続するビア30と、層間絶縁膜12に形成され、下層配線22と接続するビア32と、層間絶縁膜12上に形成され、ビア30とビア32とを接続する上層配線24と、を備え、ビア30およびビア32の抵抗値は、上層配線24の抵抗値よりも大きい。

(もっと読む)

半導体集積回路

【課題】例えばクラック発生などに起因する大量生産段階での低歩留りという問題を防止できる半導体集積回路を提供する。

【解決手段】パッドメタルの下に回路を有する半導体集積回路において、パッド開口部分のパッドメタルの少なくとも下全面に、互いに同一の電位を有する配線メタルを形成し、当該配線メタルの電位を上記パッドメタルと異なる電位に設定した。また、上記配線メタル、及び上記配線メタル以外の電位を有する別の配線メタルは、上記パッドメタルよりも下層に形成される。さらに、上記半導体集積回路の複数のパッドにおいて、バッド開口部分のパッドメタルの少なくとも下全面に形成された複数の配線メタルは互いに同一の電位に設定される。

(もっと読む)

半導体装置、半導体装置の製造方法、及び半導体装置の検査方法

【課題】層間絶縁膜に生じたボイドを高感度に検出する。

【解決手段】この半導体装置は、多層配線層(非図示、以下略)と、多層配線層中に形成された第一TEGパターン(非図示)を備える。第一TEGパターンは、互いに平行に延伸した複数の第一下層配線402と、層間絶縁膜(非図示)を貫通し、平面視で第一下層配線402間に位置する第一ビア602と、多層配線層の最上層(非図示)に形成され、第一ビア602に接続している第一端子762と、上記した同一の最上層に形成され、第一下層配線402に接続している第二端子764と、を備える。

(もっと読む)

半導体装置

【課題】異なる電位に対応する複数の外部電源配線間に間隔部分を有する半導体装置に対して,所定電源ピン数のテスタにより短絡試験を行う場合において,より多くの半導体装置の短絡試験を同時に行うことができる半導体装置を提供する。

【解決手段】半導体装置は,コア回路と,該コア回路の周囲に配置され且つコア回路と外部装置間の信号を入出力する複数の入出力回路と,複数の入出力回路のうちの第一の入出力回路グループに第一の電位の電源を供給する第一の電源配線と,複数の入出力回路のうちの第二の入出力回路グループに第二の電位の電源を供給し且つ第一の電源配線と間隔をあけて直列に延びる第二の電源配線と,第三の電位の電源を供給する第三の電源配線とを備え,第三の電源配線から延びる配線パターンが,第一の電源配線と第二の電源配線間の間隔部分に設けられる。

(もっと読む)

21 - 40 / 365

[ Back to top ]