Fターム[5F033XX28]の内容

半導体集積回路装置の内部配線 (234,551) | 目的、効果 (15,696) | 拡散、突き抜け防止 (992)

Fターム[5F033XX28]の下位に属するFターム

シリコンの拡散、突き抜け防止 (20)

アルミニウムの拡散、突き抜け防止 (24)

Fターム[5F033XX28]に分類される特許

81 - 100 / 948

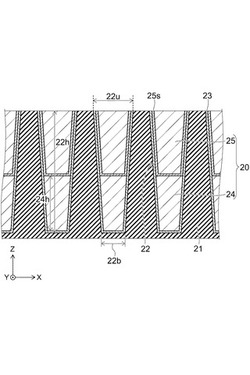

不揮発性記憶装置およびその製造方法

【課題】より低抵抗な配線層を有する不揮発性記憶装置を提供する。

【解決手段】実施形態の不揮発性記憶装置は、書き替え可能な複数の不揮発性メモリセルと、前記複数のメモリセルのそれぞれに電気的に接続可能な配線層と、を備えた不揮発性半導体記憶装置である。前記配線層は、絶縁層に設けられたトレンチ内に設けられ、前記配線層は、第1導電層と、前記第1導電層の上に設けられた第2導電層と、を有し、前記配線層が充填されていない前記トレンチに対する前記第1導電層の埋め込み性は、前記配線層が充填されていない前記トレンチに対する前記第2導電層の埋め込み性よりも高く、前記第2導電層の比抵抗は、前記第1導電層の比抵抗よりも低い。

(もっと読む)

半導体集積回路装置の製造方法

【課題】プラズマCVD法を用いてCu配線上に良好な拡散バリア膜を形成する技術を提供する。

【解決手段】ダマシン法を用いて形成したCu配線19上にCuの拡散を防止する窒化シリコン膜21を形成する工程は、Cu配線19が形成された基板1をプラズマCVD装置のチャンバ内に搬入し、基板1を所定の温度に加熱する工程と、チャンバ内にアンモニアを供給し、第1のRFパワーでアンモニアをプラズマ分解することによって、Cu配線19の表面を還元処理する工程と、RFパワーが印加された状態で、チャンバ内にアンモニアとモノシランとを含む原料ガスを供給し、第2のRFパワーでアンモニアとシラン系ガスとをプラズマ分解することによって、Cu配線19上に窒化シリコン膜21を形成する工程とを含んでいる。

(もっと読む)

半導体装置およびその製造方法

【課題】コンタクト孔に埋め込まれる金属プラグの材料が層間絶縁膜に染み出すのを防止できる半導体装置を提供する。

【解決手段】隣り合う2つのメモリセル1のサイドウォール間の不純物拡散領域に電気的接続されるコンタクトプラグ40が、層間絶縁膜18を貫通して設けられている。コンタクト孔41の側壁は、層間絶縁膜18より緻密なシール膜42で覆われている。コンタクトプラグ40は、シール膜42の表面およびコンタクト孔41の底面部を覆うように形成されたバリアメタル膜43と、バリアメタル膜43に包囲された状態でコンタクト孔41内に埋め込まれた金属プラグ44とを含む。

(もっと読む)

電子デバイス配線用Cu合金スパッタリングターゲット材、及び素子構造

【課題】酸化物反応層の寄生抵抗の低減を図り、動作特性の向上を図った電子デバイス配線用Cu合金スパッタリングターゲット材、及び素子構造を提供する。

【解決手段】TFT素子1は、a−Si膜5上に形成されたPドープn+a−Si膜6と、Pドープn+a−Si膜6上に形成された1nm以下のSi酸化膜7を有している。電極配線膜となるCu合金膜8が、Si酸化膜7上にスパッタリングにより形成されている。Cu合金膜8は、0.3〜2.0原子%のSn、In、Gaの金属のうち1種以上を含有する。

(もっと読む)

成膜付半導体素子、及びその製造方法

【課題】半導体素子を破壊することを防止しつつ半導体素子の金属膜に対し安価に成膜できるとともに容易に厚膜化できる成膜付半導体素子の製造方法を提供すること。

【解決手段】シリコン層11に重ねてアルミ膜12を有する半導体素子10に対しコールドスプレー装置30によって成膜する成膜付半導体素子の製造方法は、第1工程と、第2工程とを有する。第1工程では、コールドスプレー装置30が、アルミ膜12の厚さV1より小さい粒径R1の第1銅粉末41を噴射することにより、アルミ膜12の表面に下地層21を形成する。第2工程では、コールドスプレー装置30が、第1銅粉末の粒径R1より大きく且つ下地層21の表面からアルミ膜12とシリコン層11との境界面までの寸法V2より小さい粒径R2の第2銅粉末42を噴射することにより下地層21に重ねて厚膜層22を形成する。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】 基板を薄くしてもその反りを防止するTSV構造の製造方法を提供する

【解決手段】本発明の半導体装置の製造方法は、半導体基板の表面に半導体素子を集積させて回路の少なくとも一部を形成する工程と、半導体基板の表面から穴を開ける工程と、穴の内表面に絶縁膜およびバリア膜を形成する工程と、バリア膜の表面に、穴を埋めるように導電性金属を形成する工程と、半導体基板の裏面を加工して厚さを減少させ、導電性金属を突出させる工程と、半導体基板の裏面にSiCN膜を設ける工程とを有する。

(もっと読む)

半導体装置およびその製造方法

【課題】ダマシン構造を有するCu配線において、バリア膜の拡散防止機能を低下させずにCu配線内のCuの埋め込み性を改善し、半導体装置の歩留まりおよび信頼性を向上する。

【解決手段】ダマシン配線を有する半導体装置において、第2層間絶縁膜6に形成した配線溝G2およびビアホールV2のそれぞれの内壁にバリア膜としてTaN膜7およびCuと濡れ性の良いTiからなるTi膜8とを順に形成することにより、Ti膜8上に均一にCuシード膜9aを形成することを可能とする。これにより、Cuシード膜9aを電極として電界メッキ法によりCu膜9を形成した際に、配線溝G2およびビアホールV2内に空隙が形成されることを防ぐ。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】半導体装置の信頼性を向上させる。

【解決手段】複数のゲート電極3bを覆うように窒化シリコン膜(第1絶縁膜)5を形成した後、オゾンTEOS膜(第1酸化シリコン膜)6、プラズマTEOS膜(第2酸化シリコン膜)を順次積層する。ここで、オゾンTEOS膜6を積層後、プラズマTEOS膜を積層する前に、窒化シリコン膜5をCMPストッパ膜として、CMP法により研磨する。これにより、プラズマTEOS膜の膜厚を均一化させることができるので、半導体装置の信頼性を向上させることができる。

(もっと読む)

シリコンデバイス構造、及びその形成に用いるスパッタリングターゲット材

【課題】シリコンデバイスの飽和移動度特性を向上する。

【解決手段】シリコン半導体膜上に、Pドープn+型アモルファスシリコン膜と、該Pドープn+型アモルファスシリコン膜上に形成された配線とを有するシリコンデバイス構造において、前記配線が、前記Pドープn+型アモルファスシリコン膜の表面に形成されたシリコン酸化膜と、銅合金膜とからなり、前記銅合金膜は、1原子%以上5原子%以下のMn及び0.05原子%以上1.0原子%以下のPを含む銅合金をスパッタリングにより形成した膜である。

(もっと読む)

固体撮像装置

【課題】 暗電流やリーク電流の発生を抑制することが可能な固体撮像装置を提供する。

【解決手段】 固体撮像装置は、光電変換素子が主面に配された第1基板と、導電体を含む第1の接合部を有する第1配線構造と、周辺回路の一部が主面に配された第2基板と、導電体を含む第2の接合部を有する第2配線構造と、を有する。そして、第1基板と、第1配線構造と、第2配線構造と、第2基板とがこの順に配置されるように第1の接合部及び第2の接合部とが接合されている。そして、第1の接合部の導電体と、第2の接合部の導電体とは、導電体に対する拡散防止膜で囲まれている。

(もっと読む)

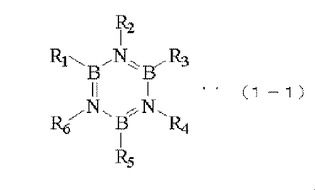

低誘電率材料形成用原料

【課題】 耐水性に優れた低誘電率材料を得る。

【解決手段】 化学式(1―1)

【化1】

で示されるボラジン系原料を有機溶媒に分散または溶解させたものを低誘電率材料形成用原料とする。式中のホウ素原子もしくは窒素原子が備える手が結合手となってボラジン環が結ばれたボラジン骨格系構造を形成し、上記ボラジン骨格系構造が繰り返されたオリゴマーまたはポリマーとして低誘電率材料を生成する。ただし式中、上記結合手以外のR1〜R6は、水素原子、炭素原子数1〜2のアルキル基の少なくともいずれかであって、少なくとも1つは水素原子ではなく、少なくとも1つは水素原子である。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】歩留まりに優れた構造を有する半導体装置およびその製造方法を提供する。

【解決手段】半導体装置は、基板と、基板上に形成されており、配線および絶縁層により構成された配線層が複数積層された多層配線層と、平面視において、基板内の記憶回路領域に形成されており、多層配線層内に埋め込まれた少なくとも1以上の容量素子および周辺回路を有する記憶回路と、平面視において、基板内の憶回路領域とは異なる領域である論理回路領域に形成された論理回路と、を備え、容量素子は、下部電極、容量絶縁膜、上部電極、埋設電極および、上部接続配線で構成されており、上部接続配線と埋設電極とは、同一の材料かつ一体に構成されており、上部接続配線と下部電極との間には、論理回路を構成する前記配線が少なくとも1以上設けられており、上部接続配線の上面と、上部接続配線と同じ配線層に形成された論理回路を構成する配線の上面とが、同一面を構成する。

(もっと読む)

回路基板及びその製造方法

【課題】配線抵抗が低く配線間の絶縁性の高い回路基板及びその製造方法を提供する。

【解決手段】基板上に、Cuを含む導電性材料の配線構造体を形成し、配線構造体の表面に、Cu−N結合を有する絶縁性の拡散防止膜を形成した後、拡散防止膜が形成された配線構造体を覆うように、絶縁膜を形成する。

(もっと読む)

半導体装置の製造方法

【課題】ポーラスLow−k膜の信頼性を向上させる。

【解決手段】プラズマCVD法によって層間絶縁膜IL2を形成する際にCVD装置内に供給するポロジェンの流量を、ポロジェンおよびメチルジエトキシシランの合計の流量の30%以上60%以下とすることで、層間絶縁膜IL2内に形成される空孔10の大きさを小さくし、プロセスダメージによって層間絶縁膜IL2の表面に変質層CLが形成されることを防ぐ。また、水分を含む変質層CLの形成を抑えることで、各配線を構成するバリア膜および主導体膜の酸化を防ぎ、各配線間の耐圧の劣化を防ぐ。これにより、層間絶縁膜IL2に隣接して形成される配線のEM寿命および前記配線の線間TDDB寿命の劣化を防ぐ。

(もっと読む)

半導体装置

【課題】ポーラスLow−k膜の信頼性を向上させる。

【解決手段】ポーラスLow−k膜からなる第2ファイン層の層間絶縁膜IL2内の空孔10および空孔11の平均径を1.0nm以上1.45nm未満とすることで、プロセスダメージによって層間絶縁膜IL2の表面に変質層CLが形成されることを防ぐ。また、水分を含む変質層CLの形成を抑えることで、各配線を構成するバリア膜および主導体膜の酸化を防ぎ、各配線間の耐圧の劣化を防ぐ。これにより、層間絶縁膜IL2に隣接して形成される配線のEM寿命および前記配線の線間TDDB寿命の劣化を防ぐ。

(もっと読む)

半導体装置とその製造方法

【課題】 相互接続配線とその上方のキャップ層との接着力を向上することが可能な半導体装置とその製造方法を提供する。

【解決手段】 半導体基板101上の誘電体層305中にその上面に自然酸化膜を含む金属の相互接続配線310を形成し、誘電体層及び前記金属の相互接続配線の少なくとも一部を覆いマンガン原子又はイオンを含む第1のキャップ層405を形成し、第1のキャップ層405上に絶縁体である第2のキャップ層410形成し、自然酸化膜及び第1のキャップ層は、第1のキャップ層と相互接続配線との間に酸化マンガンを形成するために反応する。

(もっと読む)

半導体装置の製造方法

【課題】ボイドとヒロックの発生の双方を抑制してCu配線を形成する。

【解決手段】半導体基板上の層間絶縁膜に溝パターンを形成する工程(S1)、めっき法によりCu膜を形成する工程(S2,S3)、130〜180℃で第1アニールを行う工程(S4)、CMPにより溝パターン以外の銅膜を除去する工程(S5)、300〜350℃でグレイン成長のための第2アニールを行う工程(S6)とを備える。

(もっと読む)

半導体集積回路及びその製造方法

【課題】金属層からなるガードリングで囲まれたトリミング素子形成領域のヒューズ上の保護膜の開口からヒューズ上の層間絶縁膜に浸入した水分等がガードリングに形成されたヒューズ引き出し電極用の開口を通ってデバイス形成領域に浸入することを防止する。

【解決手段】ヒューズ5aを取り囲む第1ガードリング30とその外側の第2ガードリング40に囲まれたヒューズ電極引き出し領域41を形成する。ヒューズ5aと連続し層間絶縁膜6とフィールド酸化膜4の間をヒューズ電極引き出し領域41まで延在するヒューズ電極5と、該ヒューズ電極5と接続する第1ヒューズ引き出し電極7cと、該第1ヒューズ引き出し電極7cと接続する第2ヒューズ引き出し電極9cとを形成し、該第2ヒューズ引き出し電極9cを層間絶縁膜8上に形成された第2ガードリング40を構成する第2電極の開口24を通してデバイス素子形成領域80に引き出す。

(もっと読む)

半導体装置及びその製造方法

【課題】抵抗変化素子を半導体装置に組み込む際の必要なフォトマスクを削減しても高密度化が可能な抵抗変化素子を搭載した半導体装置及びその製造方法を提供すること。

【解決手段】配線溝を有する層間絶縁膜14と、配線溝に埋め込まれた配線16aと、配線16aを含む層間絶縁膜14上に形成されるとともに、配線16aに通ずる下穴を有する層間絶縁膜18と、少なくとも下穴が配置された領域における配線16a上に形成されるとともに、抵抗が変化する抵抗変化膜19aと、下穴が配置された領域における抵抗変化膜19a上に形成されたバリアメタル20aと、下穴が配置された領域におけるバリアメタル20a上に形成されたプラグ21aと、を備え、抵抗変化素子5は、第1電極と第2電極との間に抵抗変化膜19aが介在した構成となっており、配線16aは、第1電極を兼ね、バリアメタル20aは、第2電極を兼ねる。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】上面にストラップ配線が形成された絶縁膜と、この絶縁膜の下面に形成された配線と間で剥離が生じることが抑制された半導体装置および半導体装置の製造方法を提供する。

【解決手段】本発明に係る半導体装置は、半導体基板SSと、半導体基板SS上に形成され、周辺配線P1および配線L2が形成された配線層LL1,LL2と、配線層LL2に形成され、配線L3を含む配線層LL3と、配線層LL3上に形成され、磁気記憶素子MRを含む配線層LL4とを備え、配線L1,L2上に形成された拡散防止膜NF1,NF2は、SiCN膜またはSiC膜から形成され、配線L3上に形成された拡散防止膜NF3は、SiNから形成される。

(もっと読む)

81 - 100 / 948

[ Back to top ]