Fターム[5F033XX28]の内容

半導体集積回路装置の内部配線 (234,551) | 目的、効果 (15,696) | 拡散、突き抜け防止 (992)

Fターム[5F033XX28]の下位に属するFターム

シリコンの拡散、突き抜け防止 (20)

アルミニウムの拡散、突き抜け防止 (24)

Fターム[5F033XX28]に分類される特許

121 - 140 / 948

半導体装置及びその製造方法

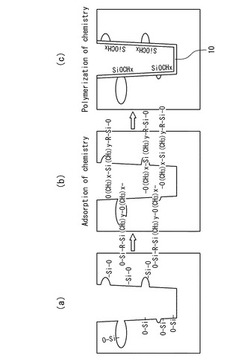

【課題】ポーラス絶縁層を用いた半導体装置において、当該ポーラス絶縁層を覆うポアシール絶縁層を良好に形成すること。

【解決手段】本発明に係る半導体装置の製造方法は、(A)ポーラス絶縁層の表面にトレンチを形成する工程と、(B)ビニル基を含み−Si−O−を含む構造を備える化学物質を、ポーラス絶縁層の表面上あるいはポーラス絶縁層中に導入する工程と、(C)当該化学物質の重合を行うことにより、ポーラス絶縁層よりも高密度のポアシール絶縁層をトレンチの表面上に形成する工程と、を含む。

(もっと読む)

マンガン含有低誘電率膜及びその製造方法、半導体装置の製造方法並びに成膜装置

【課題】マンガン含有材料を利用して、低誘電率膜への銅の拡散を防止する。

【解決手段】成膜装置100では、制御部70の制御に基づき、処理容器1内を真空にして、ヒーター6によりウエハWを加熱しつつ、シャワーヘッド11のガス吐出孔13a,13bからウエハWへ向けて低誘電率材料とマンガン含有材料とを含む成膜ガスを供給する。高周波電源23からシャワーヘッド11に高周波電力を供給することにより、成膜ガスを解離させ、処理容器1内に成膜ガスのプラズマを生成させる。このプラズマによって、ウエハWの表面にMnを含有するSiCOH膜を成膜する。

(もっと読む)

表示装置の作製方法

【課題】液滴吐出法により吐出する液滴の着弾精度を飛躍的に向上させ、微細でかつ精度の高いパターンを基板上に直接形成することを可能にする。もって、基板の大型化に対応できる配線、導電層及び表示装置の作製方法を提供することを課題とする。また、スループットや材料の利用効率を向上させた配線、導電層及び表示装置の作製方法を提供することを課題とする。

【解決手段】液滴吐出法による液滴の吐出直前に、所望のパターンに従い基板表面上の液滴着弾位置に荷電ビームを走査し、そのすぐ後に該荷電ビームと逆符号の電荷を液滴に帯電させて吐出することによって、液滴の着弾位置の制御性を格段に向上させる。

(もっと読む)

コンタクトプラグ、配線、半導体装置およびコンタクトプラグ形成方法

【課題】金属シリサイド膜と銅コンタクトプラグ本体との間の拡散バリア層として、薄膜の酸化マンガンで構成された拡散バリア層を用いてはいるものの、金属シリサイド膜への銅原子の拡散、侵入を確実に抑止することができるようにする。

【解決手段】本発明のコンタクトプラグ10は、半導体装置の絶縁膜4に設けられたコンタクトホール5に形成され、コンタクトホール5の底部に形成された金属シリサイド膜3と、コンタクトホール5内で金属シリサイド膜3上に形成され、非晶質でシリコンを含む第1の酸化マンガン膜6aと、その第1の酸化マンガン膜6a上に形成され、微結晶を含む非晶質の第2の酸化マンガン膜6bと、その第2の酸化マンガン膜6b上に、コンタクトホール5を埋め込むように形成された銅プラグ層7と、を備えることを特徴としている。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】素子の信頼性を劣化させることなく、より比誘電率の低い絶縁膜を形成する。

【解決手段】この半導体装置の製造方法は、下地膜101に、環状シロキサンをプラズマ重合させて第一の絶縁膜102を形成する工程と、第一の絶縁膜102を形成する工程の後、連続的に、第一の絶縁膜102上に、環状シロキサンをプラズマ重合させて第二の絶縁膜103を形成する工程と、を含む。第一の絶縁膜102の成膜速度は、第二の絶縁膜103の成膜速度よりも遅い。

(もっと読む)

半導体装置、及びその製造方法

【課題】配線の導通信頼性を損なうことなく、エアギャップを形成でき、配線間容量Cが低減した配線膜構造を有する半導体装置を提供することである。

【解決手段】 半導体装置の製造方法において、第1絶縁膜を形成する第1絶縁膜形成工程と、前記第1絶縁膜に配線膜を形成する配線膜形成工程と、前記配線膜が形成されてない箇所の前記第1絶縁膜にドライエッチングで溝を形成するドライエッチング工程と、前記ドライエッチング工程の後、前記溝が埋め尽くされることが無いよう、前記配線膜および前記溝上に第2絶縁膜を形成する第2絶縁膜形成工程とを具備する。

(もっと読む)

薄膜形成方法、表示板用金属配線、及びこれを含む薄膜トランジスタ表示板とその製造方法

【課題】接着層の厚さを増加させることなく、銅の下部層との接着性が向上し、銅が下部層に拡散することを防止することができる薄膜形成方法、表示板用金属配線、及びこれを含む薄膜トランジスタ表示板とその製造方法を提供する。

【解決手段】本発明の薄膜形成方法は、基板上にスパッタリング方法により薄膜を形成する方法であって、薄膜は、電力密度が1.5〜3W/cm2、非活性気体の圧力が0.2〜0.3Paで形成する。薄膜は、非晶質構造を有することができ、チタニウム、タンタル、又はモリブデンのうちのいずれか一つで形成することができる。

(もっと読む)

半導体装置の製造方法

【課題】配線間のショートを抑制すること。

【解決手段】半導体基板10上に第1絶縁膜20を形成する工程と、前記第1絶縁膜の上面を研磨する工程と、研磨された前記第1絶縁膜に接続30孔を形成する工程と、前記接続孔の内面および前記第1絶縁膜上に前記第1導電層32を形成する工程と、前記接続孔内の前記第1導電層上に第2導電層34を形成する工程と、前記第1絶縁膜上の前記第1導電層を研磨し前記第1絶縁膜の上面を露出させる工程と、前記第2導電層のエッチングレートより前記第1導電層のエッチングレートが大きいエッチャントを用い、前記接続孔内上部の前記第1導電層をエッチングする工程と、前記絶縁膜上に配線層50を形成する工程と、を含む半導体装置の製造方法。

(もっと読む)

半導体装置の製造方法

【目的】ウェット処理を行った場合でも絶縁膜上に庇形状が形成されない半導体装置の製造方法を提供する。

【構成】本発明の一態様の半導体装置の製造方法は、基板上に絶縁膜を形成する工程(S102)と、絶縁膜上に保護膜を形成する工程(S104)と、保護膜に第1の開口部を形成する工程(S114)と、第1の開口部内に保護膜よりもウェットエッチングレートが大きい犠牲膜を形成する工程(S116)と、第1の開口部内の犠牲膜に第1の開口部よりも幅の狭い第2の開口部を形成する工程(S122の一部)と、第2の開口部を転写することで絶縁膜に第3の開口部を形成する工程(S122の一部)と、第3の開口部が形成された後に、ウェット処理を行なう工程(S126)と、ウェット処理後に、第3の開口部内にバリアメタル膜を形成する工程(S128)と、第3の開口部内に導電性材料を埋め込む工程(S132)と、を備えたことを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】微細配線を有する半導体装置を高信頼性及び高歩留まりで得る。

【解決手段】この半導体装置の製造方法は、下層配線を形成する工程(ステップS101)と、下層配線上に絶縁膜を形成する工程(ステップS102)と、絶縁膜上にレジストを形成する工程(ステップS103)と、レジストをマスクとしてドライエッチングにより下層配線を露出する開口部を形成する工程(ステップS104)と、開口部を洗浄液を用いて洗浄する工程(ステップS105)と、洗浄した開口部をリンスする工程(ステップS106)と、含む。ステップS106では、リンス液と還元性ガスとを二流体ノズルから吐出して、開口部の底部をリンスする。

(もっと読む)

半導体装置とその製造方法、及び電子機器

【課題】寄生容量を低減し、高性能化を図った固体撮像装置等の半導体装置とその製造方法、前記固体撮像装置を備えたカメラ等の電子機器を提供するものである。

【解決手段】本発明の半導体装置は、2つ以上の半導体チプ部22,26が貼り合わされた積層半導体チップ27を有する。積層半導体チップ27では、少なくとも第1の半導体チップ部22に画素アレイ23と多層配線層41が形成され、第2の半導体チップ部26にロジック回路25と多層配線層55が形成される。第1の半導体チップ部22には、一部の半導体部分が全て除去された半導体除去領域52が形成され、半導体除去領域52内に第1の半導体チップ部22と第2の半導体チップ部26との間を接続する複数の接続配線67が形成される。この半導体装置は、裏面照射型の固体撮像装置として構成される。

(もっと読む)

半導体装置の製造方法

【課題】絶縁膜のストレスに耐え、絶縁膜からの酸素や水分の影響を抑制しつつ、エレクトロマイグレーションの耐性や配線間の耐圧も改善することが可能な半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法では、(a)凹部102が形成された絶縁膜101上に、TaN膜103を成膜する工程と、(b)TaN膜103上に、Taよりも熱膨張係数が大きいTiを主成分とするTi膜104を成膜する工程と、(c)Ti膜104上に、Tiよりも熱膨張係数が大きいCuを主成分とするCu膜105を成膜する工程と、(d)Cuを、電解めっきにより、凹部102内に埋め込む工程とを含む。

(もっと読む)

半導体装置

【課題】電極パッドからの水分の拡散を防止できると共に、絶縁膜の薄膜化及び低誘電率化に対応できるようにする。

【解決手段】半導体装置は、半導体基板11の上方に形成され、外部との電気的な接続を取る接続部25である電極パッドと、半導体基板と接続部との間に積層された絶縁膜14等にそれぞれ形成され、上層の配線34が接続部と接続された複数の第1配線層及び該第1配線層同士を接続するビア31よりなる積層構造体27と、複数の絶縁膜に積層構造体の周囲を隙間なく囲むように形成され、複数の第2配線層40等及び該第2配線層同士を線状に接続するラインビア41よりなるリング構造体28と、接続部と内部回路とを電気的に接続する引き出し配線32Aとを有している。積層構造体とリング構造体とは複数の第1配線層の少なくとも1つによって互いに接続されており、引き出し配線はリング構造体と接続されている。

(もっと読む)

半導体装置及びその製造方法

【課題】 半導体装置の銅配線の信頼性をTDDB寿命とEM寿命との双方に関して向上させる。

【解決手段】 半導体装置の配線層30は、配線溝が形成された絶縁膜32、35と、配線溝の内面に形成されたバリアメタル層41と、バリアメタル層41を介して配線溝内に形成された銅配線膜43とを有する。バリアメタル層41は、配線溝の内壁面側から順に形成された第1乃至第3のバリアメタル膜41−1、2、3を有する。第2のバリアメタル膜41−2は、第3のバリアメタル膜41−3側の表面部分において、クラスタイオン照射によって形成された、その他の部分より高い密度の緻密層41−2aを有する。第3のバリアメタル膜41−3は、例えばルテニウム等、銅配線膜43との密着性に優れた材料を有する。

(もっと読む)

半導体装置及びその製造方法

【課題】空孔を含む絶縁膜を用いる半導体装置及びその製造方法において、配線間耐圧を向上すると共に配線間容量を低減する。

【解決手段】半導体装置200の製造方法は、基板上に、単一層からなり且つ空孔形成材料202を含む絶縁膜203を形成する工程(a)と、絶縁膜203の表面部である第1領域210には空孔を形成することなく、絶縁膜203における第1領域210よりも下方の第2領域には空孔形成材料202の除去により空孔204を形成する工程(b)と、絶縁膜203に少なくとも1つの配線溝211を形成する工程(c)と、配線溝211を埋め込むように導電膜215を形成する工程(d)と、配線溝211からはみ出た余剰部分の導電膜215を除去することにより配線207を形成する工程(e)とを備える。

(もっと読む)

半導体装置の製造方法

【目的】Cu配線寿命の劣化と絶縁膜の絶縁性劣化を共に低減する半導体装置の製造方法を提供することを目的とする。

【構成】本発明の一態様の半導体装置の製造方法は、チャンバ内面にシリコン(Si)膜を表面層とする多層膜を形成する工程(S102)と、前記多層膜が内面に形成されたチャンバ内に、表面に銅(Cu)配線と絶縁膜とが形成された基板を配置して、希ガスプラズマ処理を行なう工程(S106)と、を備えたことを特徴とする。

(もっと読む)

導電性バリア膜形成材料、導電性バリア膜形成方法、及び配線膜形成方法

【課題】溝や穴の開口部と深さとの比(開口部/深さ)が1/5〜1/7のような条件を要求されても、又、厚さが10nm以下であっても成膜が可能で、かつ、銅の拡散防止(バリア性)に優れ、更には電気抵抗が小さく、銅膜との密着性にも優れた導電性バリア膜形成材料を提供する。

【解決手段】ケミカルベーパーデポジションにより銅膜の下地膜として導電性Ta−Zr系バリア膜を形成する為の材料であって、Taを持つ金属有機化合物と、Zrを持つ金属有機化合物とを含むことを特徴とする導電性バリア膜形成材料、および、前記Ta有機化合物、前記Zr有機化合物の一方または双方を溶解する溶媒とを含むことを特徴とする導電性バリア膜形成材料。

(もっと読む)

表示装置及び表示装置の製造方法

【課題】表示装置の薄膜トランジスタ基板において、水素プラズマ処理時の水素による影響を低減する。

【解決手段】非晶質ケイ素の膜により形成された非晶質ケイ素層上に形成される銅配線において、第1添加元素として水素化物の生成エネルギーが負の元素、さらに第2添加元素を含む銅を主成分とする合金により形成された銅合金層107Aと、前記銅合金層の上に純銅により形成された純銅層107Bとを有する薄膜トランジスタ基板を備える。

(もっと読む)

半導体装置の製造方法

【課題】半導体製造プロセスにおけるガスの流量制御は、マスフローコントローラによって行われている。ここで使用される流量調整バルブは、流量を調整することに重点が置かれているため、閉鎖時にも微小ながらガスが流出する。このため、流量調整バルブの出力側に閉鎖特性の良好な開閉バルブが挿入されている。しかし、流量調整バルブと開閉バルブ間の流路系には、一定の容量を有するため、流量調整バルブが閉鎖されている間に、この流路系の圧力が流量調整バルブのリークを介して、上昇するという問題がある。このような出力側バルブ間空間の圧力上昇は、次に、開閉バルブが開いたときに、ガス被供給系への余剰のガス供給の原因となる。

【解決手段】本願発明は、マスフローコントローラのガス排出側の流量制御バルブと開閉バルブ間の圧力を計測することで、流量制御バルブの閉鎖時のリークガス流量を検知する半導体装置の製造方法である。

(もっと読む)

半導体装置

【課題】動作速度が低下することを抑制することができる半導体装置を提供する。

【解決手段】半導体装置は、MOSトランジスタ9を有するシリコン基板5と、シリコン基板5上に形成され、配線および絶縁膜により構成された配線層が複数積層された多層配線層と、多層配線層内に埋め込まれた、下部電極(下部電極膜91)、容量絶縁膜92、および上部電極(上部電極膜93)を有しており、メモリ素子を構成する容量素子90と、を備え、容量素子90とMOSトランジスタ9との間にダマシン形状の銅配線(第2層配線25)が少なくとも1層以上形成され、1つの配線(第2層配線25)の上面と容量素子90の下面とが略同一平面上にあり、容量素子90上に銅配線(プレート線配線99)が少なくとも1層以上形成されている。

(もっと読む)

121 - 140 / 948

[ Back to top ]