Fターム[5F033XX28]の内容

半導体集積回路装置の内部配線 (234,551) | 目的、効果 (15,696) | 拡散、突き抜け防止 (992)

Fターム[5F033XX28]の下位に属するFターム

シリコンの拡散、突き抜け防止 (20)

アルミニウムの拡散、突き抜け防止 (24)

Fターム[5F033XX28]に分類される特許

201 - 220 / 948

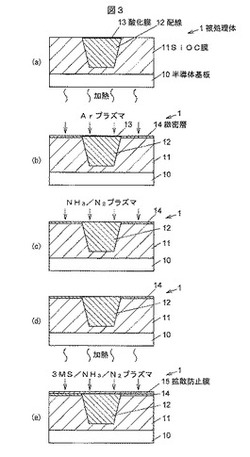

半導体装置の製造方法

【課題】配線表面の酸化膜を除去する際の低誘電率絶縁膜の変質を抑える半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、半導体基板10上のSiOC膜11表面に配線12を形成する工程と、配線12が表面に形成されたSiOC膜11を希ガス、又は希ガスとN2ガスの混合ガスを含むプラズマに曝してSiOC膜11表面に緻密層14を形成する工程と、緻密層14が形成された後に、配線12の表面に形成された酸化膜13を除去する工程と、酸化膜13が除去された配線12、及び緻密層14上に絶縁膜としての拡散防止膜15を形成する工程と、を含み、酸化膜13を除去する工程から拡散防止膜15を形成する工程までが、大気に暴露されることなく行われる。

(もっと読む)

半導体装置及びその製造方法

【課題】電極パッドの損傷を抑制することができる半導体装置を提供する。

【解決手段】半導体基板11と、半導体基板11の上方に形成された電極パッド30とを有し、電極パッド30は、第1の融点温度を有する材料からなる第1の層32と、第1の層32上に位置するとともに外に向けて表出し、第1の融点温度よりも高い第2の融点温度を有する材料からなる第2の層33とを含むことを特徴とする。これにより、外部から電極パッド30への圧力により第1の層32に達する傷ができても、必要に応じて第1の融点以上の温度で加熱することにより電極パッド表面の平坦性を修復することができる。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体基板に素子と貫通電極とが形成された半導体装置の製造方法において、貫通電極からの銅による素子の汚染を防止できる方法を提供する。

【解決手段】半導体基板10と、それに形成された素子ZDと、半導体基板10を貫通するスルーホールTHと、半導体基板10の両面側及びスルーホールTHの内面に形成されて、素子ZDを被覆する絶縁層12とを備えた構造体を用意する工程と、スルーホールTH内に貫通電極20を形成する工程と、貫通電極20を被覆する第1バリア金属層30aを形成する工程と、素子ZDの接続部に到達するコンタクトホールCH1を形成する工程と、コンタクトホールCH1内の素子ZDの接続部の自然酸化膜を除去する工程と、第1バリア金属層30aを利用して、貫通電極20に接続される第1配線層40と、コンタクトホールCH1を通して素子ZDの接続部に接続される第2配線層40aとを形成する工程とを含む。

(もっと読む)

半導体装置およびその製造方法

【課題】製造プロセス中に磁性体膜の材料の拡散を防止しながら、高い磁気シールド効果を有するヘテロ構造磁気シールドを備えた半導体装置を提供する。

【解決手段】半導体装置10は、半導体基板20、半導体基板20の主面上に形成され、かつ多層配線層11Bを含む半導体素子12、および半導体素子12を被覆するヘテロ構造磁気シールド170を含む。ヘテロ構造磁気シールド170は、第一の磁気シールド積層構造16Aと磁気シールド積層構造16Aを覆う第二の磁気シールド積層構造16Bを含む。第一および第二の磁気シールド積層構造16Aおよび16Bは、いずれも、半導体素子12を被覆する磁性体からなる磁気シールド膜および半導体素子12と磁気シールド膜との間に介在し磁性体の拡散を防止するバッファ膜とを有する。

(もっと読む)

半導体装置およびその製造方法

【課題】新たな工程を追加することなく信頼性の高い半導体装置およびその製造方法を提供すること。

【解決手段】半導体素子を表面側に有する基板11と、半導体素子を覆うように基板11に積層された第1絶縁膜12と、第1絶縁膜12を厚さ方向に貫通する貫通孔の内面に積層されたバリア導電層13を介して貫通孔内に埋め込まれたコンタクトプラグ14と、第1絶縁膜12の表面に形成されてコンタクトプラグ14を介して半導体素子と電気的に接続された1種類以上の機能層とを備え、前記機能層は、バリア導電層13の材料と同じ材料からなり第1絶縁膜12の表面の所定領域に積層された第1バリア導電層13と、第1バリア導電層13上に、直接積層されるか、または第2絶縁膜15を介して積層されるか、またはそれらの両方の形態で積層された第2バリア導電層16と、第2バリア導電層16に積層された導電層17とを有してなることを特徴とする半導体装置。

(もっと読む)

半導体装置及びその製造方法

【課題】絶縁膜の表面に対するダメージを防ぎ、配線膜厚を均一に制御することにより、配線間ショート及び信頼性劣化を防止できるようにする。

【解決手段】半導体基板101の上に絶縁膜102を形成し、絶縁膜102の内部にイオン注入法によりイオン注入層103を形成し、絶縁膜102に少なくともイオン注入層103に達する深さの配線溝104を形成し、配線溝104に導電膜107Aを形成し、絶縁膜102及び導電膜107Aにおけるイオン注入層103よりも上に形成されている領域を除去する。

(もっと読む)

半導体装置及びその製造方法

【課題】配線の埋め込み不良及び配線抵抗の上昇を抑えると共に、信頼性を向上した半導体装置を実現できるようにする。

【解決手段】半導体装置は、基板101の上に形成された絶縁膜105と、絶縁膜105中に形成された、銅を含む材料からなる埋め込み配線115とを備えている。絶縁膜105と埋め込み配線115との間には、白金族元素を含む材料からなるバリア膜110が形成されている。絶縁膜105とバリア膜110との間には、絶縁膜105よりも密度が高い高密度絶縁膜109が形成されている。

(もっと読む)

窒素含有前駆物質を用いる誘電体バリアの堆積

【課題】現行のバリア誘電体膜に匹敵するかそれよりも低い誘電率を有する誘電体膜を得る方法を提供する。

【解決手段】集積回路基板の誘電体膜と金属相互接続との間に、炭窒化ケイ素バリア誘電体膜を形成する方法であって、誘電体膜を有する集積回路基板を提供すること、この基板をRxR’y(NR”R”’)zSiを含むバリア誘電体膜の前駆物質と接触させること(R、R’、R”及びR”’はそれぞれ個々に、水素、直鎖若しくは分岐の飽和若しくは不飽和アルキル、又は芳香族から選択され;x+y+z=4;z=1〜3であるが、R及びR’の両方が同時に水素にはならない);及び集積回路基板上でC/Si比0.8超かつN/Si比0.2超の炭窒化ケイ素バリア誘電体膜を形成することを含む方法。

(もっと読む)

半導体構造体及びその形成方法

【課題】 相互接続構造の信頼性及び拡張性を改善する相互接続構造のための冗長金属拡散バリア層を提供する。

【解決手段】 冗長金属拡散バリア層は、誘電体材料内に設けられた開口内に配置され、且つ開口内に存在する拡散バリア層及び導電性材料の間に配置される。冗長拡散バリア層は、Ru並びに純粋なCo若しくはN,B及びPのうちの少なくとも1つを含むCo合金からなる単層若しくは多層構造である。

(もっと読む)

半導体装置

【課題】電極部と貫通電極層の間の抵抗値ばらつきに依存しない信頼性に優れた半導体装置を提供する。

【解決手段】半導体基板表面2aの第1絶縁膜8の中に、外部接続端子を有する電極部18が形成され、基板をビアホール10が貫通し、ビアホール側壁10a及び基板裏面の第2絶縁膜12とビアホール底面の第1絶縁膜とに貫通電極層11が形成され、電極部と貫通電極層との間にシリサイド層9を接続形成し、ビアホール中心軸を含む平面で切断された断面において、シリサイド層の幅A≦ビアホール底部の幅Bである。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】第2絶縁層にビアとなる接続孔を形成するときにビアと配線の間に位置ずれが生じても、エアギャップとビアが繋がることを抑制できるようにする。

【解決手段】配線162は第1絶縁層120に埋め込まれており、上面が第1絶縁層120の上面より高い。エアギャップ128は、配線162と第1絶縁層120の間に位置している。エッチングストッパー膜200は、第1絶縁層120上、エアギャップ128上、及び配線162上に形成されている。第2絶縁層220はエッチングストッパー膜200上に形成されている。ビア262は第2絶縁層220に埋め込まれており、配線162に接続している。そしてエッチングストッパー膜200は、エアギャップ128上に位置する部分202が、配線162上に位置する部分より厚い。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】ビアと配線の間に位置ずれが生じても、エアギャップとビアが繋がることを抑制できるようにする。

【解決手段】配線162は第1絶縁層120に埋め込まれており、上面が第1絶縁層120の上面より高い。エアギャップ128は、配線162と第1絶縁層120の間に位置している。第2絶縁層200は、少なくとも第1絶縁層120上及びエアギャップ128上に形成されている。本図に示す例では、第2絶縁層200は配線162を被覆していない。エッチングストッパー膜210は、少なくとも第2絶縁層200上に形成されている。本図に示す例では、エッチングストッパー膜210は、第2絶縁層200上及び配線162上に形成されている。第3絶縁層220はエッチングストッパー膜210上に形成されている。ビア262は第3絶縁層220に埋め込まれており、配線162に接続している。

(もっと読む)

小臨界次元の接点装置及び相互接続子用の超薄低抵抗タングステンフィルムの堆積方法

【課題】高縦横比の特徴部のボイドなしの充填方法を提供する。

【解決手段】種々の実施例に於いて、この方法は低温化学蒸着工程によるタングステンでの特徴部の充填に関する。或る実施例に於いて、工程温度は特徴部充填の化学蒸着の間約350°C以下に維持される。この低温化学蒸着タングステン充填により、標準の化学蒸着充填と同様は薄膜抵抗を達成する一方、高縦横比の特徴部への向上された充填と下地層へとのフッ素移動への向上されたバリヤが得られる。発明は更に低抵抗を有するタングステンフィルムの堆積方法に関する。種々の実施例に於いて、この方法ではタングステンバルク層の堆積及び/或は低温化学蒸着によるバルク層の堆積の前に堆積された核形成層に低温低抵抗処理を実施し、その後高温化学蒸着を実施する。

(もっと読む)

スパッタリングターゲット

【課題】 平面表示装置等の配線膜のプロセス温度域で、低抵抗化が可能であるとともに、ガラス基板やSi層への密着性が良好で、かつSi拡散バリア性を有するCu系配線膜を形成するために使用されるスパッタリングターゲットを提供する。

【解決手段】 Cuと添加元素と酸素の総和を100原子%とした時に、添加元素としてBを0.1〜1.0原子%、さらにBと化合物を発現する元素の少なくとも1種類以上を0.1〜2.0原子%含むとともに、酸素を3.0〜10原子%含有し、残部がCuと不可避的不純物からなるスパッタリングターゲットである。

(もっと読む)

半導体装置およびその製造方法

【課題】層間絶縁膜を貫通するように形成した下部電極の外壁を露出する際、湿式エッチングに用いる薬液が下部電極の下層に浸透し、浸透した薬液により半導体装置がダメージを受けやすいという課題があった。

【解決手段】層間絶縁膜2上に、湿式エッチングに耐性を備えたエッチング防止膜5、第一の絶縁膜6、該第一の絶縁膜6より前記湿式エッチングの速度が大きい第二の絶縁膜7をこの順で設ける成膜工程と、エッチング防止膜5、第一の絶縁膜6および第二の絶縁膜7を貫通する開口部8を形成する開口工程と、開口部8にキャパシタの下部電極10を設ける下部電極形成工程と、第二の絶縁膜7を前記湿式エッチングで除去し下部電極10を露出する除去工程とを有することを特徴とする。

(もっと読む)

配線構造、薄膜トランジスタ基板およびその製造方法、並びに表示装置

【課題】純CuまたはCu合金のCu系合金配線と半導体層との間のバリアメタル層を省略することが可能なダイレクトコンタクト技術であって、幅広いプロセスマージンの範囲においてCu系合金配線を半導体層に直接かつ確実に接続することができる技術を提供する。

【解決手段】本発明の配線構造は、基板の上に、基板側から順に、半導体層と、純CuまたはCu合金のCu系合金膜とを備えた配線構造であって、前記半導体層と前記Cu系合金膜との間に、基板側から順に、窒素、炭素、フッ素、および酸素よりなる群から選択される少なくとも一種の元素を含有する(N、C、F、O)層と、CuおよびSiを含むCu−Si拡散層との積層構造を含んでおり、且つ、前記(N、C、F、O)層を構成する窒素、炭素、フッ素、および酸素のいずれかの元素は、前記半導体層のSiと結合している。

(もっと読む)

半導体装置の製造方法

【課題】本発明は多層配線構造を有する半導体装置の製造方法に関し、高い集積度が要求される場合に優れた歩留まりと高い信頼性とを確保することを目的とする。

【解決手段】トランジスタのソースドレイン領域の上層にシリコン酸化膜7を形成する。一端面がソースドレイン領域6に導通し、他端面がシリコン酸化膜7の表面に露出するように、シリコン酸化膜7の内部に導電性のパッド10を設ける。シリコン酸化膜7およびパッド10の上層にシリコン酸化膜11を形成する。一端面がパッド10に接触し、他端面が配線層14と導通するようにシリコン酸化膜11の内部にプラグとして機能する導電層を設ける。シリコン酸化膜7の表面と、パッド10の他端面は平滑な同一平面を形成する。プラグとして機能する導電層は、パッド10に比して小さく、かつ、パッド10の中央部近傍に接触するように形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体基板に素子と貫通電極とが形成された半導体装置の製造方法において、貫通電極からの銅による素子の汚染を防止できる方法を提供する。

【解決手段】半導体基板10と、それに形成された素子ZDと、半導体基板10を貫通するスルーホールTHと、半導体基板10の両面側及びスルーホールTHの内面に形成されて、素子ZDを被覆する絶縁層12とを備えた構造体を用意する工程と、スルーホールTH内に貫通電極20を形成する工程と、貫通電極20を被覆する第1バリア金属パターン層30を形成する工程と、絶縁層12に、素子ZDの接続部に到達するコンタクトホールCHを形成する工程と、コンタクトホールCH内の素子ZDの接続部の自然酸化膜を除去する工程と、第1バリア金属パターン層30に接続されると共に、コンタクトホールCHを通して素子ZDに接続される配線層40,40aを形成する工程とを含む。

(もっと読む)

半導体素子の製造方法

【課題】柱状残渣の発生を抑制した半導体素子の製造方法の提供。

【解決手段】基板12上に配線層14を形成する工程と、基板12および配線層14を覆うように、第3絶縁膜22、第2絶縁膜(SiN膜)24、および第1絶縁膜(PSG膜)26を順に積層した層間絶縁層20を形成する工程と、第1絶縁膜26上にマスクパターンを形成する工程、ウェットエッチング処理によって第1絶縁膜26のコンタクトホール30形成部分を除去する工程、少なくとも等方性ドライエッチングを含むエッチング処理によって第2絶縁膜24のコンタクトホール30形成部分を除去する工程、およびエッチング処理によって第3絶縁膜22のコンタクトホール30形成部分を除去する工程、を経て配線層14表面が露出するよう層間絶縁層20にコンタクトホール30を形成する工程と、を有する半導体素子10の製造方法。

(もっと読む)

信頼性向上のためのケイ化銅パッシベーション

【課題】その表面をケイ化銅に転化することにより、銅相互接続構造の露出銅表面を直接不動態化するための方法を提供すること。

【解決手段】その後の誘電体フィルムの形成とともに原位置に実行されるシラン・パッシベーション・プロセスは、Cu相互接続構造の露出したCu表面をケイ化銅に転化する。ケイ化銅は、Cu拡散およびエレクトロマイグレーションを抑制し、後続導体材料との接触が行われる領域内でバリア材として機能する。銅相互接続構造の銅表面全体をケイ化する場合もあれば、銅表面の一部分を露出するように上に重なる誘電体に開口部を形成した後で表面の局部部分をケイ化する場合もある。

(もっと読む)

201 - 220 / 948

[ Back to top ]