Fターム[5F038AC05]の内容

半導体集積回路 (75,215) | キャパシタ (4,915) | 構造 (2,824) | 電極領域又は電極部分 (2,206) | 多結晶電極、金属電極 (1,364)

Fターム[5F038AC05]に分類される特許

121 - 140 / 1,364

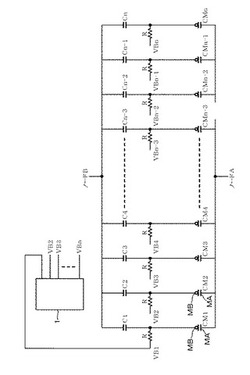

電圧制御可変容量及び電圧制御発振器

【課題】集積回路上に構成可能で、容量可変比率が大きくかつQ値が高く、VCOを構成した時に直線性の高い制御電圧と発振周波数の関係を実現する電圧可変型容量を提供すること。

【解決手段】下部電極を共通接続した複数のMOS型容量素子(CM1〜CMn)と、該複数のMOS型容量素子の上部電極に一端を接続し、他端を共通接続する同数の非電圧可変型容量(C1〜Cn)と、これらのMOS型容量素子と非電圧可変型容量の接続点に夫々異なる固定バイアス電圧を与える手段(VB1〜VBn及び抵抗)により構成され、前記複数のMOS型容量の共通接続された下部電極に制御電圧を加える。

(もっと読む)

アッド‐オン層形成方法

【課題】多くの半導体装置に必要な低温処理と両立しない高温操作を必要とするような欠点がない、堆積可能なアッド‐オン層形成方法を提供することを目的とする。

【解決手段】堆積可能なアッド‐オン層形成方法であって、第一半導体基板の取り外し層の形成、取り外し層の上の第一半導体基板に多くのドーピング領域の形成、ここで多くのドーピング層の形成は、第一電導型を有するように、ドーピングされ、取り外し層の上の第一半導体基板の第一ドーピング層の形成、第一電導型に対する第二電導型を有するようにドーピングされ、第一ドーピング層の上の第一半導体基板に最低中間ドーピング層の形成、及び中間ドーピング層上の第一半導体基板に最低第三ドーピング層の形成からなり、第三ドーピング層上に第一の電導性ブランケット層の形成、第一電導ブランケット層上に第二の電導性ブランケット層の形成、及び第二電導性ブランケット層が第二半導体基板の対応する電導性上部層と接触するように、第一半導体基板を第二半導体基板への取り付け、からなる。

(もっと読む)

半導体装置およびバイパスキャパシタモジュール

【課題】バイパスキャパシタは、半導体基板上に形成される半導体装置と一体化されて形成されているが、半導体装置の製造工程が複雑になると言う欠点がある。

【解決手段】バイパスキャパシタをシート状にモジュール化して、半導体装置に対して外付けできるように構成されたバイパスキャパシタモジュールが得られる。

(もっと読む)

キャパシタ装置及びその製造方法

【課題】本発明は、大容量化及び小面積化の要請に応えつつ、電圧依存性の低いキャパシタ装置及びその製造方法を提供することを目的とする。

【解決手段】シリコン31、32からなる下部電極30上に、容量絶縁膜40と上部電極50が順次積層形成されたキャパシタ装置であって、

前記下部電極は、互いに導電極性の異なるN型領域20とP型領域10とが所定比率で混在配置されているとともに、前記N型領域の表面が前記P型領域の表面よりも窪んだ凹凸構造を有することを特徴とする。

(もっと読む)

化合物半導体装置

【課題】容量耐性を高めると共に信頼性の向上を図った容量付PDを提供する。

【解決手段】PD、ダイオードを含む素子と複数のMIM容量を基板上に集積した化合物半導体装置において、前記素子からの引き出し配線とMIM容量の下部配線を結ぶ線を第1配線、MIM容量の上部電極とボンディングパッドを結ぶ線を第2配線としたときに前記第1配線と第2配線をスルーホールで接続し、MIM容量に印加する電圧方向を1方向に揃えるように、MIM容量の上下メタルに電圧を印加した。

(もっと読む)

誘電体薄膜形成用組成物、誘電体薄膜の形成方法及び該方法により形成された誘電体薄膜

【課題】薄膜キャパシタ等において、チューナビリティ、リーク電流特性及び誘電率を向上させ得る誘電体薄膜形成用組成物、誘電体薄膜の形成方法及び誘電体薄膜を提供する。

【解決手段】一般式:Ba1-xSrxTiyO3(式中0.2<x<0.6、0.9<y<1.1)で示される複合金属酸化物Aに、Cu(銅)を含む複合酸化物Bが混合した混合複合金属酸化物の形態をとる薄膜を形成するための液状組成物であり、複合金属酸化物Aを構成するための原料及び複合酸化物Bを構成するための原料が上記一般式で示される金属原子比を与えるような割合で、かつAとBとのモル比B/Aが0.001≦B/A<0.15の範囲内となるように、有機溶媒中に溶解している有機金属化合物溶液からなることを特徴とする。

(もっと読む)

半導体装置およびその製造方法

【課題】より低コストで、より信頼性の高いMIMキャパシタを有する、より信頼性の高い半導体装置、およびその製造方法を提供する。

【解決手段】本製造方法は、半導体基板SUBを準備する工程と、半導体基板SUBの一方の主表面上に、アルミニウム層AC1を有する第1の金属電極LEL1と、第1の金属電極LEL1上の誘電体層DECと、誘電体層DEC上の第2の金属電極UELとを形成する工程とを備える。第1の金属電極LEL1を形成する工程においては、表面がRmax<80nm、Rms<10nm、Ra<9nmの関係を満たすように、アルミニウム層AC1が形成される。第1の金属電極LEL1を形成する工程には、少なくとも1層の第1のバリア層T1を形成する工程と、第1のバリア層T1上に、アルミニウム層AC1を形成する工程と、アルミニウム層AC1を構成する結晶を再結晶化する工程とを含んでいる。

(もっと読む)

半導体装置

【課題】補償容量素子を構成する容量絶縁膜が破壊されることのない半導体装置を提供する。

【解決手段】第1の電圧が供給される第1の電源端子29と、第2の電圧が供給される第2の電源端子23と、容量絶縁膜42と該容量絶縁膜42を挟んで形成される第1及び第2電極とを其々備えており、前記第1及び第2の電源端子間に直列に設けられる複数の補償容量素子4と、奇数番目の前記補償容量素子4と次の偶数番目の前記補償容量素子4とを各々接続する第1の配線層に形成された第1の容量接続配線と、偶数番目の前記補償容量素子4と次の奇数番目の前記補償容量素子4とを各々接続する第2の配線層に形成された第2の容量接続配線と、前記第1及び第2の容量接続配線のいずれか一方に隣接して設けられ、実質的に固定された電圧が供給されるシールド配線5と、を備える。

(もっと読む)

キャパシタ装置及びその製造方法

【課題】キャパシタ装置及びその製造方法を提供する。

【解決手段】本発明に係るキャパシタ装置10は、第1導電型を有して第1電圧が印加される第1ウェル105及び第2導電型を有して第2電圧が印加される第2ウェル110を有する基板100、及び第1または第2ウェル105,110と絶縁されるように第1または第2ウェル105,110の上部に配されたゲート電極126を含み、キャパシタ装置10のキャパシタンスは、第1ウェル105と第2ウェル110との間の第1キャパシタンス及び第1または第2ウェル105,110とゲート電極126との間の第2キャパシタンスを含む。

(もっと読む)

薄膜キャパシタの製造方法及び該方法により得られた薄膜キャパシタ

【課題】薄膜キャパシタにおける諸特性低下の原因となるヒロックを抑制し、リーク電流特性及び絶縁耐圧特性に優れた薄膜キャパシタを製造する。

【解決手段】下部電極を形成した後、300℃よりも高い温度のアニール処理を行わずに薄膜形成前駆体溶液を下部電極上に塗布し、乾燥は室温〜450℃の範囲内の所定の温度で行い、焼成は乾燥温度よりも高い450〜800℃の範囲内の所定の温度で行い、塗布から焼成までの工程は塗布から焼成までの工程を1回又は2回以上行うか或いは塗布から乾燥までの工程を2回以上行った後、焼成を1回行い、初回の焼成後に形成される誘電体薄膜の厚さは20〜600nmにする。下部電極の厚さと初回の焼成後に形成される誘電体薄膜の厚さの比(下部電極の厚さ/誘電体薄膜の厚さ)は0.10〜15.0の範囲とするのが好ましい。

(もっと読む)

スイッチ回路装置

【課題】従来技術によるスイッチ回路装置では、ドライバ回路がアンテナ端子とポートとの間に振幅の大きい高周波信号を入力した際に、ドライバ回路内部でリーク電流が発生し、スイッチ回路装置の消費電力が増大する、という問題がある。

【解決手段】ドライバ回路の出力部に、リーク電流抑制回路部を設ける。本発明のスイッチ回路装置によれば、リーク電流抑制回路部が高周波信号の侵入を抑制するので、ドライバ回路は出力状態を保持することが出来て、リーク電流の問題が解決される。

(もっと読む)

半導体装置の製造方法

【課題】エッチング装置の経時変化や状態変化等によらずトレンチの深さのばらつきを低減することができる半導体装置の製造方法を得る。

【解決手段】まず、所望の深さよりも浅い深さを持つトレンチ16をSi基板10の主面に形成する。次に、トレンチ16の深さを測定する。トレンチ16の底面からSi基板10に酸素イオン18を注入する。この際に、測定したトレンチ16の深さと所望の深さの差に基づいて酸素イオン18の注入エネルギーを調整して、Si基板10の所望の深さに酸素イオン18が注入されるようにする。次に、熱処理を行って酸素イオン18を注入した位置にSiO2膜22を形成する。次に、SiO2膜22をエッチングストッパとして用いて、トレンチ16の底面からSi基板10を更にエッチングしてトレンチ24を形成する。その後、SiO2膜22を除去する。

(もっと読む)

半導体装置

【課題】キャパシタを形成する領域の占有面積を縮小する。

【解決手段】本実施形態の半導体装置は、半導体基板10内に設けられた半導体領域AACと、半導体領域AAC内に設けられる複数のキャパシタCm,Cnを含むキャパシタ群と、を具備し、キャパシタCm,Cnのそれぞれは、半導体領域AAC上のキャパシタ絶縁膜42Aと、キャパシタ絶縁膜42A上のキャパシタ電極34Am,34Amと、キャパシタ電極34Am,34Amに隣接する拡散層32Aとを有し、を有し、キャパシタ電極34Am,34Anに接続される配線29m,29nのそれぞれは、キャパシタCm,Cn毎に電気的に分離され、キャパシタ電極Cm,Cnのそれぞれに異なる電位Vm,Vnが印加されている。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の製造方法において、半導体装置の小型化を図ること。

【解決手段】第1の領域IにフラッシュメモリセルFLを形成する工程と、第2の領域IIにキャパシタQの第1の電極11aを形成する工程と、第2の絶縁膜14として第1の酸化シリコン膜14a、窒化シリコン膜14b、及び第2の酸化シリコン膜14cをこの順に形成する工程と、第1の電極11aの一部領域CRにおける窒化シリコン膜14bと第2の酸化シリコン膜14cとを除去する工程と、第3の領域IIIHにおける第1の絶縁膜10と第2の絶縁膜14とをウエットエッチングする工程と、キャパシタQの第2の電極30aを形成する工程と、一部領域CRにおける第1の酸化シリコン膜14aをエッチングして除去する工程とを有する半導体装置の製造方法による。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】多層配線層の層間における剥離の有無を簡便な手法で検出できるようにする。

【解決手段】第1電極412は多層配線層20に形成されている。第2電極422は、絶縁膜22の一部を介して第1電極412と対向している。第1電極パッド430は第1電極412に接続している。第2電極パッド432は第2電極422に接続している。そして少なくとも2層以上の絶縁膜22のそれぞれが、第1電極412及び第2電極422に挟まれている。そして第1電極412及び第2電極422により、センサ40の少なくとも一部が形成されている。センサ40は、多層配線層20の層間における剥離の有無を検出するために用いられる。

(もっと読む)

高電圧動作電界効果トランジスタとそのバイアス回路およびその高電圧動作回路要素

【課題】 ICまたはLSIの標準電源電圧用のトランジスタ構成部分ないしはプロセス技術を活用して高電圧動作電界効果トランジスタを該IC中に作りこむ。

【解決手段】 電界効果トランジスタの動作電圧を大きくするために、ゲートにドレイン電位に応じて変化する電位分布を設ける手段をとる。

(もっと読む)

MEMS装置

【課題】基板とMEMS素子との間の寄生容量、および基板の反りを抑えたMEMS装置を提供する。

【解決手段】

実施の形態のMEMS装置は、表面に開口する凹部と凹部内に、絶縁物、エアギャップ、または絶縁物およびエアギャップが形成された基板と、基板上の絶縁層と、絶縁層上に形成された信号線を有するMEMS素子とを有し、上記基板の表面に平行な方向の信号線の位置と上記平行な方向の凹部の位置に重なりがある。

(もっと読む)

チャージポンプ回路、不揮発性メモリ、データ処理装置、及びマイクロコンピュータ応用システム

【課題】複数の容量を互いに直列接続して一つの昇圧容量を形成した場合の中間ノードの帯電に起因するデバイス破壊を回避するとともに、当該中間ノードのリークパスを介して流れるリーク電流に起因するポンプ効率の低下を回避する。

【解決手段】チャージポンプ回路(1307)は、第1静電容量(Ca)とそれに直列接続された第2静電容量(Cb)とを含む昇圧容量(C(x−1),Cx)と、容量ドライバ(DRV(x−1),DRVx)と、保護回路(D1,D2)とを含む。上記保護回路は、上記昇圧電圧が形成されない状態においては導通状態とされて、上記第1静電容量と上記第2静電容量との直列接続ノードの蓄積電荷を放電し、上記昇圧電圧が形成される状態においては非導通状態を維持する。これにより、昇圧容量の耐圧緩和を図り、また、ポンプ効率の低下を回避する。

(もっと読む)

半導体装置

【課題】容量素子の単位面積当たりの容量を増加させる。

【解決手段】複数の第1電極110は互いに離間している。第2電極120は複数の第1電極110と同一の第1配線層102に位置している。図3に示すように複数の第1電極110は、第1の六角形の各頂点及び中心に、それぞれの中心が重なるように配置されており、第2電極120は、複数の第1電極110それぞれの全周に対向している。第1の六角形は、同一形状の2つの二等辺三角形を、底辺が互いに対向する向きに配置することにより、6つの頂点の位置が定められている。

(もっと読む)

半導体集積回路装置

【課題】デジタル回路からアナログ回路へのノイズの混入を十分に抑圧する半導体集積回路装置を提供することを目的とする。

【解決手段】デジタル回路を形成するデジタル回路領域13と、アナログ回路を形成するアナログ回路領域12とに分離し、アナログ回路領域を、アナログ回路の能動素子を形成する能動素子領域12aと、アナログ回路の受動素子を形成する受動素子領域12b,12cとに分離し、受動素子領域12b,12cをデジタル回路領域13と隣り合う領域に配置し、能動素子領域12aをデジタル回路領域13から離れた領域に配置した半導体集積回路装置において、受動素子領域12b,12cの半導体基板20に半導体基板の導電型と異なる第1導電型の第1ウェル21を形成し、第1ウェル21内に第1ウェルの第1導電型と異なる第2導電型の第2ウェル22を形成し、第2ウェル22上に素子分離膜23を介在させて受動素子を配設した。

(もっと読む)

121 - 140 / 1,364

[ Back to top ]